Изобретение относится к цифровым следящим системам с элементами -самонастройки, используемым в вычислительных устройствах обработки информации, представленной, например, в бинарной форме.

Известны вычислительные устройства для регулятора времеикой задержки электрического сигнала сложной формы, в которых сигнал управления величиной задержки формируется непосредстзенно из сигнала, несущего полезную информацию.

Однако эти устройства сложны (хотя в них рационально использовано входное отношение сигнала к шуму), что снижает их надежность. Кроме того, сложность связей приводит к понижению качества регулирования, в частности к ухудшению точности управления задержкой, что обусловлено влиянием дрейфа и нестабильности отдельных элементов схемы.

Предложенное устройство отличается от известных тем, что в нем между входом устройства и блоком обработки информации установлены соединенные последовательно второй канальный перемножитель, интегратор и схема совпадения, цркчем выходы обеих схем совпадения подключены ко входам обш,его перемножителя, к выходу генератора тактовых импульсов подключен аналоговый сумматор, второй вход которого подключен к первому через линию задержки, а .выход аналогового сумматора подключен ко второму входу сумматора по модулю два, выход которого подключен ко входу второго канального перемножителя.

Это повышает качество обработки инфорлгации и упрощает устройство.

Устройство позволяет также повысить качество управления объектом регулирования, осуществляемого блоком обработки информации.

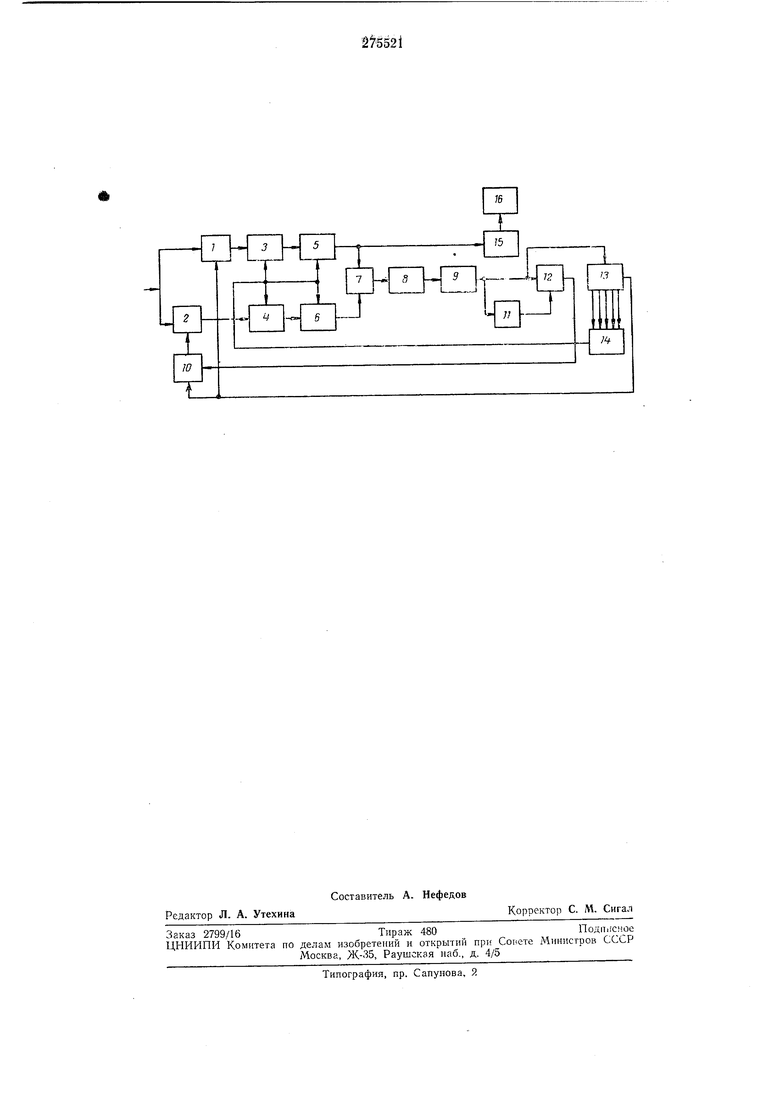

На чертеже дана блок-схема предложенного устройства..

Она содерлчит канальные перемножители / и 2, интеграторы со сбросом 3 и 4, сов.падения 5 и 6, общий перемножитель 7, непрерывное управляющее устройство 8 регулятора задержки, управляемый генератор тактовых имлульсов 9, сумматор W по модулю два, линию задержки на ноловину длительности импульса 11, аналоговый сумматор 12, регистр 13 опорной импульсной носледовательности со схемой логической обратной связи, дещифратор 14, блок обработки информации 15, объект регулирования 16.

Устройство работает следуюащм образом.

Входная псевдослучайная, бинарная импульсная последовательность

лг-1 где 1 0,1,..., Л-1; Го - длительность импульса, 1 х 0,5 . О х 0,5 ui - амплитуда имлульсов последовательности, равная или -1, поступает на вход перемножителей / и 2, на вторые входы которых поступает опорная псевдослучайная бинарная импульсная последовательность, в общем случае смещенная во времени относительно входной на величину А. Если входная импульсная последовательность велика, т. е. , то можно считать, что вероятности появления импульсов с амплитудами -f-1 и -1 равны 0,5. В этом случае на выходах интеграторов 3 н 4 сигналы и L4 UA| к моменту сброса пропорциональны значениям корреляционных функций Pl(A) f/(A);;„ (/), p,(A)fУ(A)y; (О, iJ,(t) a,( оп( 2t - 0,5To Xrect/ 2Га Сигналы УЗ(/+-А) и /4(i+-A) снимаются в момент времени, когда открыты ключи схем совпадения 5 к 6, управляемые дешифратором 14, на общий перемножитель 7. В зависимости от величины смещения (расстройки) А сигналы на выходе схем 5 и б раввы:Чприи,(А) при I Aj Го; К 1 + - К- , /7в(А) 7-02 npHf.AS-f «j;при Г.ЗАЭ, где К - коэффициент пропорциональности. Сигнал на выходе перемножителя 7 определяется сигналами /з|А| и f/(;|A| и зависит только от расстройки А. При 1А| Другими словами, путем перемножения усредненных напряжений, снимаемых с выхода информационного канала и канала опорного напряжения, можно получить информацию для формирования управляющего сигнала (сигнала ошибки), и через регулирующее устройство 8 осуществить перестройку генератора тактовых импульсов 9 и, следовательно, изменить величину смещения А. Канал формирования опорного напряжения состоит из .схем 10-13. Схема 11 представляет собой линию задержки на половину такта следования импульсов с генератора 9, который одновременно подключен к сумматору 12. Опорная импульсная последовательность () подаваемая на перемножитель 1, снимается с регистра 13, запускаемого импульсами с генератора 9. Опорная импульсная последовательность оп () подаваемая на неремножитель 2, формируется iB сумматоре 10 по модулю два, на который поступают импульсы как с регистра 13, так и с выхода сумматора 12. Дешифратор 14 служит для формирования сигнала управления схемами совпадения 5 и 6. Управление схемой 5 позволяет согласовать работу устройства передачи информации и устройства 15 ее обработки. Полное согласование достигается при А О, т. е. в случае, когда сигнал ошибки UT(A) на выходе общего перемнол ителя равен нулю. Предмет изобретения Вычислительное устройство для регулятора временной задержки электрического сигнала сложной формы, содержащее последовательно включенные канальный перемножитель, интегратор сброса, схему совпадения и блок обработки инс|)ормации, а также общий перемножитель, -управляющее устройство, управляемый генератор тактовых импульсов, регистр опорной импульсной последовательности с дешифратором и сумматор по модулю два, О7личающееся тем, что, с целью повышения качества обработки информации и упрощения устройства, в нем между входом устройства и блоком обработки информации установлены соединенные последовательно второй канальный перемножитель, интегратор и схема совпадения, причем, выходы обеих схем совпадения подключены ко входам общего перемножителя, к выходу генератора тактовых импульсов подключен аналоговый сумматор, второй вход которого подключен к первому через линию задержки, а выход аналогового сумматора подключен ко второму входу сумматора по модулю два, выход которого подключен ко входу второго канального перемножителя.

Даты

1970-01-01—Публикация