Изобретение относится к цифровым запоминающим устройствам вычислительных машин, в частности, к многоканальным анализаторам.

Известны запоминающие устройства на линиях задержки для многоканальных анализаторов импульсов, содержащие системы рециркуляции, арифметическое устройство, синхрогенератор тактовых, .маркерных и опорных импульсов, коммутатор-распределитель и коммутатор-объединитель.

Недостатком таких устройств является иовыщение тактовой частоты элементов запоминающего устройства и арифметического устройства в цепи нераспределенной последовательности импульсов, что затрудняет нспользование однотипных элементов в цепях линии задержки и арифметического устройства и п,елает невыполнимым устройство при отсутствии элементов, работающих на повыщенной тактовой частоте. Кроме того, при наличии стабилизации величины задержки только у одной линии задержки трудно выполнить устойчивую циркуляцию кодов при дальнейшем увеличении числа линий задержки в запоминающем устройстве и при более жестких допусках на величину задержки.

В описываемом устройство каждая система рециркуляции содержит стабилизатор и сумматор, соединенный с выходом коммутаторараспределителя и со входом коммутатораобъединителя, при этом входы коммутаторов связаны с синхрогеиератором, а стабилизатор задержки, обеспечивающий регулирование величины времени задержки сигналов, выполнен, например, в виде нагревателя звукопровода линии задержки.

Такое ныполнение повыщает быстродействие многоканального анализатора и упрощает его схемную реализацию.

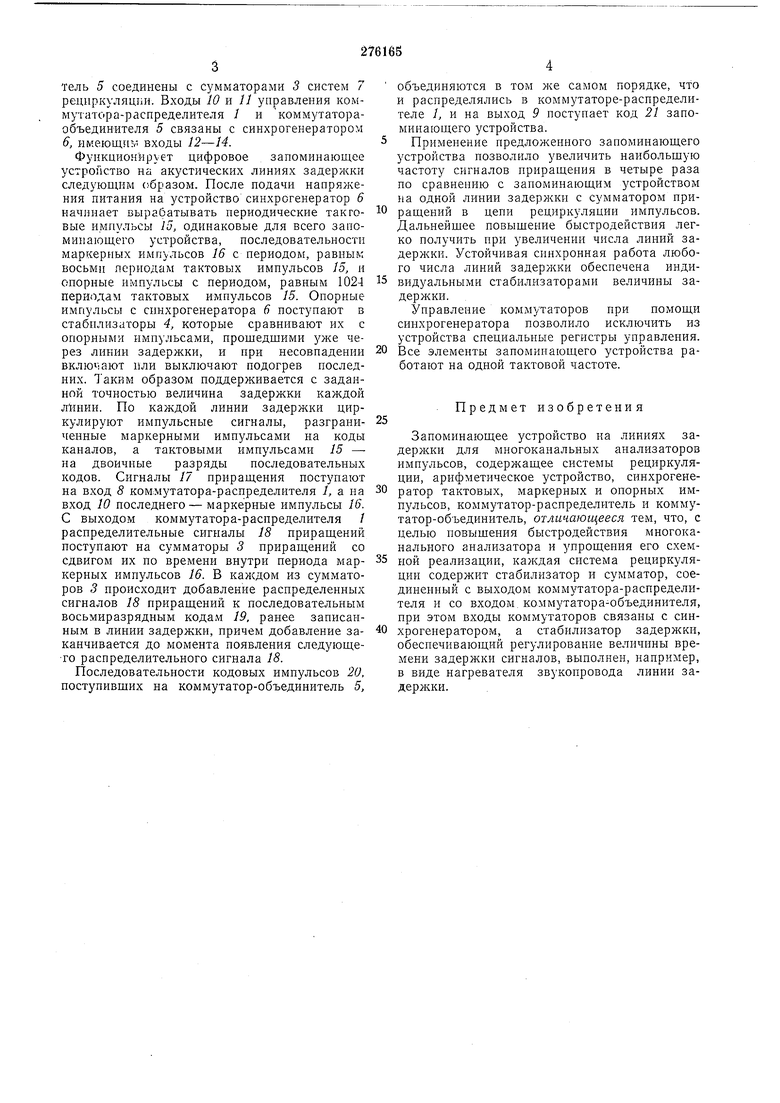

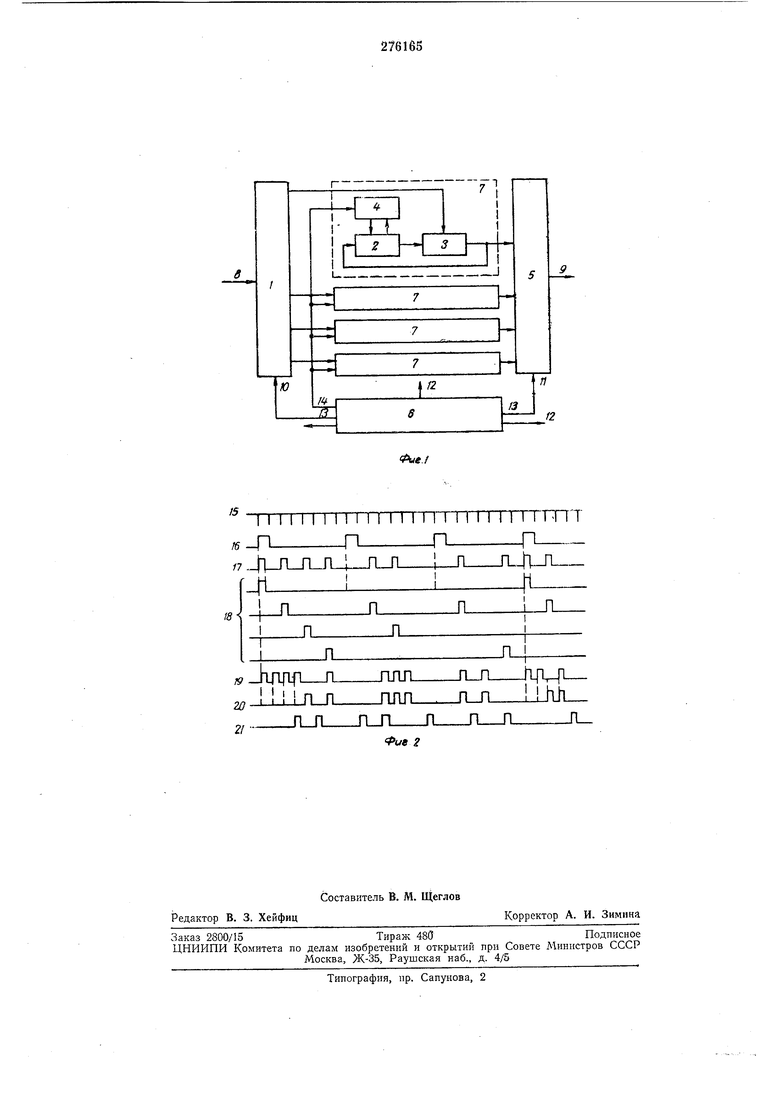

Иа фиг. 1 изображена блок-схема заноминающего устройства на акустических линиях задержки; на фиг. 2 - временная диаграмма цифрового заноминающего устройства на акустических линиях задержки.

В состав цифрового запоминающего устройства на акустических линиях задержки входят коммутатор-распределитель 1 сигналов приращения, четыре идентичные схемы 2 регенерации с сумматорами 3 приращений и стабилизаторами 4 отклонений времени задержки, коммутатор-объединитель 5, синхрогенератор 6. Схема 2 регенерации совместно с сумматором 5 нрнращений и стабилизатором 4 отклонений временн задерлши образуют стабилизированную систему 7 рециркуляции. Вход 8 коммутатора-раснределителя 1 является входом запоминающего устройст1за, а выход 9 коммутатора-объединителя 5 - выходом запоминающего устройства. Коммутатель 5 соединены с сумматорами 3 систем 7 рециркуляции. Входы 10 и 11 уиравления коммутатора-распределителя 1 и коммутатораобъединителя 5 связаны с синхрогенератором 6, имеющие входы 12-14.

Функционирует цифровое запоминающее устройство на акустических линиях задержки следующим образом. После нодачи нанряжения питания на устройство синхрогенератор 6 начинает вырабатывать периодические тактовые имиульсы 15, одинаковые для всего запоминающего устройства, последовательности маркерных импульсов 16 с периодом, равным восьми периодам тактовых импульсов 15, и онорные имиульсы с периодом, равным 1024 периодам тактовых имнульсов 15. Опорные импульсы с синхрогенератора 6 поступают в стабилизаторы 4, которые сравнивают их с опорными импульсами, прощедщими уже через линии задержки, и при несовпадении или выключают подогрев последних. Таким образом иоддерживается с заданной точностью величина задержки каждой линии. По каждой линии задержки циркулируют импульсные сигналы, разграниченные маркерными импульсами на коды каналов, а тактовыми импульсами 15 - на двоичные разряды последовательных кодов. Сигналы 17 приращения поступают на вход 8 коммутатора-распределителя 1, а на вход 10 последнего - маркерные импульсы 16. С выходом коммутатора-распределителя / распределительные сигналы 18 приращений поступают на сумматоры 3 приращений со сдвигом их по времени внутри периода маркерных импульсов 16. В каждом из сумматоров 3 происходит добавление расиределенных сигналов 18 приращений к последовательным восьмиразрядным кодам 19, ранее записанным в линии задержки, причем добавление заканчивается до момента появления следующето распределительного сигнала 18.

Последовательности кодовых импульсов 20, иоступивщих на коммутатор-объединитель 5,

объедиияются в том же самом порядке, что и распределялись в коммутаторе-распределителе 1, и на выход 9 поступает код 21 запоминающего устройства.

Применение предложенного заиомииающего устройства позволило увеличить наибольщую частоту сигналов приращения в четыре раза по сравнению с запоминающим устройством на одной линии задержки с сумматором приращений в цепи рециркуляции импульсов. Дальнейщее повыщение быстродействия легко получить при увеличении числа лииий задержки. Устойчивая синхронная работа любого числа линий задержки обеспечена индивидуальными стабилизаторами величины задержки.

Управлеиие коммутаторов при помощи синхрогенератора позволило исключить из устройства специальные регистры уиравления.

Все элементы запоминающего устройства работают на одной тактовой частоте.

Предмет изобретения

Запоминающее устройство на линиях задержки для многоканальных анализаторов импульсов, содержащее системы рециркуляции, арифметическое устройство, синхрогенератор тактовых, маркерных и опорных импульсов, коммутатор-распределитель и коммутатор-объединитель, отличающееся тем, что, с целью повыщеиия быстродействия многоканального анализатора и упрощеиия его схемной реализации, каждая система рециркуляции содержит стабилизатор и сумматор, соединенный с выходом коммутатора-распределителя и со входом, коммутатора-объединителя, при этом входы коммутаторов связаиы с синхрогенератором, а стабилизатор задержки, обеспечивающий регулирование величины времени задержки сигналов, выполнен, например, в виде нагревателя звукопровода линии задержки.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЦИФРОВОЙ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1971 |

|

SU297071A1 |

| Многоканальная система для морских сейсмических исследований | 1981 |

|

SU949587A2 |

| Многоканальная система для морских сейсмических исследований | 1975 |

|

SU558236A1 |

| ЭЛЕКТРОННАЯ КЛАВИШНАЯ ВЫЧИСЛИТЕЛЬНАЯ МАШИНА | 1973 |

|

SU395837A1 |

| УСТРОЙСТВО ДЛЯ ТЕЛЕФОННОЙ СВЯЗИ ГЛУХИХ | 1972 |

|

SU330568A1 |

| МНОГОКАНАЛЬНОЕ ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО ДЛЯ РЕГИСТРАЦИИ И СТАТИСТИЧЕСКОЙ ОБРАБОТКИИНФОРМАЦИИ | 1966 |

|

SU189238A1 |

| Устройство кодирования сигнала цветных графических изображений | 1987 |

|

SU1555917A1 |

| ФОТОНАБОРНЫЙ АВТОМАТ | 1967 |

|

SU193926A1 |

| УНИВЕРСАЛЬНАЯ ЦИФРОВАЯ УПРАВЛЯЮЩАЯ МАШИНА | 1965 |

|

SU170218A1 |

| Устройство синхронизации в одночастотных многоканальных адресных системах с временным разделением каналов | 1989 |

|

SU1811018A1 |

Авторы

Даты

1970-01-01—Публикация