л ел

Q1

&

| название | год | авторы | номер документа |

|---|---|---|---|

| Телевизионное устройство для формирования двухградационного сигнала графических изображений | 1986 |

|

SU1356260A1 |

| Устройство для формирования бинарных телевизионных сигналов | 1991 |

|

SU1818707A1 |

| Кодер телевизионного сигнала | 1990 |

|

SU1753596A2 |

| Способ формирования и приема телевизионного сигнала при передаче изображения и система для его осуществления | 1986 |

|

SU1453619A1 |

| Устройство для измерения частоты гармонического сигнала | 1987 |

|

SU1525607A1 |

| Устройство для формирования цветного изображения информации | 1982 |

|

SU1061292A1 |

| Устройство компенсации сигнала царапин кинопленки | 1988 |

|

SU1536521A2 |

| Цифровой обнаружитель-измеритель частоты | 1989 |

|

SU1797127A1 |

| Устройство для отображения информации на экране телевизионного индикатора | 1988 |

|

SU1508272A1 |

| УСТРОЙСТВО ДЛЯ ДИАГНОСТИКИ ПО БИОЛОГИЧЕСКИ АКТИВНЫМ ТОЧКАМ | 1991 |

|

RU2005460C1 |

Изобретение относится к телевидению. Цель изобретения - сокращение плотности информационного сигнала графических изображений. Устройство содержит датчик 1 цветоделенных и яркостных сигналов, АЦП 2, блок перекодирования (БП) 3 цветоделенных сигналов, оперативное запоминающее устройство (ОЗУ) 4, арифметический блок 5, блок 6 преобразования параллельного кода в последовательный и синхрогенератор 7. Цветоделенные сигналы с датчика 1 преобразуются в цифровую форму с помощью АЦП 2 и поступают в БП 3. Здесь осуществляется переход от трехмерного цветового пространства к условному одномерному с грубым квантованием полученной одномерной шкалы. С выхода БП 3 значения сигнала, соответствующие центрам защитных областей, подаются на ОЗУ 4, где производятся запись в память, в соответствии с телевизионным стандартом, и считывание по фрагментам. Значения сигнала, считываемые, пофрагментно из ОЗУ 4, поступают на арифметический блок 5 и далее на блок 6 преобразования. Цель достигается введением БП 3, ОЗУ 4 и синхрогенератора 7. Даны ил. выполнения блоков устройства. 5 ил.

Фиг.1

3155

Изобретение относится к технике телевидения и может быть использовано при кодировании телевизионных изображений цветных графических доку- ментов в замкнутых телевизионных системах, в частности в телевизионных системах, предназначенных для передачи неподвижных изображений по узкополосным каналам связи.

Целью изобретения является сокращение плотности информационного сигнала графических изображений.

На фиг. 1 представлена структурная электрическая схема устройства коди- рования сигнала цветных графических изображений; на фиг. . - структурная электрическая схема оперативного дополняющего устройства; на фиг. 3 структурная электрическая схема фор- мирователя адресов считывания; на фиг. 4 - структурная электрическая схема арифметического устройства, на фиг. 5 - структурная электрическая схема сумматора накопителя.

Устройство кодирования сигнала цветных графических изображений содержит датчик 1 цветоделенных и яр- костных сигналов, аналого-цифровой преобразователь (АЦП) 2, блок 3 пере- кодирования цветоделенных сигналов, оперативное запоминающее устройство (ОЗУ) 4, арифметический блок (АБ) 5, блок 6 преобразования параллельного кода в последовательный и синхрогене- ратор 7.

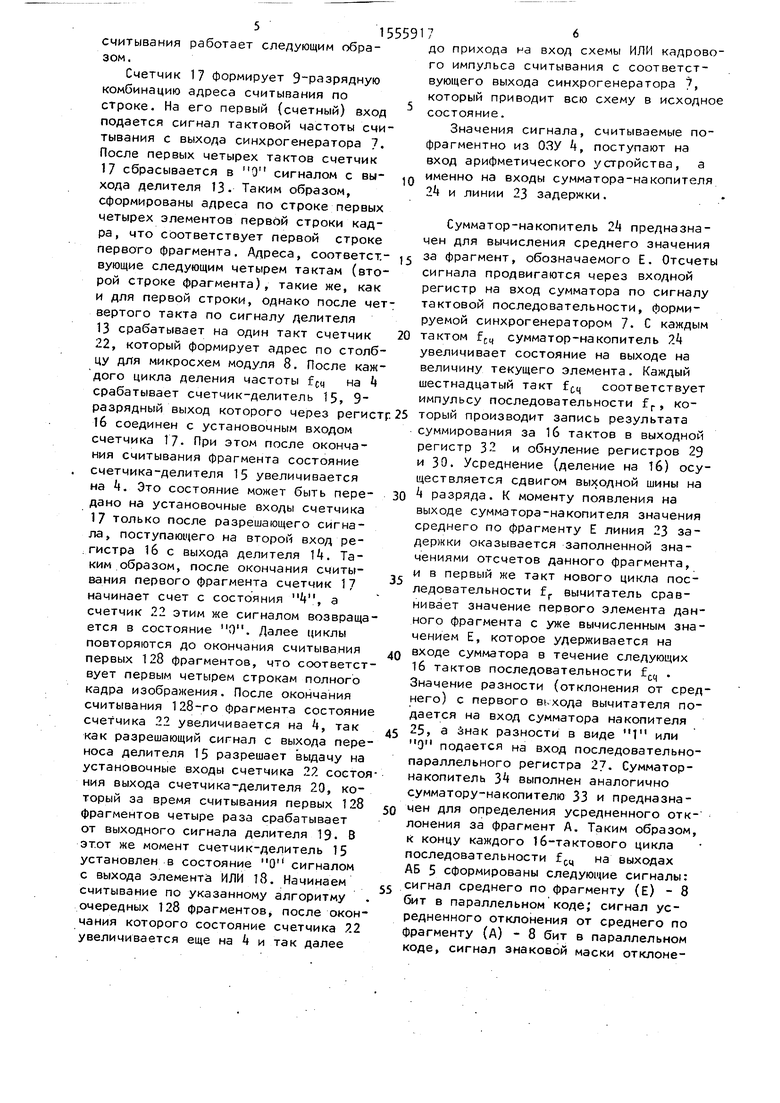

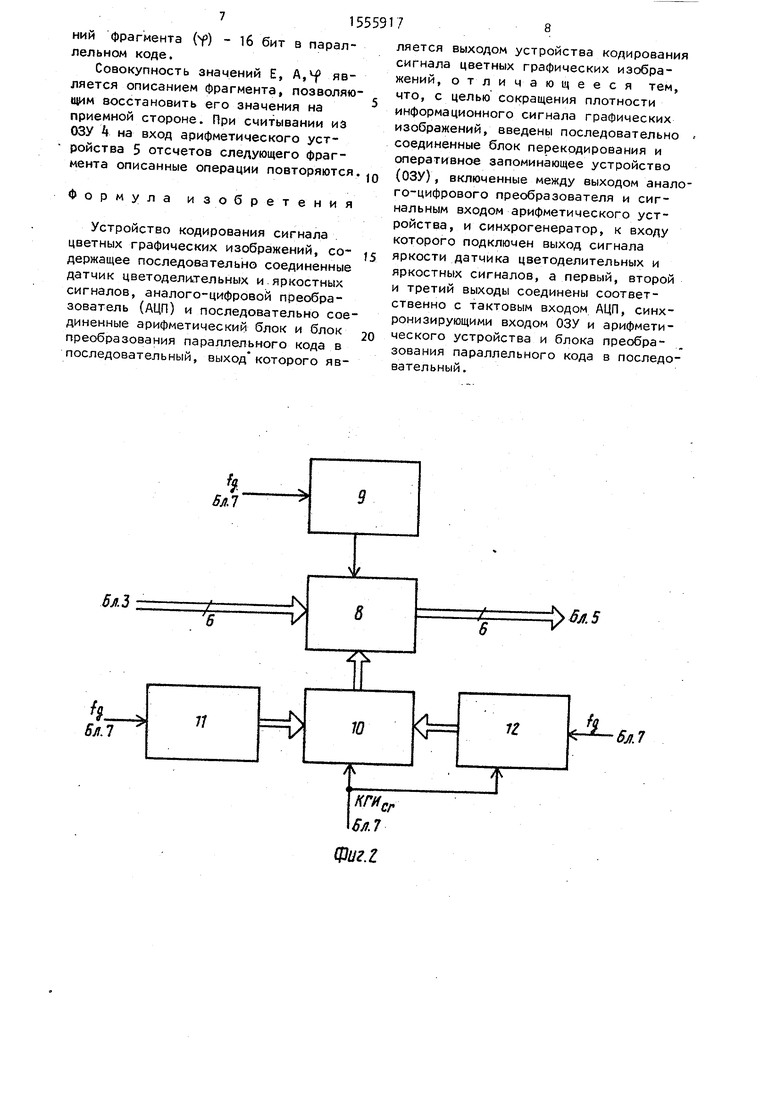

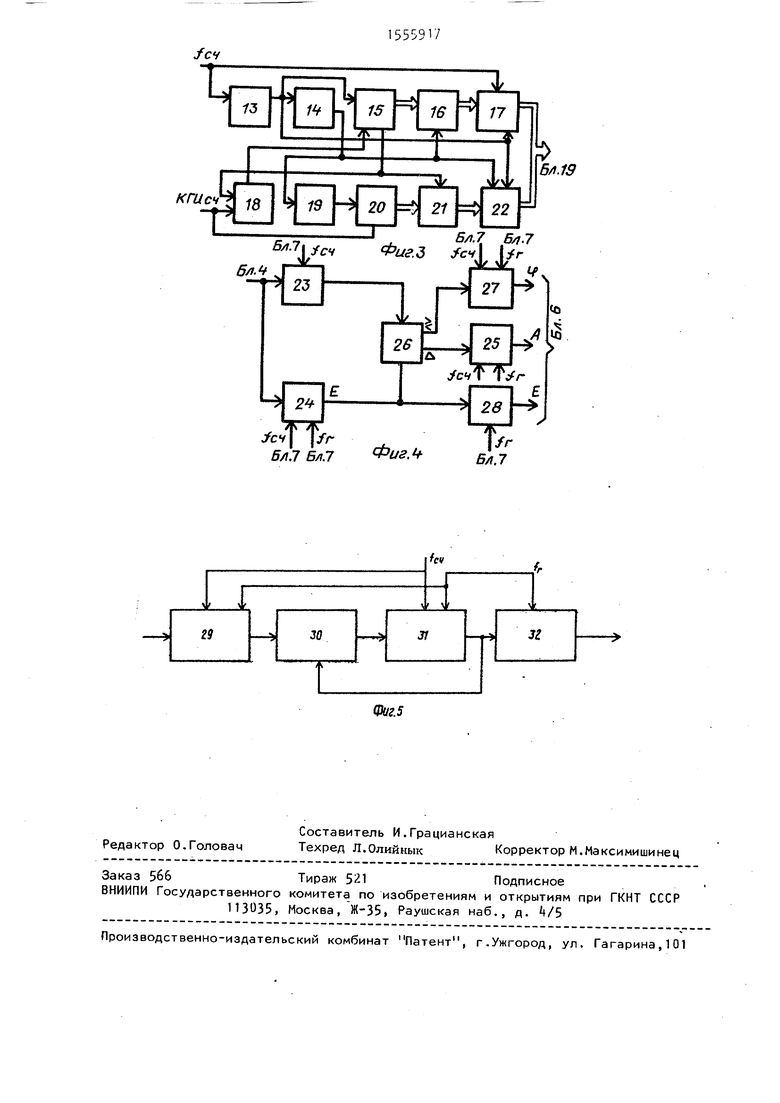

Оперативное запоминающее устройство k (фиг. 2) содержит модуль 8, блок 9 формирования управляющих сигналов, коммутатор 13 адресов, формирователь 11 адресов записи, формирователь 12 адресов считывания.

Формирователь 12 адресов считывани содержит первый 13 и второй 14 делители, счетчик-делитель 15, первый ре- гистр 16, счетчик 17, элемент ИПИ 18, третий делитель 29, счетчик-делитель 20, второй регистр 21 и счетчик 22.

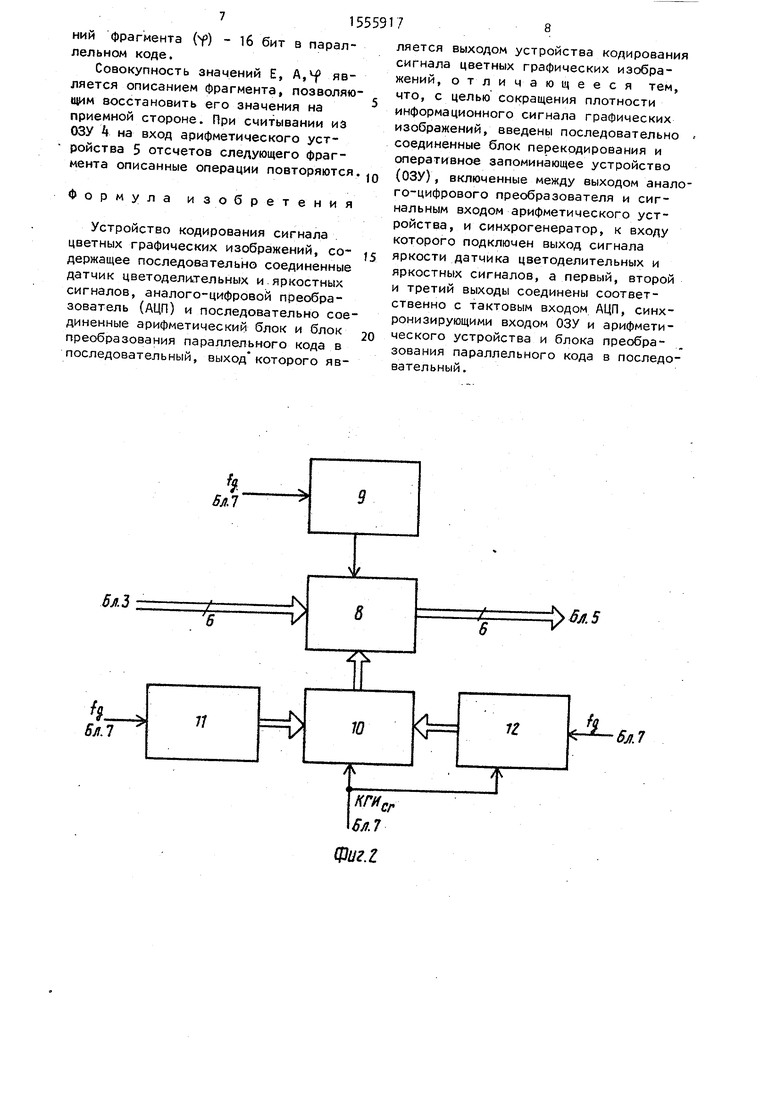

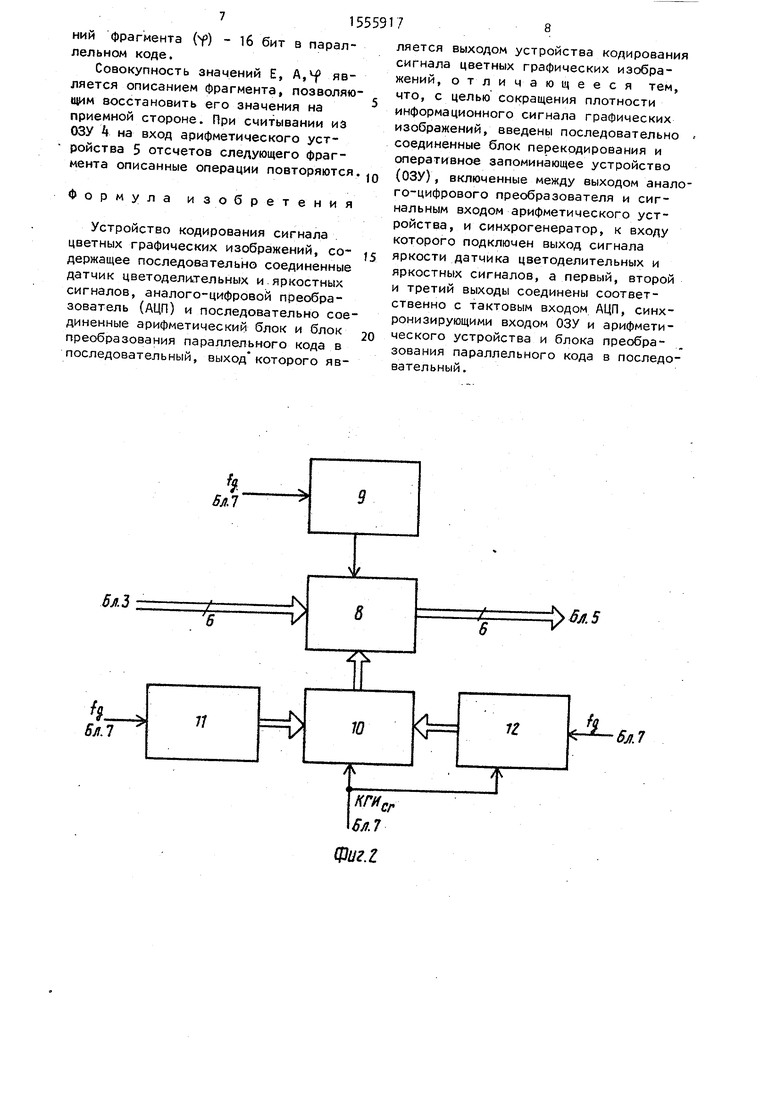

Арифметический блок 5 содержит (фиг. 4) линию 23 задержки, сумматор-

накопитель 2k, второй сумматор-накопитель 25, вычитатель 26, первый 27 и второй 28 регистры. Сумматор-накопитель 2k (фиг. 5) содержит входной регистр 29, сумматор 30, регистр 31 хранения и выходной регистр 32.

Устройство кодирования сигнала цветных графических изображений работает следующим образом.

g

5 0 5

о

Q

,-п

5

55

Цветоделенные сигналы телевизионного изображения размахом 0-1 В с выходов R, G, В датчика 1 подаются на соответствующие входы АЦП 2, а яркост- ный сигнал с выхода Y датчика 1 подается на вход синхрогенератора J. Преобразованные в цифровую форму в виде комбинаций 4-разрядного параллельного кода цветоделенные сигналы подаются на адресные входы постоянного запоминающего устройства (ПЗУ) блока 3- Параметры выбранного для реализации ПЗУ обеспечивают устойчивую работу перекодирующего устройства на частотах дискретизации до 11 МГц. В зависимости от сочетаний значений оцифрован- ных цветоделенных сигналов R, G, В на адресных входах ПЗУ блока 3 на выходе ПЗУ появляется значение (сигнал) , приводящее входные сигналы R, G и В в соответствие с значениями некоторой условной шкалы. Такое перекодирование означает переход от трехмерного цветового пространства к условному одномерному с грубым квантованием полученной одномерной шкалы. Иллюстрацией может служить разбиение площади цветового треугольника, ограниченной спектральным локусом на ряд зон, характеризующихся сравнительно однородным цветом. Если текущий элемент цветного графического изображения имеет значения сигналов R, G, В такие, что пересчитанные в значения X, Y, Z колориметрической системы, они попадают в зону с центром XjYjZ;, то значение текущего элемента заменяется на условное число, приписанное данной зоне. Множество таких чисел составляет набор уровней по условной шкале. Например, для весьма грубой ,. передачи информации о цвете только восемью основными цветами достаточно восьми уровней по условной шкале.

С выхода блока 3 значения сигнала, соответствующие центрам защитных областей, подаются на вход ОЗУ 4. Запись в память производится в соответствии с телевизионным стандартом, считывание - по фрагментам размером

4x4 элемента.

i

Формирователь 12 адреса записи представляет собой 18-разрядный счетчик, причем первые 9 разрядов формируют адрес по строке, а остальные 9 разрядов - по столбцу для микросхем модуля 8. Формирователь 12 адресов

считывания работает следующим образом.

Сметчик 17 формирует 9-рззрядную комбинацию адреса считывания по строке. На его первый (счетный) вход подается сигнал тактовой частоты считывания с выхода синхрогенератора 7. После первых четырех тактов счетчик 17 сбрасывается в О сигналом с выхода делителя 13. Таким образом, сформированы адреса по строке первых четырех элементов первой строки кадра, что соответствует первой строке

10

до прихода на вход схемы ИЛИ кадрового импульса считывания с соответствующего выхода синхрогенератора 7, который приводит всю схему в исходное состояние.

Значения сигнала, считываемые по- фрагментно из ОЗУ 4, поступают на вход арифметического устройства, а именно на входы сумматора-накопителя 2k и линии 23 задержки.

Сумматор-накопитель 24 предназначен для вычисления среднего значения

первого фрагмента. Адреса, соответст.- «с за фрагмент, обозначаемого Е. Отсчеты

t - w

вующие следующим четырем тактам (второй строке фрагмента), такие же, как и для первой строки, однако после четвертого такта по сигналу делителя 13 срабатывает на один такт счетчик 22, который формирует адрес по столбцу для микросхем модуля 8. После каждого цикла деления частоты на Ц срабатывает счетчик-делитель 15 9

сигнала продвигаются через входной регистр на вход сумматора по сигналу тактовой последовательности, формируемой синхрогенератором 7. С каждым 20 тактом fcq сумматор-накопитель 2k увеличивает состояние на выходе на величину текущего элемента. Каждый шестнадцатый такт ft4 соответствует импульсу последовательности fr, ко35

разрядный выход которого через регистр 25 торыи производит запись результата

16соединен с установочным входом счетчика 17- При этом после окончания считывания фрагмента состояние счетчика-делителя 15 увеличивается на k. Это состояние может быть передано на установочные входы счетчика

17только после разрешающего сигнала, поступающего на второй вход регистра 16 с выхода делителя 14. Таким образом, после окончания считывания первого фрагмента счетчик 17 начинает счет с состояния 4, а счетчик 22 этим же сигналом возвращается в состояние О. Далее циклы повторяются до окончания считывания первых 128 фрагментов, что соответствует первым четырем строкам полного кадра изображения. После окончания считывания 128-го фрагмента состояние счетчика 22 увеличивается на 4, так как разрешающий сигнал с выхода переноса делителя 15 разрешает выдачу на установочные входы счетчика 22 состояния выхода счетчика-делителя 20, который за время считывания первых 128 фрагментов четыре раза срабатывает

от выходного сигнала делителя 19- В этот же момент счетчик-делитель 15 установлен в состояние О сигналом с выхода элемента ИЛИ 18. Начинаем считывание по указанному алгоритму очередных 128 фрагментов, после окончания которого состояние счетчика 22 увеличивается еще на k и так далее

суммирования за 16 тактов в выходно регистр 32 и обнуление регистров 2 и 30. Усреднение (деление на 16) ос ществляется сдвигом выходной шины н

30 k разряда. К моменту появления на выходе сумматора-накопителя значени среднего по фрагменту Е линия 23 за держки оказывается заполненной значениями отсчетов данного фрагмента, и в первый же такт нового цикла пос ледовательности fr вычитатель сравнивает значение первого элемента да ного фрагмента с уже вычисленным зн чением Е, которое удерживается на

40 входе сумматора в течение следующих 16 тактов последовательности Јсч . Значение разности (отклонения от ср него) с первого вкхода вычитателя п дается на вход сумматора накопителя

45 25, a JsHaK разности в виде 1м или 0м подается на вход последовательн параллельного регистра 27. Сумматор накопитель 34 выполнен аналогично сумматору-накопителю 33 и предназна

50 чен для определения усредненного от лонения за фрагмент А. Таким образо к концу каждого 16-тактового цикла последовательности Јсц на выходах АБ 5 сформированы следующие сигналы

ее сигнал среднего по фрагменту (Е) - бит в параллельном коде; сигнал усредненного отклонения от среднего п фрагменту (А) - 8 бит в параллельном коде, сигнал знаковой маски отклоне

10

до прихода на вход схемы ИЛИ кадрового импульса считывания с соответствующего выхода синхрогенератора 7, который приводит всю схему в исходное состояние.

Значения сигнала, считываемые по- фрагментно из ОЗУ 4, поступают на вход арифметического устройства, а именно на входы сумматора-накопителя 2k и линии 23 задержки.

Сумматор-накопитель 24 предназначен для вычисления среднего значения

w

сигнала продвигаются через входной регистр на вход сумматора по сигналу тактовой последовательности, формируемой синхрогенератором 7. С каждым тактом fcq сумматор-накопитель 2k увеличивает состояние на выходе на величину текущего элемента. Каждый шестнадцатый такт ft4 соответствует импульсу последовательности fr, ко

торыи производит запись результата

суммирования за 16 тактов в выходной регистр 32 и обнуление регистров 29 и 30. Усреднение (деление на 16) осуществляется сдвигом выходной шины на

k разряда. К моменту появления на выходе сумматора-накопителя значения среднего по фрагменту Е линия 23 задержки оказывается заполненной значениями отсчетов данного фрагмента, и в первый же такт нового цикла последовательности fr вычитатель сравнивает значение первого элемента данного фрагмента с уже вычисленным значением Е, которое удерживается на

входе сумматора в течение следующих 16 тактов последовательности Јсч . Значение разности (отклонения от среднего) с первого вкхода вычитателя подается на вход сумматора накопителя

25, a JsHaK разности в виде 1м или 0м подается на вход последовательно- параллельного регистра 27. Сумматор- накопитель 34 выполнен аналогично сумматору-накопителю 33 и предназначен для определения усредненного отклонения за фрагмент А. Таким образом, к концу каждого 16-тактового цикла последовательности Јсц на выходах АБ 5 сформированы следующие сигналы:

сигнал среднего по фрагменту (Е) - 8 бит в параллельном коде; сигнал усредненного отклонения от среднего по фрагменту (А) - 8 бит в параллельном коде, сигнал знаковой маски отклонений фрагмента Of) - 16 бит в параллельном коде.

Совокупность значений Е, A,f является описанием фрагмента, позволяющим восстановить его значения на приемной стороне. При считывании из ОЗУ 4 на вход арифметического устройства 5 отсчетов следующего фрагмента описанные операции повторяются.

Формула изобретения

Устройство кодирования сигнала цветных графических изображений, содержащее последовательно соединенные датчик цветоделительных и яркостных сигналов, аналого-цифровой преобразователь (АЦП) и последовательно соединенные арифметический блок и блок преобразования параллельного кода в последовательный, выход которого яв.

ел 7

блЗ

ъ

Ј

6л. 7

Q

5

0

ляется выходом устройства кодирования сигнала цветных графических изображений, отличающееся тем, что, с целью сокращения плотности информационного сигнала графических изображений, введены последовательно соединенные блок перекодирования и оперативное запоминающее устройство (ОЗУ), включенные между выходом аналого-цифрового преобразователя и сигнальным входом арифметического устройства, и синхрогенератор, к входу которого подключен выход сигнала яркости датчика цветоделительных и яркостных сигналов, а первый, второй и третий выходы соединены соответственно с тактовым входом АЦП, синхронизирующими входом ОЗУ и арифметического устройства и блока преобразования параллельного кода в последовательный.

8

1

/4

V

I I

i

79

б/i. t

5/7.7 .

5/r-7|/cv /,3 Ус-vl t/r

16

f

I3L

21

-А -V

77

1

22

5/.А9

5/7.7 .7

с-vl t/r

/с

«

| Техника кино и телевидения | |||

| Дверной замок, автоматически запирающийся на ригель, удерживаемый в крайних своих положениях помощью серии парных, симметрично расположенных цугальт | 1914 |

|

SU1979A1 |

| ( УСТРОЙСТВО КОДИРОВАНИЯ СИГНАЛА ЦВЕТНЫХ ГРАФИЧЕСКИХ ИЗОБРАЖЕНИЙ | |||

| Способ получения на волокне оливково-зеленой окраски путем образования никелевого лака азокрасителя | 1920 |

|

SU57A1 |

| Цель изобретения - сокращение плотности информационного сигнала графических изображений | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Значения сигнала, считываемые пофрапментно из ОЗУ k, поступают на арифметический блок 5 и далее на блок 6 преобразования | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| выполнения блоков устройства | |||

| Кипятильник для воды | 1921 |

|

SU5A1 |

| € (Л | |||

Авторы

Даты

1990-04-07—Публикация

1987-07-06—Подача