Изобретение относнтся к технике телефонной связи и может быть исиользовано нри производстве электронных и квазиэлектронных автоматических телефонных станций.

Известны устройства для проверки регистров, состояш,ие, например, из дополнительного «контрольного регистра, схем эквивалентности, подключенных к идентичным выходам контролнруемого регистра, и устройства набора номера, подключенного ко входам обоих регистров. В качестве устройств набора номера используются специальные формирователи кодовых серий импульсов (устройство автоматического набора номера) или номеронабиратель.

Однако известные устройства сложны и при исиользованин номеронабирателя не обеспечивают высокой скорости нроверки.

С целью сакращения время лраверкн регистров, уменьшения количества оборудования, а также обеспечения контроля обрыва рабочих тактовых шин в любой декаде двоичного счетчика в предлагаемое устройство включены в качестве датчика имнульсов последовательно соединенные генератор тактовых имнульсов и схема запрета, а устройство индикации содержит две схемы совнадения контроля заполненного состояния, подключенных раздельно к единичным выходам счетчика и блока памяти регистра, н схему совпадения

контроля исходного состояння, подключенную к нулевым выходам блока памяти, ири этом выход нервой схемы совпадения контроля заполненного состояния подключен к управляющему входу схемы запрета н одному нз входов дополнительной схемы совпадения, к другому ,кютцр ой :П10Д1кл10чен 1выхоа юто.рой схемь 1сав|П1аае|Ния 1кантр;ол.я за1П10л|не1н;иог,о С Остоя;н|Ия. Выходы схемы (жвпаяенмя .ка;ют1роля И1сх:01Д1Н1аго состояния и дополнительной схемы совпадения подключены ко входам собирательной схемы.

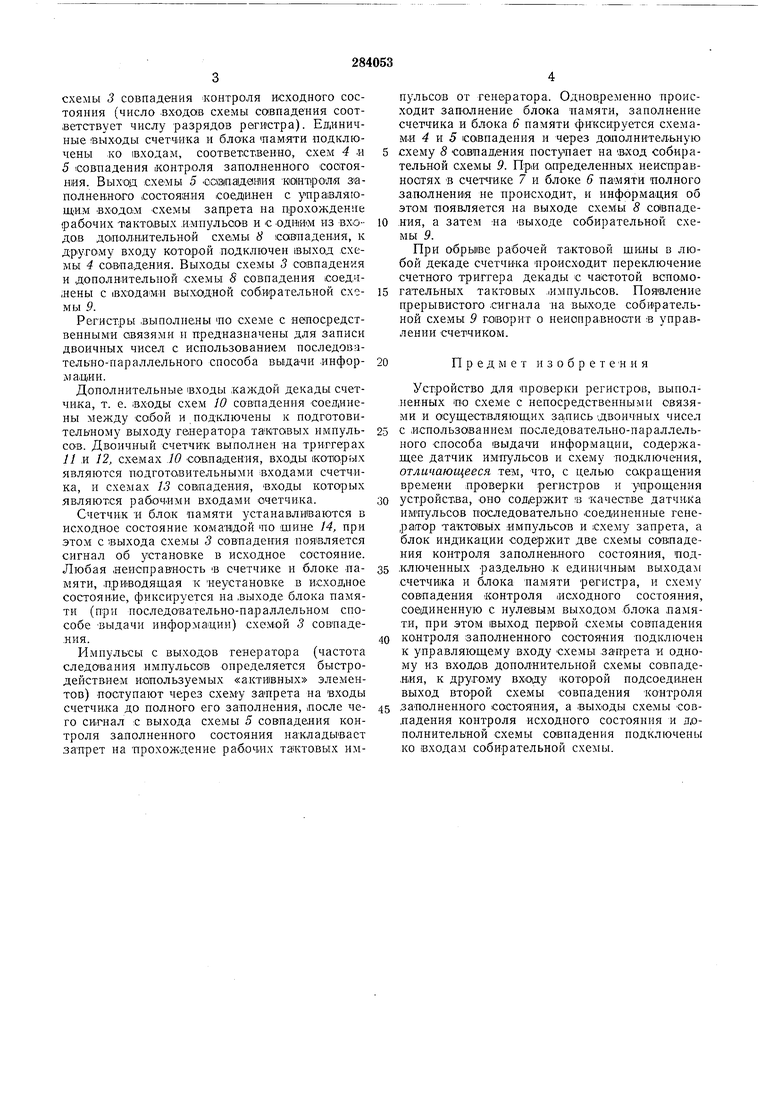

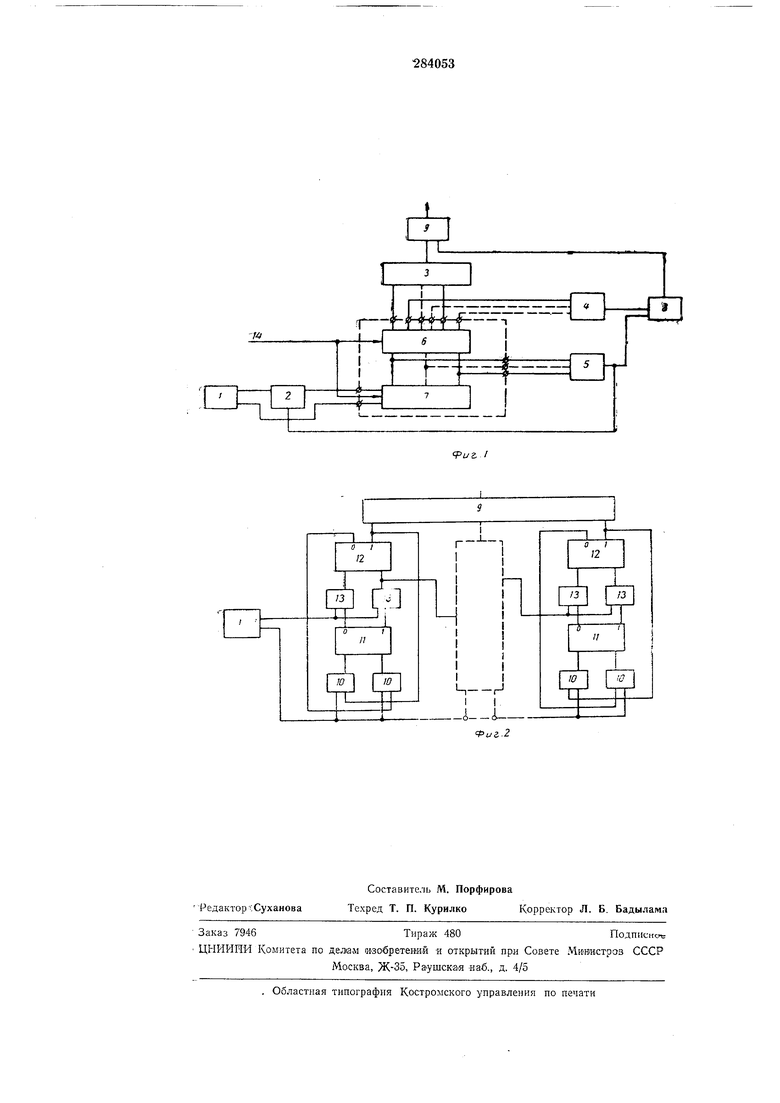

На фнг. 1 изображена функциональная схема иредлагаемого устройства совместно с контр олир уем ы.м регистром; на фиг. 2 - упрош,енная функциональная схема регистра.

Устройство содержит датчик импульсов, состоящий из генератора J тактовых импульсов, схемы 2 запрета; блок инднкацш соде| жит схему 3 совпадения контроля исходного состояния регистра, схемы 4 и 5 совпадения контроля заиолленного состояния, соответственно, блок 6 памяти .и двоичный счетчик 7 регистра; дополнительную схему 8 совнал,ения и собирательную схему 9.

Выход генератора тактовых н-мнульсов соединен через схему запрета с рабочим входом двоичного счетчика контролируемого регистра. Другой выход генератора иодключен к подготовительному .входу счетчика. }-1улевые схемы 3 совпадения контроля исходного состояния (число входов схемы совпадения соответствует числу разрядов регистра). Единичные выходы счетчгика и блока памяти подключены ко (входам, соответственно, схем 4 л 5 совнадения контроля заполненного собтояния. Выход схемы 5 .оазшадевня ио( занолненного состояния соединен с унра1вляющим входо:М схемы зап,рета на дрохождение (рабочих тактовых ямнульоов и с одн|И1М из входов долол.нительной схемы 8 савнаден.ия, к другОму входу которой подключен 1выхол схемы 4 совладения. Выходы схемы 3 совпадения и дополнительной схемы 5 совпадения соединены с (входаэди выходной собирательной схемы .9. Регистры выполнены НО схеме с неносредственнымИ связями н предназначены для записи двоичных чисел с использованием последовательно-параллельного способа выдачи .информа|Ции. Дополнительные входы .каждой декады счетчика, т. е. входы схем W совпадення соел1инены между собой и подключены к подготовительному выходу генератора тактовых импульсов. Двоичный счетчиК выполнен на триггерах 1 я 12, схемах 10 савнадення, входы которых являются подготовительными входами счетчика, и схемах 7,3 сов;падения, входы которых являются рабочими входами очетчика. Счетчик н блок памяти устанавливаются в исходное состояние командой по шине 14, при этом с выхода схемы 3 сов-падения появляется сигнал об установке в исходное состояние. Любая неисправность в счетчике н блоке памяти, приводящая к неустановке в исходное состояние, фиксируется на выходе блока памяти (при последовательно-параллельном способе выдачи информации) схемой 3 совпаде.ния. Импульсы с выходов генератора (частота следования импульсов определяется быстродействием используемых «акти1вных элементов) поступают через схему занрета па входы счетчика до полного его заполнения, лосле чего сигнал с выхода схемы 5 совпадения контроля заполненного состояния накладывает запрет на прохождение рабочих таистовых импульсов от генератора. Одновременно происходит заполнение блока памяти, заполнение счетчика и блока 6 памяти фиксируется схемами 4 1 5 1С01Впадения н через даполнител-ьную схему 8 совпадения поступает на вход собирательной схемы 9. При определенных неисправноатях в счетчике 7 и блоке 6 памяти полного заполнения не происходит, и информация об этом появляется на выходе схемы 8 соепаде.ния, а затем яа выходе собирательной схемы 9. При обрьиве рабочей тактовой ши,ны в любой декаде счетчика происходит переключение счетного триггера декады с частотой вспомогательных тактовых ..импульсов. Появление прерывистого сягнала яа выходе собирательной схемы 9 го1ворит о неисправности в управлении счетчиком. Предмет изобретен и я Устройство для проверки регистров, выполненных по схеме с непосредственными связями и осуществляющих зались .двоичных чисел с яспользаванием последовательно-параллельного способа выдачи информации, содержащее датчик импульсов и схему подключения, отличающееся тем, что, с целью сокращения времени проверки регистров и упрощения устройства, оно сод,ержят в качестве датчика импульсов последовательно соединенные генератор тактовых импульсов и схему запрета, а блок индикации содержит две схемы совпадения контроля заполненного состояния, подключенных раздельно к единичным выхода счетчика и блока намяти регистра, и схему совПадения контроля исходного состояния, соединенную с нулевым выходом блока памяти, при этом выход первой схемы совпадения контроля заполненного состояния подключен к управляющему входу схемы запрета и одному из входов дополнительной схемы совпадеН|ИЯ, к другому входу 1которой подсоединен выход второй схемы совпадения контроля .заполненного состояния, а выходы схемы совладения контроля исходного состояния и я,ополнятельной схемы савпадения подключены ко входам собирательной схемы.

| название | год | авторы | номер документа |

|---|---|---|---|

| Дискретный умножитель частоты следования импульсов | 1973 |

|

SU446879A1 |

| ФОРМИРОВАТЕЛЬ КОДА МОРЗЕ | 1972 |

|

SU331498A1 |

| УСТРОЙСТВО числового ПРОГРАММНОГО УПРАВЛЕНИЯСТАНКАМИ | 1969 |

|

SU257265A1 |

| ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО ДЛЯ СИСТЕМ ПРОГРАММНОГО УПРАВЛЕНИЯ ДВУХКООРДИНАТНЫМИ ПЕРЕМЕЩЕНИЯМИ | 1967 |

|

SU223465A1 |

| РАСПРЕДЕЛИТЕЛЬ ИМПУЛЬСОВ | 1971 |

|

SU306564A1 |

| ЛИНЕЙНЫЙ ИНТЕРПОЛЯТОР С ЗАПОЛНЕНИЕМ ОПОРНОГО СЧЕТЧИКА МНОГОРАЗРЯДНЫМИ КОДАМИ | 1968 |

|

SU206911A1 |

| БЫСТРОДЕЙСТВУЮЩИЙ МИНИМИЗАТОР БУЛЕВЫХ ФУНКЦИЙ | 1970 |

|

SU271897A1 |

| Устройство для управления электроприводами разветвленных конвейерных линий | 1971 |

|

SU485533A1 |

| УСТРОЙСТВО для ВВОДА ИНФОРМАЦИИ | 1973 |

|

SU395830A1 |

| Датчик времени для обучающего устройства | 1977 |

|

SU739624A1 |

Даты

1970-01-01—Публикация