Известен линейный интерполятор с заполнением опорного счетчика многоразрядными кодами на однотипных феррит-транзисторных модулях, содержащий регистры сдвига, сумматор, триггер и логические элементы.

Предложенное устройство отличается от известных тем, что в нем выходы двух регистров сдвига соединены со входами двух схем «НЕ и через схемы совпадений, собирательную схему и тактирующую ячейку подключены к одному из входов сумматора, другой вход которого через схему совпадений соединен с выходом третьего регистра сдвига и вторыми входами схем «НЕ, а выход переноса - со входом схемы совпадения обнаружения конца счета. Управляющие входы подключенных к выходам первых двух регистров сдвига схем совпадений соединены с единичным выходом триггера, а их выходы - со входами выходных схем совпадений и через собирательную схему - с нулевым входом того же триггера. Единичный вход последнего подключен к схеме «НЕ, соединенной с генератором тактовых илшульсов и через собирательную схему - с выходами упомянутых двух схем «НЕ, которые через тактирующие ячейки соединены также со вторыми входами выходных схем совпадений, подключенных по входам считывания к генератору тактовых импульсов.

Это позволяет упростить схему устройства при сохранении высокого быстродействия следования выходных импульсов.

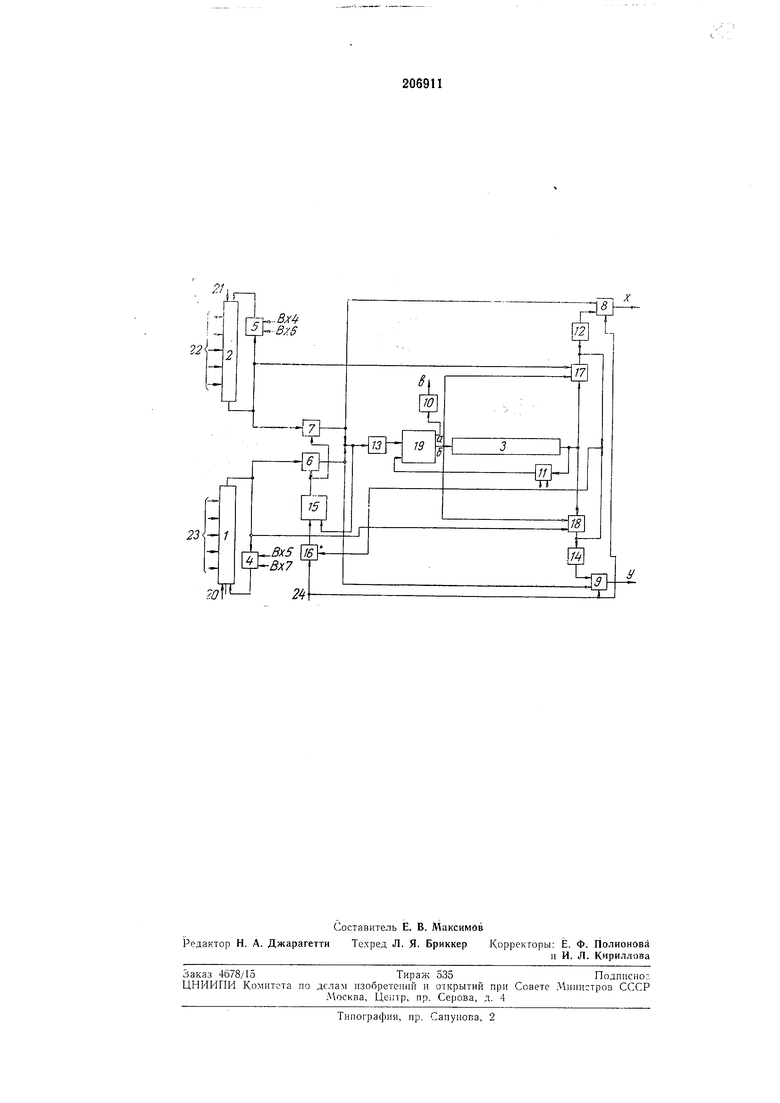

Функциональная схема интерполятора приведена на чертеже.

Он содержит регистры 1-3 сдвига, схемы «И 4-11, тактирующие ячейки 12-14, выполняющие функции задержки, триггер 15, схемы «НЕ 16-18, одноразрядный сумматор 19, входы последовательных кодов чисел 20, 21, 22-23 параллельных кодов чисел, Еход частоты 24, заданной с генератора. Схема работает следующим образом. п - разрядные числа в двоичном коде ввидятся в регистры 1 и 2 либо последовательно на входы 20 и 21 (старщими разрядами вперед), либо параллельно на входы 22 и 23.

После записи в регистры / и 2 числа циркулируют в них с периодом циркуляции Т. Частота циркуляции соответетвенно составляет . Перед началом работы схемы триггер 15 находится в состоянии, при котором схемы 5 и 7 заперты, и опорный счетчик, включающий сумматор 19 и регистр 3, не считает. Для ускорения процесса счета в устройстве в каждом цикле его работы на вход счетчика сразу поступает многоразрядное число, обеспечивающее получение сигнала на одном из выходов интерполятора или на обоих в каждом цикле его работы. Это достигается тем, что импульсы, подаваемые на вход 24 с частотой /з (равна или кратна /), опрашивают схемы 8 п 9, а также ставят триггер 15 в положение, при котором схемы 6 н 7 могут пропускать импульсы с регистров 1 2, на входы сумматора 19 через тактирующую ячейку 13. Импульсы /з подготовляют схемы и 7 к тому моменту, когда с регистров 1 и 2 начинают выходить старшие разряды. Первый значащий импульс, прощедший через схему б и 7, закрывает триггер 15, и эти схемы перестают пропускать импульсы с регистров 1 к 2. Ячейка 13 задерживает импульс ровно на один цикл (число циклов равно количеству разрядов), так что в сумматор J9 импульс поступает всегда на цикл позже.

На схемы 17, 18 поступают импульсы с регдстров.1. и .2, импульсы с выхода б сумматора 19 я с выхода регистра 3.

Импульс, прощедший на выход б сумматора 19, опрашивает схемы 17 и 18. Если в данном цикле были импульсы с регистров 1 и 2, и не было с регистра 3, то со схем 17 или 18 или с обеих одновременно появится импульс, который-наложит запрет на проход следующего импульса /3 через схему 16. Одновременно импульсы, выщедщие со схем 17 и 18, поступают соответственно на тактирующие ячейки 12 и 14, где задерживаются на один период /3. При этом после прохода следующего импульса /3 со схемы 8 или 9 .или с обеих одновременно выходят импульсы, а состояние сумматора остается неизменным, так как триггер 15 не открывался и через схемы 5 и 7 не было пропущено ни одного импульса. Если же в данном цикле на всех входах схем 17 и 18 появятся импульсы, то с их выходов не выйдет ни одного импульса, так как на них будет наложен запрет импульсом с выхода

регистра 3. Таким образом, к моменту полного заполнения счетчика, который обнаруживается схемой 10 совпадения, с выхода 8 и выхода 9у выйдет количество импульсов, записанное в регистрах 1 и 2. Импульсы с выходных схем 8, 9 будут выходить синхронно с частотой /3Предмет изобретения

Линейный интерполятор с заполнением опорного счетчика многоразрядными кодами на однотипных феррит-транзисторных модулях, содержащий регистры сдвига, сумматор, триггер и логические элементы, отличающийся

тем, что, с целью упрощения схемы при сохранении высокого быстродействия следования выходных импульсов, в нем выходы двух регистров сдвига соединены со входами двух схем «НЕ и через схемы совпадений, собирательную схему и тактирующую ячейку подключены к одному из входов сумматора, другой вход которого через схему совпадений соединен с выходом третьего регистра сдвига и вторыми входами схем «НЕ, а выход переноса - со входом схемы совпадения обнаружения конца счета; управляющие входы подключенных к выходам первых двух регистров сдвига схем совпадений соединены с единичным выходом триггера, а их выходы - со

входами выходных схем совпадений и через собирательную схему - с нулевым входом того же триггера, единичный вход которого подключен к схеме «НЕ, соединенной с генератором тактовых импульсов и через собирательную схему - с выходами упомянутых Еыще двух схем «НЕ, которые через тактирующие ячейки соединены также со вторыми входами выходных схем совпадений, подключенных по входам считывания к генератору

тактовых импульсов.

.oJ

| название | год | авторы | номер документа |

|---|---|---|---|

| ПОСЛЕДОВАТЕЛЬНЫЙ ДЕСЯТИЧНЫЙ НАКАПЛИВАЮЩИЙ СУММАТОР С ПАРАЛЛЕЛЬНЫМ СДВИГОМ | 1969 |

|

SU250544A1 |

| ЦИФРОВОЙ ДИФФЕРЕНЦИАЛЬНЫЙ ФАЗОМЕТР | 1973 |

|

SU361447A1 |

| Устройство для считывания графической информации | 1988 |

|

SU1606980A1 |

| Круговой интерполятор | 1985 |

|

SU1359772A1 |

| УСТРОЙСТВО для ПРОСТРАНСТВЕННО-ВРЕМЕННОГО СЕЙСМИЧЕСКОГО АНАЛИЗА | 1973 |

|

SU393742A1 |

| МНОЖИТЕЛЬНО-ДЕЛИТЕЛЬНОЕ УСТРОЙСТВО | 1968 |

|

SU217718A1 |

| УСТРОЙСТВО для ПРЕОБРАЗОВАНИЯ ДВОИЧНЫХ КОДОВ ПРИРАЩЕНИЯ ФУНКЦИИ | 1968 |

|

SU208344A1 |

| Устройство для программного управления | 1986 |

|

SU1335933A1 |

| Цифровой линейный интерполятор | 1989 |

|

SU1693592A1 |

| Цифровой линейный интерполятор | 1989 |

|

SU1631518A1 |

Даты

1968-01-01—Публикация