Изобретение относится к области автоматики и вычислительной техники и может быть иоиользовано в устройствах логического типа иовышенной надежности, в частности, нри построении схем этих устройств по .1ажоритарH0 iy принцшгу.

Известеи межоритарный элемеит, выполненный на логнческих схемах «И и «ИЛИ.

Иедостатком такого элемента яв.лястся то, что он имеет ограниченное число входов и выходов и не может быть иснользован при пзмененни числа входов и гюрога элемента.

Целью изобретения является расширение функциональных возмол постсй элемента, вынолненного на схемах «И и «ИЛИ.

Поставленная цель достигается тем, что мажоритарный элемент выполпен в впде матрицы с числом строк и столбцов, равны:.м числу источииков входных сигналов, составленной из однотинных ячеек, содерлсащих схему «И, подключеииую к первому входу схемы «ИЛИ, причем выход схемы «ИЛИ, расположенной в i-u строке, /-М столбце матрицы, соединен со вторым входом схемы «ИЛИ, расположенной в L-H строке, (/-г1)-м столбце и первым входом схемы «И, расположенной в (1+1)-й строке, (/+1)-;м столбце. Вторые входы схем «И, расположенным в /-м столбце, подключены к /-у источнику входного сигнала, а первые входы схем «И, расположенных з первой

строке, подключены к нсгочнику управляющего сигнала.

Это дало возможность не изменяя схемы мажоритарного элемента, получать выходной

сигнал на /-м выходе при одновре.менной подаче входных сигналов не менее, чем на i входов, т. е. выходной снгнал на нервом выходе изменяет свое значенне ири наличии входного сигнала на любом одном входе элемента; на

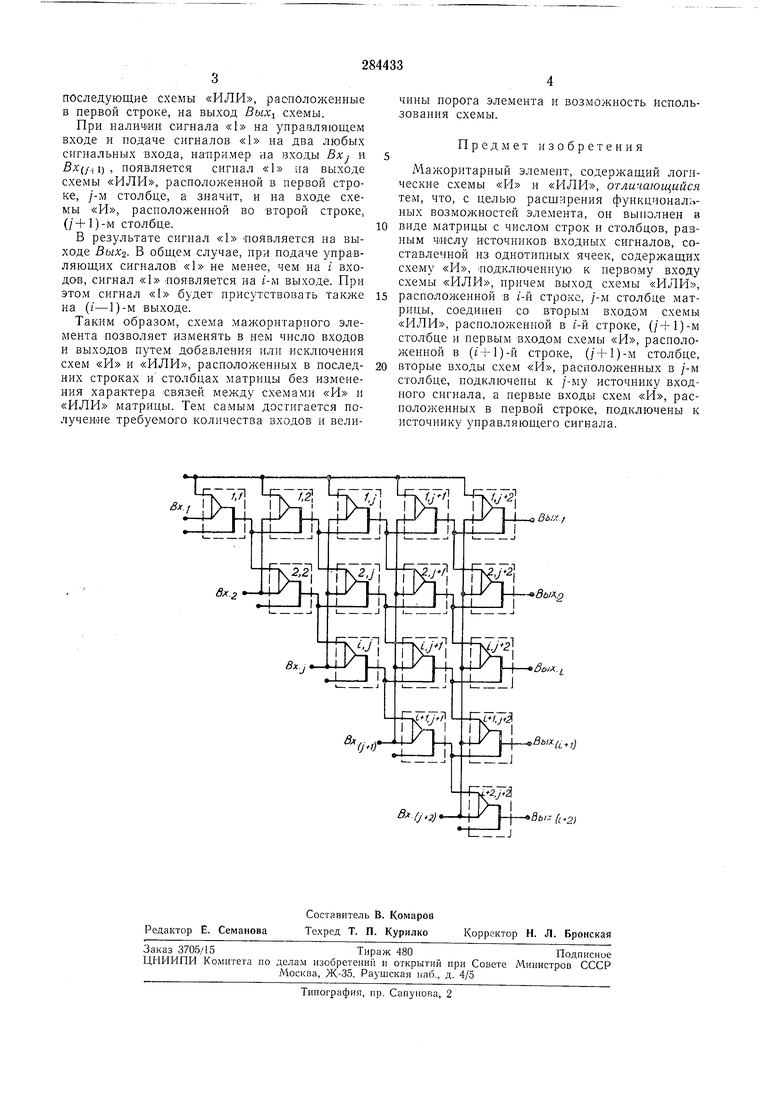

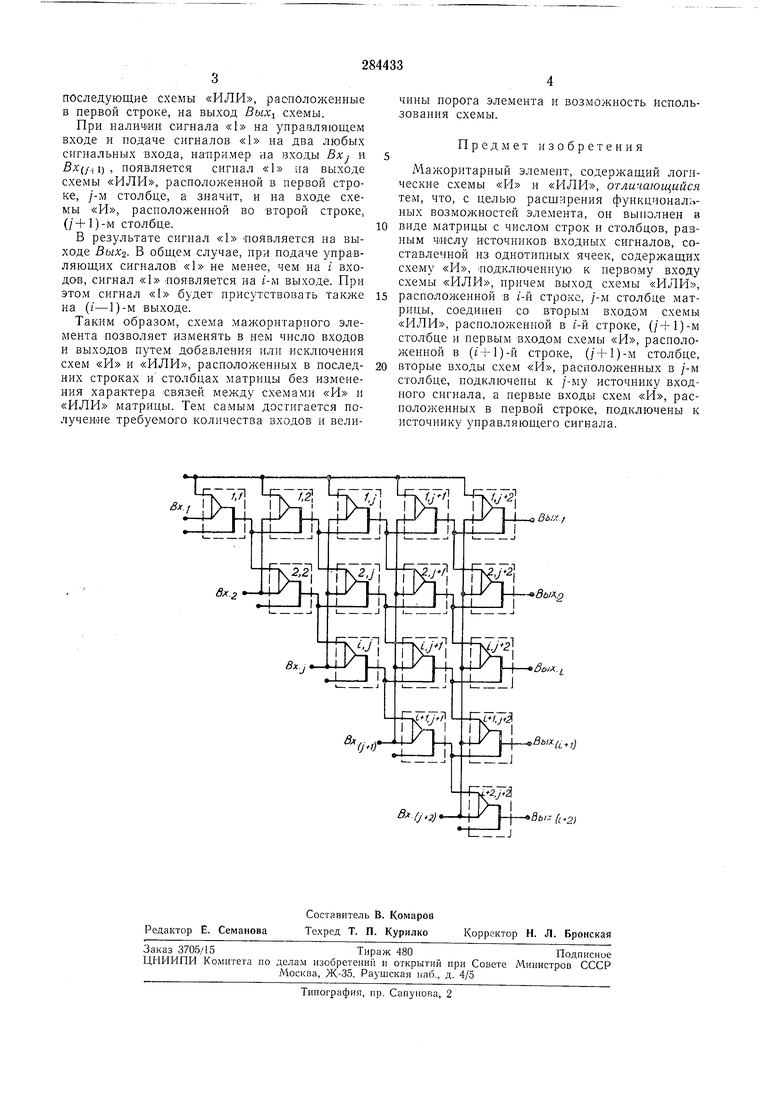

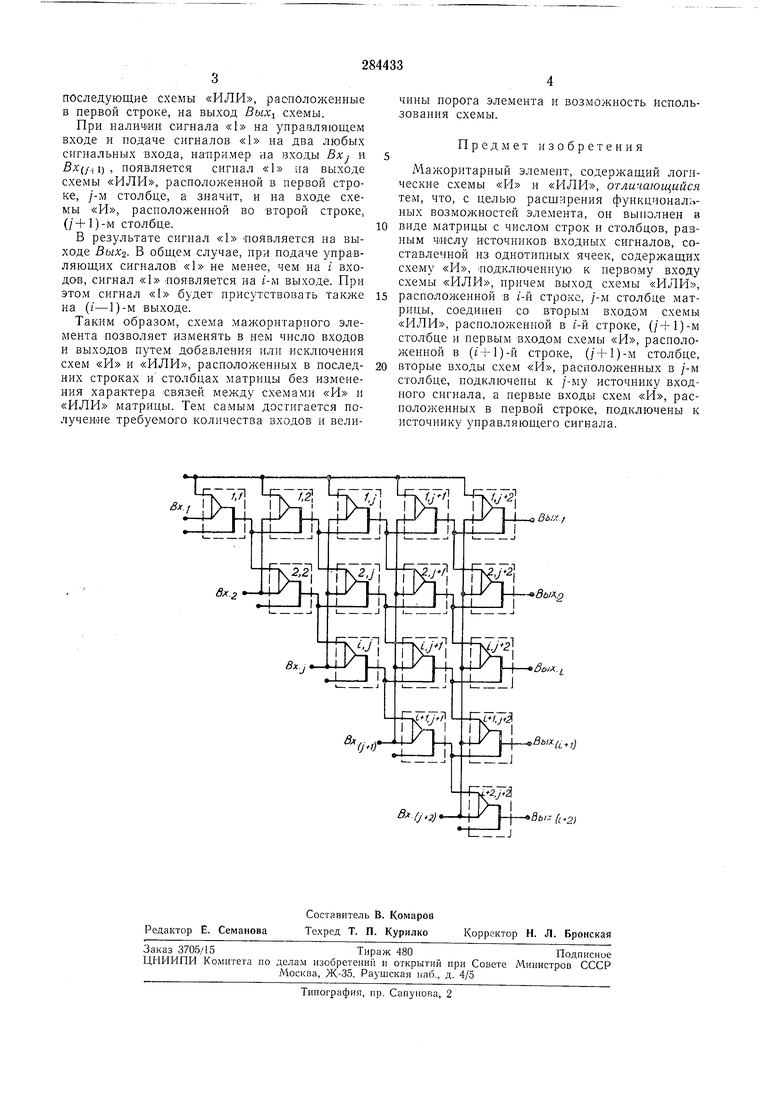

втором выходе- пря налични входных сигналов на любых двух входах элемента; на третьем выходе-при налнчпн входных сигналов на любых трех входах элемента н т. д . Па чертеже 1нредставлена функциональная

схема мажорНтарного элемента, содерл ащая логические схемы «И и «ИЛИ, объединенные в однотипные функцгюиальные ячейки и соединениые упорядоченным одииаковым образом.

В исходное состояние на все входы Вх, Вх, Bxj, ВА(;+) и 5(у+2) элемеита иоданы сигналы, соответствующие нулевому уровгно. Ири этом на выходах Вых, ВыХ2, Вых, BbiX(i-ri) и ВыХ(щ элемента присутствуют также оигналы нулевого уровня. При подаче единичиых сигналов на уиравляющий вход и на один любой сигнальный вход схемы, нанрнмер, на вход В.х1, на выходе схемы «ИЛИ, расположенной в первой строке, нервом столбце, нопоследующие схемы «ИЛИ, расположенные в первой строке, на выход Вых схемы.

При наличии сигнала «1 на управляющем входе и подаче сигналов «1 на два любых сигнальных входа, например на входы Bxj и Bx() , появляется сигнал «1 на выходе схемы «ИЛИ, расположенной в первой строке, /-М столбце, а значит, и на входе схемы «И, расположенной во -второй строке, (/+ 1)-м столбце.

В результате сигнал «1 появляется па выходе BbiXz. В общем случае, при подаче управляющих сигналов «1 не мепее, чем на / входов, сигнал «1 -появляется на I-M выходе. При этом сигнал «1 будет присутствовать также на (L-1)-м выходе.

Таким образом, схема мажоритарного элемента позволяет изменять в нем число входов и выходов путем добавления или исключения схем «И и «ИЛИ, расположенных в последних строках и столбцах матрицы без измепения характера связей между схемами «И и «ИЛИ матр:ицы. Тем самым достигается получение требуемого количества входов и величины порога элемента и возможность Использования схемы.

Предмет изобретения

Мажоритарный элемент, содержащий логические схемы «И и «ИЛИ, отличающийся тем, что, с целью расширения функциональных возможностей элемента, он выполнен в

виде матрицы с числом строк и столбцов, разным Числу источников входных сигналов, составленной из однотипных ячеек, содержащих схему «И, 1подключениую к первому входу схемы «ИЛИ, причем выход схемы «ИЛИ,

расположенной в /-и строке, /-м столбце матрицы, соединен со вторым входом схемы «ИЛИ, расположенной в i-и строке, (/Ч-1)-м столбце и цервым входом схемы «И, расположенной в (г+1)-й строке, (/+1)-м столбце,

вторые входы схем «И, расположенных в /-м столбце, подключены к /-му источнику входного сигнала, а первые входы схем «И, расположенных в первой строке, подключены к источнику управляющего сигнала.

| название | год | авторы | номер документа |

|---|---|---|---|

| Мажоритарный элемент | 1978 |

|

SU752808A1 |

| ИЗМЕРИТЕЛЬНЫЙ КОММУТАТОР | 1971 |

|

SU293252A1 |

| Матричный коммутатор | 1987 |

|

SU1429308A1 |

| Коммутационное устройство | 1985 |

|

SU1307573A1 |

| ПРЕОБРАЗОВАТЕЛЬ КОДОВ ИЗ ОСТАТОЧНОЙ СИСТЕМЫ СЧИСЛЕНИЯ В ПОЛИАДИЧЕСКУЮ | 1973 |

|

SU407301A1 |

| ТРЕХКАНАЛЬНЫЙ МАЖОРИТАРНЫЙ ЭЛЕМЕНТ | 1972 |

|

SU430508A1 |

| Устройство для обнаружения и исправления ошибок | 1990 |

|

SU1785041A1 |

| АВТОМАТИЧЕСКИЙ СИНТЕЗАТОР ОДНОТАКТНЫХ РЕЛЕЙНЫХ СХЕМ | 1970 |

|

SU453698A1 |

| Устройство для обнаружения и исправления ошибок в блоках памяти | 1988 |

|

SU1525746A1 |

| МНОГОЗНАЧНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ | 1970 |

|

SU262954A1 |

BblK-lL-.,)

8}.lJ.2) (i 2)

Авторы

Даты

1970-01-01—Публикация