I

Изобретение относится к области вычислительной техники и предназначено для преобразования кодов, заданных в системе счисления остаточных классов (СОК), в полиадическую систему (в коды со смешанными основаниями - КСО).

Известен преобразователь кодов СОК в полиадическую систему счисления, содержащий

yv

(ЛГ-1)(Лг+4)

+ 2 ()-1)

2

l (N-2) (Л-1)

модульных суммирующих и табличных схем (где Л - число модулей СОК).

Предложенное устройство отличается тем, что каждый и-й параллельный модульный канал преобразования содержит (i-1) табличных схем модульного сложения, блок определения остатка частного содержит (N-2) табличных схем модульного сложения (где Л - число модулей входного кода), а каждая табличная схема модульного сложения содержит идентификатор переносов, логическую схему формирования межканального переноса и две схемы перекодирования и свертки, входы первой из которых соединены с выходами операндного дешифратора столбцов, а выходы - со входами вентилей первой группы; входы второй схемы перекодирования и свертки соединены с выходами аперандного дешифратора строк, а выходы - со входами вентилей второй группы; входы идентификатора переноса соединены со входами межканального переноса, а выходы - со входами вентилей первой группы и логической схемы формирования межканального переноса, с другими входами которой соединены выходы

вентилей первой и второй групп и обеих схем перекодирования и свертки; входы табличных схем модульного сложения, соответствующие k-му уровню преобразования 1-го параллельного модульного канала преобразования, соединены с выходами табличных схем модульного сложения, соответствующих (k-1)-му уровню преобразования того же канала; выходы межканальных переносов табличных схем модульного сложения i-ro

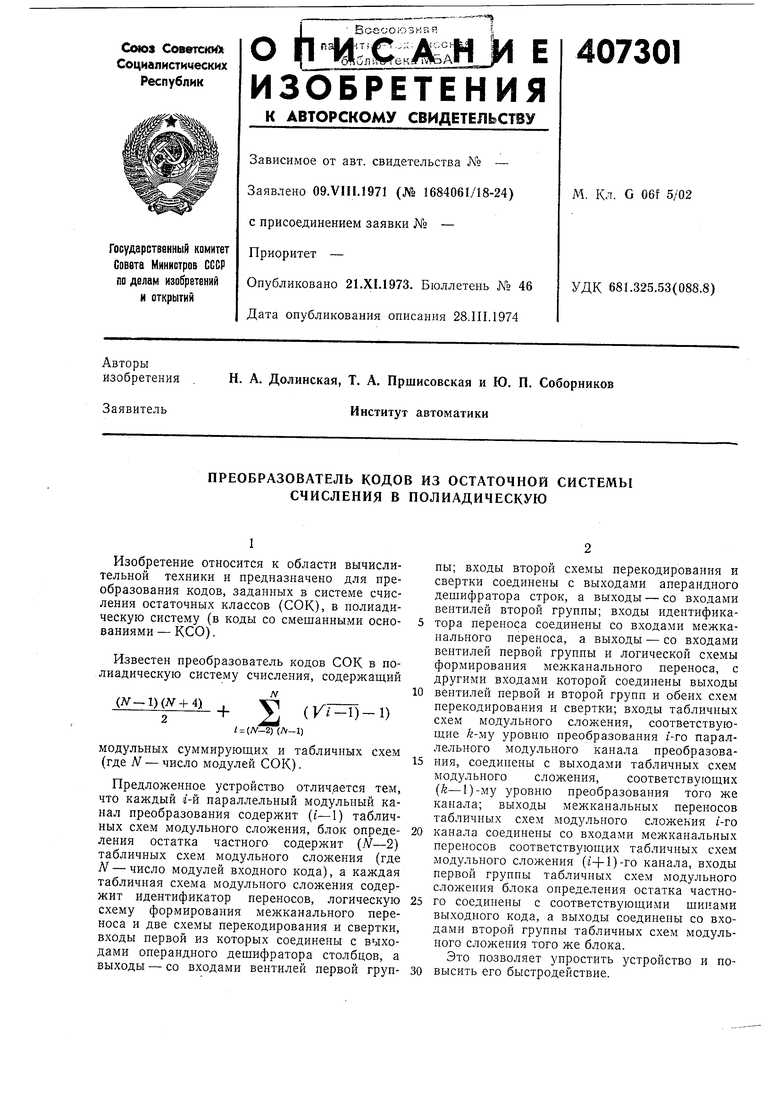

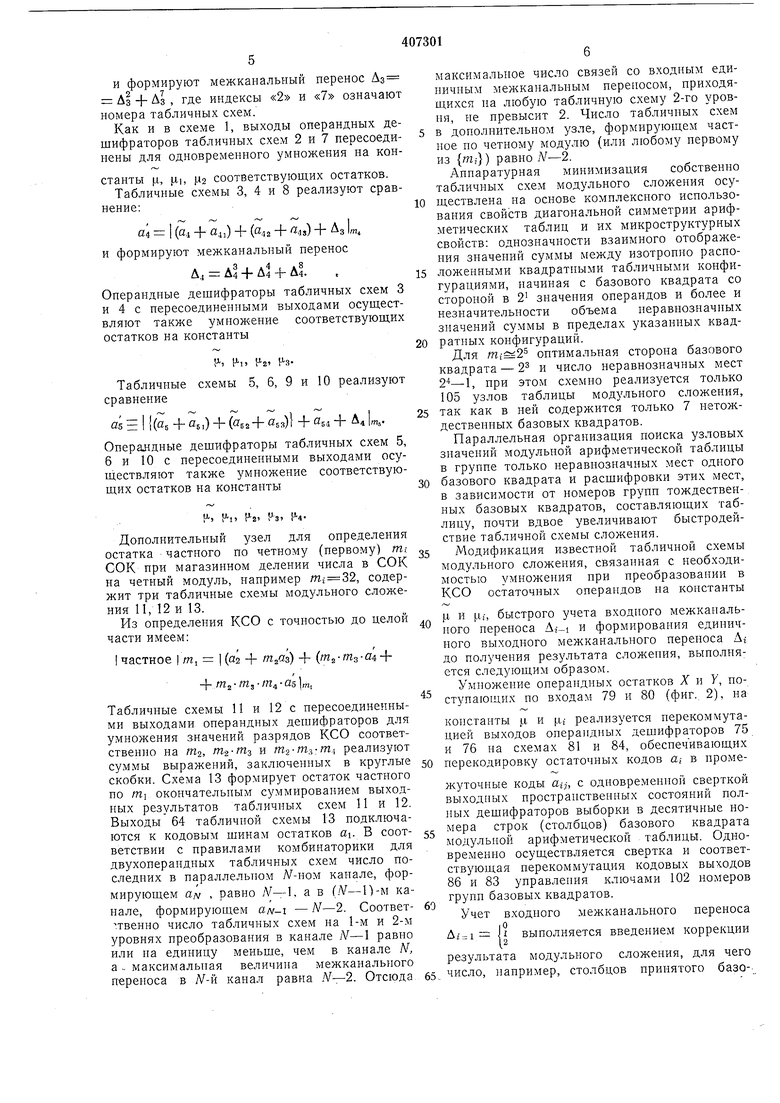

канала соединены со входами межканальных переносов соответствующих табличных схем модульного сложения ()-го канала, входы первой группы табличных схем модульного сложения блока определения остатка частного соединены с соответствующими шинами выходного кода, а выходы соединены со входами второй группы табличных схем модульного сложения того же блока. Это позволяет упростить устройство и повысить его быстродействие. Схема устройства для изображена на фиг. 1; на фиг. 2 изображена схема табличной схемы модульного сложения, а на фиг. 3 - временные диаграммы, поясняющие работу устройства. Устройство содержит (фиг. 1) табличные схемы 1 -13 модульного сложения, причем табличная схема 1 имеет входы 14, 15 и выходы 16, 17 и образует II параллельный модульный канал преобразования (для модуля m-i). Табличные схемы 2 и 7 имеют входы 18, 19, выходы 20,- 21 и входы 22, 23, 24, выходы 25, 26 соответственно и образуют III канал преобразования (для модуля /Пз). Табличные схемы 3, 4, 8 имеют входы 27, 28, 29, выходы 30, 31; входы 32, 33, выходы 34, 35; входы 36, 37, 38, выходы 39, 40 соответственвходы OD, д/, оо, ВЫХОДЫ оу, tu соитие с 1ьенно И образуют IV канал преобразования (для модулят4)Табличнь1е схемы 5-10 имеют Бходь 41, 42, вьтход 43; входьг 44, 45, вь1ход 46; входы 47-50, выход 51; входы 52, 53, 54, выход 55 соответственно и образуют V канал преобразования (для модуля ms). Табличные схемы 11, 12, 13 имеют входы 56, 57, выход 58; входы 59, 60, выход 61; входы 62, 63, выход 64 соответственно и образуют блок определения остатка частного (по первому, например, четному модулю СОК). Коды остатков а, а, аз, а, а СОК подаются по шинам 65-69 соответственно. Формируемые разряды аь «з, «з, а, QsKCO снимаются с шин 70-74 соответственно. Шины управляющих сигналов (УС) табличных схем модульного сложения на фиг. 1 не показаны. Каждая табличная схема модульного сложения содержит (фиг. 2) операндные дешифраторы строк 75 и столбцов 76 (принятого базового квадрата арифметической таблицы) . ., с выходами 77 и 78 соответственно, на которые подаются операндные остатки X и У по входам 79 и 80 соответственно; схему 81 перекодирования и свертки с выходами 82 и 83, схему 84 перекодирования и свертки с выходами 85 и 86; группы вентилей 87 и 88, ключи 89, формирователи 90; идентификатор переносов 91, со входами 92, 93 межканального переноса и выходами 94, 95, 96; логическую схему 97 формирования межканального переноса с выходом 98 межканального переноса; матрицу выборки 99 со схемами сборки 100, трансформаторной линейкой 101, ключами 102 и усилителями считывания 103; шину управляющих сигналов 104. В описании работы устройства приняты следующие формульные обозначения; nii - взаимно простые модули машинной СОК; i - порядковый номер модулей, остатков СОК и значений разрядов КСО; и; - остатки СОК; Ш -значения формируемых разрядов КСО; / - номера остатков СОК, участвующих в образовании значения t-ro разряда КСО; ац - промежуточные остаточные коды, составляющие значения разрядов 6 КСО по it-му и младшим (i-1,..., 1) модулям системы; Аг - выходной межканальный перенос из данного в последующий модуль; Аг-1 - входной межкаиальный перенос из предыдущего в данный модуль. Согласно известному алгоритму, значения разрядов КСО определяются сравнением: , / 0, 1,2..., г-1, 2«о- + а11 Ф(а, а,; ., i,,..., iA(i г:: const); Аг-1 -}- , i-z, i-i, i-z { i Схема собственно преобразователя для Л (Л1) содержит 10 табличных схем модульного сложения. Поскольку табличные схемы являются двухоперандными, то члены правой части для V разряда КСО можно сгруп F F пировать, например, следующим образом; 05 Е 1 I (Os + йя) + («52 + ««) } +«54+ 41,. Отсюда следует, что при однократном использовании каждой табличной схемы в цессе преобразования, максимальная глубина преобразователя при V-5 занимает триУровия. Однократное использование двухоперандных табличных схем позволяет учитывать А|0 входной межканальныи перенос Дг-i, г-2 ii непосредственно при табличной выборке результатов модульного сложения на 2-м и 3-м уровнях преобразования, а учет основного переноса Ai-i (переполнения по данному модулю) осуществлять в каждой табличной схеме (кроме схем V модуля) логическим формированием выходного межканального переноса Таким образом, общее число связей по входному межканальному переносу для V модульного канала достигает трех. Число таких связей для IV и III модульньи каналов .равно соответственно 2 и 1. Табличная схема 1 преобразователя реализует сравнение: 02 Е I «2 + 2I т,1 де .ii, а также формирует выходной межканальный перенос. Поскольку результат сложения образуется осредством адресной выборки (адреса - статочные коды операндов), можно совестить поиск суммы и умножение остатков а константы ц и ц, простым пересоедине выходов операндных дешифраторов абличной схемы. Табличные схемы 2 и 7 еализуют сравнение: «зЕ I(o3 + 3i) + за + Ajm,) и формируют межканальный перенос АЗ АЗ + Дз , где индексы «2 и «7 означают номера табличных схем. Как и в схеме 1, выходы операндных дешифраторов табличных схем 2 и 7 пересоединены для одновременного умножения на константы |д,, 11, На соответствующих остатков. Табличные схемы 3, 4 и 8 реализуют сравнение;«4 I (04 + a,} + ( + Я,,,) + Дз т, и формируют межканальный перенос Д Л4 + А4 + Д4. Операндные дешифраторы табличных схем 3 и 4 с пересоединенными выходами осуществляют также умножение соответствуюш,их остатков на константы 1, 2 -яТабличные схемы 5, 6, 9 и 10 реализуют сравнение аб Е I {(а, + «5,) + (052+053)1 + «54 + Д4 Im,Онерандные дешифраторы табличных схем 5, 6 и 10 с пересоединепными выходами осуществляют также умножение соответствующих остатков на константы И . Н-п . 4 Дополнительный узел для определения остатка частного по четному (первому) т,; СОК при магазинном делении числа в СОК на четный модуль, например тг 32, содержит три табличные схемы модульного сложения И, 12 и 13. Из определения КСО с точностью до целой части имеем: частное | т, : | (оз -f ) + (т -тз-а + т.,-т,, Табличные схемы 11 и 12 с пересоединенными выходами операндных дешифраторов для умножения значений разрядов КСО соответственно на т, и реализуют суммы выражений, заключенных в круглые скобки. Схема 13 формирует остаток частного по /П окончательным суммированием выходных результатов табличных схем И и 12. Выходы 64 табличной схемы 13 подключаются к кодовым шинам остатков а В соответствии с правилами комбинаторики для двухонерандных табличных схем число последних в параллельном yV-ном канале, формирующем a/v , равно .V-1, а в (V-П-м канале, формирующем UN-I - . Соответ твенно число табличных схем на 1-ми 2-м уровнях преобразования в канале /V-1 равно или на единипу меньше, чем в канале Л, а максимальная величина межканального переноса в канал равна N-2. Отсюда максимальное число связей со входным единичным межканальным переносом, приходящихся на любую табличную схему 2-го уровня, не превысит 2. Число табличных схем в дополнительном узле, формирующем частное по четному модулю (или любому первому из (nj)}) равно/V-2. Аппаратурная лшнимизация собственно табличных схем модульного сложения осуществлена па основе комплексного использования свойств диагональной симметрии арифметических таблиц и их микроструктурных свойств: однозначности взаимного отображения значений суммы между изотропно расположенными квадратными табличными конфигурациями, начиная с базового квадрата со стороной в 2 значения операндов и более и незначительности объема неравнозначных значений суммы в пределах указанных квадратных конфигураций. Для mtSE2 оптимальная сторона базового квадрата - 2 и число неравнозначных мест , при этом схемно реализуется только 105 узлов таблицы модульного сложения, так как в ней содержится только 7 нетождественных базовых квадратов. Параллельная организация поиска узловых значений модульной арифметической таблицы в группе только неравнозначных мест одного базового квадрата и расшифровки этих мест, в зависимости от номеров групп тождественных базовых квадратов, составляющих таблицу, почти вдвое увеличивают быстродействие табличной схемы сложения. Модификация известной табличной схемы модульного сложения, связанная с необходимостью умножения при преобразовании в КСО остаточных операндов на константы ц и ц,,-, быстрого учета входного межканального переноса Д, и формирования единичного выходного межканального переноса Д; до получения результата сложения, выполняется следующим образом. Умножение операндных остатков X и У, поступающих по входам 79 и 80 (фиг. 2), на константы J.I и |,ii реализуется перекоммутацией выходов операндных дешифраторов 75 и 76 на схемах 81 и 84, обеснечивающих перекодировку остаточных кодов О; в промежуточные коды aij, с одновременной сверткой выходных нространственных состояний полных дешифраторов выборки в десятичные номера строк (столбцов) базового квадрата модульной арифметической таблицы. Одновременно осуществляется свертка и соответствующая перекоммутация кодовых выходов 86 и 83 управлепия ключами 102 номеров групп базовых квадратов. Учет входного межканального переноса Ь выполняется введением коррекции результата модульного сложения, для чего исло, например, столбцов принятого базового квадрата увеличивается на максимальную величину . Тогда при выборе по операндпым кодам столбца и строки базового квадрата можно произвести одновременное изменение номера столбца на +Ai-i и в силу свойств модульной таблицы сложения получить тождественное приращение результата.

Входы 92, 93 мел капального нерепоса Лг-i связаны с идентификатором 91, выходы которого 96 (Дг-1 0), 95 () и 94 (A,-i 2) подключены к управляющим входам группы вентилей 88; с дрзгими входами тех же вентилей связаны соответствующие выходные цепи 85 .схемы 84, чем обеспечивается возбуждение (А+1)-го либо )-ro формирователя 90 (если операндными кодами без учета входного переноса должен быть выбран k-E формирователь);, общее число их в табличной схеме увеличивается на max(A,--i). То же максимальное приращение получит число входов в координатно-узловых элементах матрицы выборки 99, определяющей номер состояния (для /n;,2 уже не 15, а 17 состояний), выбранного в расщиренном базовом квадрате. В основу формирования табличной схемой выходного межканального переноса положено свойство модульной таблицы сложения, в которой непосредственно ниже побочной диагонали лежат остатки суммы, полученные однократным исключением значения данного модуля, что и учитывается как единичный перенос в следующий модульный канал преобразования. Учет каждой единицы входного межканального переноса (из предыдущего модульного канала), естественно, вызывает единичный сдвиг вниз от диагональной границы между областями 0-го и 1-го значения выходного межканального переноса.

Логическая схема 97 формирования выходного межканального переноса представляет собой сборку элементов типа «И-ИЛИ-НЕ. Учет входного межканального переноса при окончательном выборе столбца расщиренного базового квадрата отражается введением цепей связи между логической схемой 97 и выходами групп вентилей 87 и 88. Учет сдвига диагоцальной границы арифметической таблицы, обусловленного входным межканальным нереносом, реализуется с помощью связей логической схемы 97 с идептификатором переносов 91 по цепям 96, 95 и 94. Выход 98 служит для связи логической схемы 97 с одним из входов 92, 93 идентификатора 91 в табличпой схеме следующего модульного канала.

Процесс целочисленного нреобразования из СОК в KCiQ реализуется параллельно по N модульным каналам (фиг. 1). Так как значения ui и Oi совпадают, табличные схемы в канале I (mi) отсутствуют.

С целью сокращения запаздывания на преобразование, работа устройства организована с уплотнением времени, учитывающим реальпые задержки формирования и прохождения канальных сигналов по каскадным соединениям табличных схем.

Параллелизм канального нреобразования обеспечивается при условии, что межканальный неренос поступает на вход соответствующей табличной схемы одновременно с суммируемыми операндами a,j. Это достигается разнесением во времени сигналов внещней синхронизации преобразователя с учетом запаздывания на формирование сумм и межканальных переносов в табличных схемах. В собственно преобразователе (фиг. 1) используется .пять управляющих сигналов внешней синхронизации, следующих через временные интервалы т (запаздывание на формирование табличной схемой выходного межканального переноса).

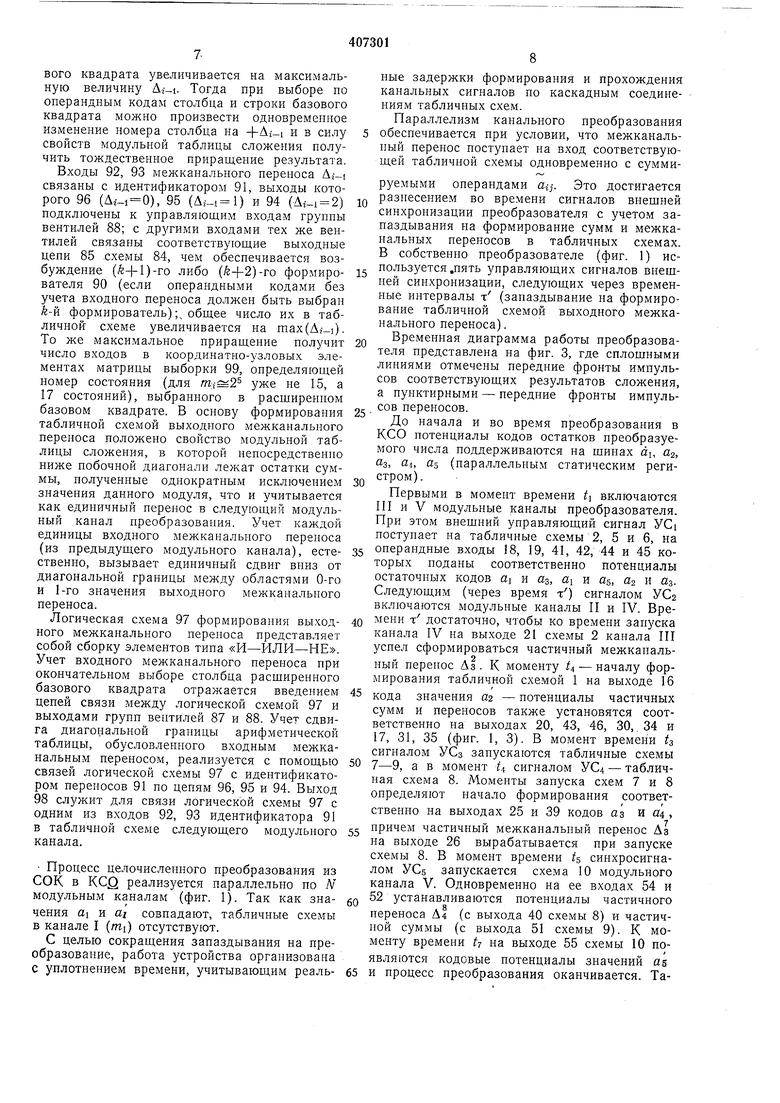

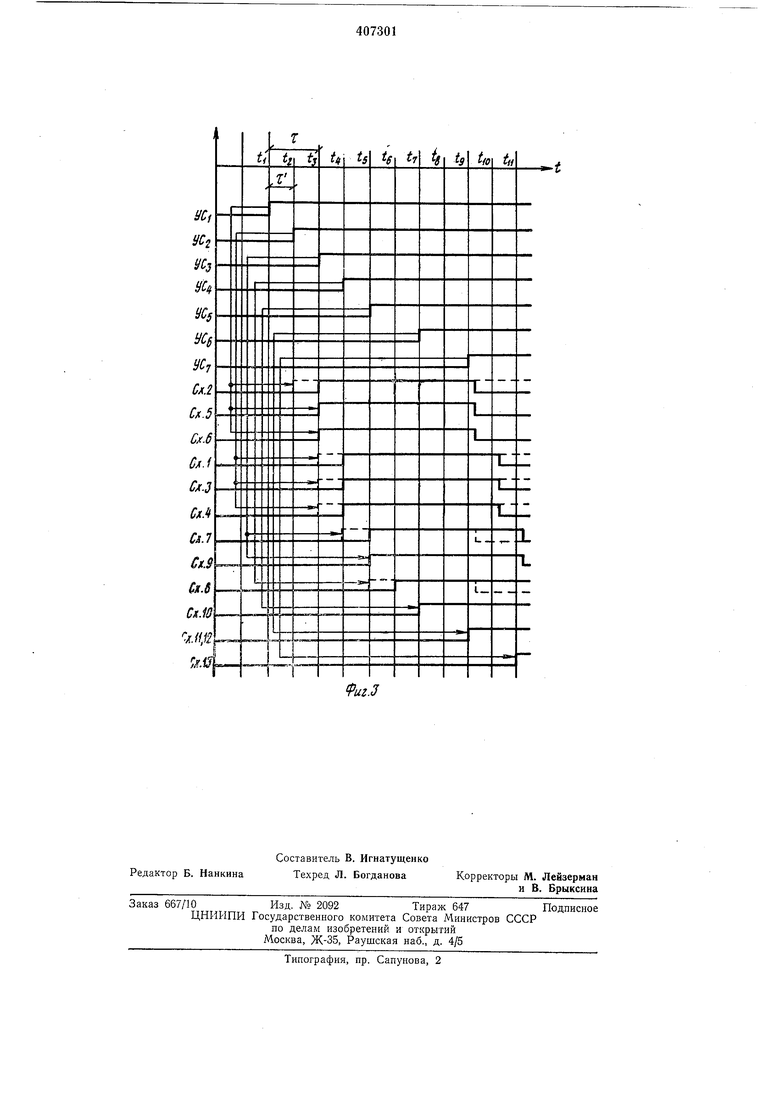

Временная диаграмма работы преобразователя представлена на фиг. 3, где сплошными линиями отмечены передние фронты импульсов соответствующих результатов сложения, а нунктирными - передние фронты импульсов переносов.

До начала и во время преобразования в КСО потенциалы кодов остатков преобразуемого числа поддерживаются на щинах dj, 02, «3, flb Й5 (параллельным статическим регистром).

Первыми в момент времени tj включаются III и V модульные каналы преобразователя. При этом внещний управляющий сигнал УС: поступает на табличные схемы 2, 5 и 6, на операндные входы 18, 19, 41, 42, 44 и 45 которых поданы соответственно потенциалы остаточных кодов а и аз, Ci и as, az и аз. Следующим (через время т ) сигналом УС2 включаются модульные каналы Пи IV. Времени т достаточно, чтобы ко времени запуска канала IV на выходе 21 схемы 2 канала III успел сформироваться частичный межкапальо

ный перенос Аз . К моменту /4 - началу формирования табличной схемой 1 на выходе 16 кода значения й2 - потенциалы частичных сумм и переносов также установятся соответственно на выходах 20, 43, 46, 30,. 34 и 17, 31, 35 (фиг. 1, 3). В момент времени ts сигналом УСз запускаются табличные схемы 7-9, а в момент t. сигналом УС4 - табличная схема 8. Моменты запуска схем 7 и 8 определяют начало формирования соответственно на выходах 25 и 39 кодов аз и 04 ,

7 причем частичный межканальныи перенос Аз

на выходе 26 вырабатывается при запуске схемы 8. В момент времени 5 синхросигналом УСб запускается схема 10 модульного канала V. Одновременно на ее входах 54 и 52 устанавливаются потенциалы частичного переноса А4 (с выхода 40 схемы 8) и частичной суммы (с выхода 51 схемы 9). К моменту времени 7 на выходе 55 схемы 10 появляются кодовые нотенциалы значений ад и процесс преобразования оканчивается. ТаКИМ образом, общее запаздывание предложенного преобразователя из СОК в КСО при составляет . Потенциалы кодов al, й2, аз, щ, as КСО, поступающие на соответствующие щины, могут в дальнейщем запоминаться на статическом регистре. Полученные значения разрядов КСО используются и при магазинном делении остаточного представления числа А на первый модуль СОК (например, четный) для определения остаточного представления частного Л по этому модулю: - с помощью блока 1 Wl из схем и 12 и 13 (фиг 1) При подаче в момент /у сигнала УСв на схемы И и 12 на их выходах 58 и 61 в момент 9 будут сформированы коды частичных суии |а2+mj-aslffZi Im -ms-a - -mz-tn -m -aslm 20 соответственно. Последние складываются к моменту 11 в синхронизируемой УС/ схеме 13, на выходе 64 которой и образуется Табличная схема модульного сложения в процессе преобразования функционирует следующим образом. Наличие операндных кодов J и У на вхо-30 дах 79 и 80 приводит в соответствующее активное состояние дещифраторы 75 и 76 (фиг. 2), на единственном выходе каждого из которых появляется потенциал. Через диоды схем 81 и 84 перекодирования и свертки ко-35 дов потенциалы по цепям, 82, 85 поступают на входы групп вентилей 87, 88 соответственно. Потенциал па выходе одного из вентилей 88 появляется в случае одновременного воздействия управляющего сигнала УС по цепи40 104 и потенциала корректировки результата на величину входного переноса по одной из цепей 96, 95 или 94. На входах ключей 89 потенциал запуска появляется при совпадеНИИ УС и выходного потенциала схемы 81,45 воздействующего по цепи 82. Потенциалы, запускающие своим передним фронтом выбранные ключ 89 и формирователь 90, поступают также на входы элементов совпадения логической схемы 97 форми-50 рования межканального переноса. На другие входы указанных элементов совпадения соответственно по цепям 86 и 83 через схемы 84 и 81 перекодирования и свертки поступают выходные потенциалы дещифраторов 76 и 7555 и по цепям 96, 95 или 94 с идентификатора 91-потенциал входного межканального переноса. Одновременное воздействие указанных потенциалов на входы логической схемы 97 вызывает появление (через время т после60 УС) на ее выходной щине 98 сформированного сигнала выходного межканального переноса. При этом потенциал на одной из щин 96, 95 или 94, соответствующий значению входного межканального переноса «О, 25 или «2, предварительно вырабатывается схемами совпадения в идентификаторе 91 (из сигналов выходного межканального переноса предыдущего модульного канала, поступаюЩ х по входам 92, 93). Выходные потенциалы схем перекодирова«ия и свертки кодов поступают по кодовым шинам 86 и 83 групп номеров базовь1х квадРатов на входную логику ключей 102. Таким образом, параллельно с выбором ключа 89 и формирователя 90 осуществляется и выбор ключа группы базовых квадратов с тождественными узловыми значениями. На выходе координатно-узлового элемента матрицы 99, общего для включенных схем 89 и 90, возни«ает токовый импульс, а единственным из ключей 102 к общей земляной щине предварительно подключен только один из диодов сборки 100, связанный с выходом выбранного элемента матрицы 99, в только по одному из кодовых проводов трансформаторной линейки 101 пройдет импульсный ток. Кодовые сигналы выбранного таким образом табличного результата модульного сложения со вторичных обмоток кодовых трансформаторов липейки 101 поступают параллельно на входы усилителей считывания 103, на выходных щинах которых через время от момента подачи УС появляются сформированные (по амплитуде и длительности) кодовые сигналы результата модульной операции, Предмет изобретения Преобразователь кодов из остаточной системы счисления в полиадическую, содержащий блок определения частного и параллельные модульные каналы преобразования, выполненные на табличных схемах модульного сложения, каждая из которых содержит операндные дещифраторы строк и столбцов, матрицу выборки со схемами сборки, трансформаторной линейкой, усилителями считывания и ключами, формирователи, входы которых соединены с выходами вентилей первой группы, а выходы - с первой группой входов матрицы выборки, ключи, входы которых соедийены с выходами вентилей второй группы, а выходы -- со второй группой входов матрицы выборки, отличающийся тем, что, с целью упрощения устройства и повыщення его быстродействия, каждый i-й параллельный модульный канал преобразования содержит (i-1) табличных схем модульного сложения, блок определения остатка частного содержит (N-2) табличных схем модульного сложения (где ЛГ -число модулей входного кода), а каждая табличная схема модульного сложения содержит идентификатор переносов, логическую схему формирования межканального переноса и две схемы перекодирования и свертки, входы первой из которых соединены с выходами операндного дещифратора столбцов, а выходы - со входами вентилей первой группы, входы второй схемы

перекодирования и свертки соединены с выходами операндного дешифратора строк, а выходы - со входами вентилей второй групиы, входы идентификатора переноса соединены со входами межканального переноса, а выходы - со входами вентилей первой группы и логической схемы формирования межканального переноса, с другими входами которой соединены выходы вентилей первой и второй групп и обеих схем перекодирования и свертки, входы табличных схем модульного сложения, соответству1ОН1ие й-му уровню преобразования г-го параллельного модульного канала преобразования, соединены с выхода407301

12

ми табличных схем модульного сложения, соответствующих (k-1)-му уровню преобразования того же канала, выходы межканальных переносов табличных схем модульного

сложения t-ro канала соедииены со входами межканальных переносов соответствующих табличных схем модульного сложения (f-j-l)-ro канала, входы первой группы табличных схем модульного сложения блока

определения остатка частного соединены с соответствующими щииами выходного кода, а выходы соединены со входами второй группы табличных схем модульного сложения того же блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Табличный сумматор-вычислитель в системе остаточных классов | 1971 |

|

SU446056A1 |

| Табличное устройство для модульного умножения в системе остаточных классов | 1971 |

|

SU550636A1 |

| Арифметическое устройство в системе остаточных классов | 1973 |

|

SU549805A1 |

| Побайтный преобразователь из двоичного в двоично-кодированное остаточное представление | 1972 |

|

SU437067A1 |

| Многокоординатная система числового программного управления | 1972 |

|

SU448435A1 |

| Арифметическое устройство в системе остаточных классов | 1981 |

|

SU999050A1 |

| Устройство для сложения в системе остаточных классов | 1984 |

|

SU1160408A1 |

| Устройство для умножения в системе остаточных классов | 1978 |

|

SU922731A1 |

| Преобразователь кода из системы остаточных классов в позиционный код | 1978 |

|

SU744549A1 |

| Цифровой фильтр | 1988 |

|

SU1617635A1 |

с,б.. ai66 741 Ч hi- 56 57 59 60 Фиг. Si T/l (риг.2

Авторы

Даты

1973-01-01—Публикация