Изобретение относится к автоматике и вычислительной технике и может быть использовано в специализированных вычислительных устройствах повышенной надежности. Известно устройство, выполненное на одноразрядных сумматорах и логическом элементе ИЛИ-НЕ 1. Недостатком устройства является неоднородность входящих в него элементов и существенное усложнение при увеличении числа входв. Известно также устройство, содер жащее логические элементы И и ИЛИ и выполненное в виде матрицы с числом строк и столбцов, равным числу источников входных сигналов, составлен ной из однотипных ячеек, содержащих элемент И, подключенный к первому входу элемента ИЛИ, причем выход эле мента ИШ, расположенного в i-й стро ке, J-M столбце матрицы, соединен в 1-й строке,:(J+1)-м столбце и первым входом элемента И, расположенного в (±+1)-й строке, (J+I)-M столб це, вторые входы элементов И, расположенных в J-M столбце, подключены к j-му источнику входного сигнала, а первые входы-элементов И, расположенных в первой строке, подключены к источнику управляющего сигнала . Недостатком устройства является его сложность. Цель изобретения - упрощение устройства мажоритарного элемента. Поставленная цель достигается тем, что мажоритарньгй элемент выполнен в виде многоступенчатого сумматора с числом ступеней суммирования равным Z , i-ая ступень которого (,,..,2 ) состоит из i-разрядных сумматоров, при этом входные сигналы подключены к первому и второму входу сумматоров первой ступени суммирования, а также к входам переноса сумматоров всех ступеней суммирова-ния, выходы суммы сумматоров первой ступени суммирования подключены . к первому и второму входам сумматоров второй ступени суммирования, а выхо-ды переноса сумматоров.первой ступени суммирования подк.пючены к третьему и четвертому входам сумматоров второй ступени суммированич, причем (2.-j)-й выход (,...., ,-) сум-мы сумматора С- ой ступени суммирования подключен и (28-2j-1) -му входу выходного сумматора, выход

переноса сумматора: t-ой ступени суммирования подключен к (2 и +1)-му входу выходного сумматора, (22 -2j)-bje входы и (2В +2)-ый вход которого подключен к источнику управляющего сигнала, а выход переноса выходнрго сумматора подключен к выходу устройства.

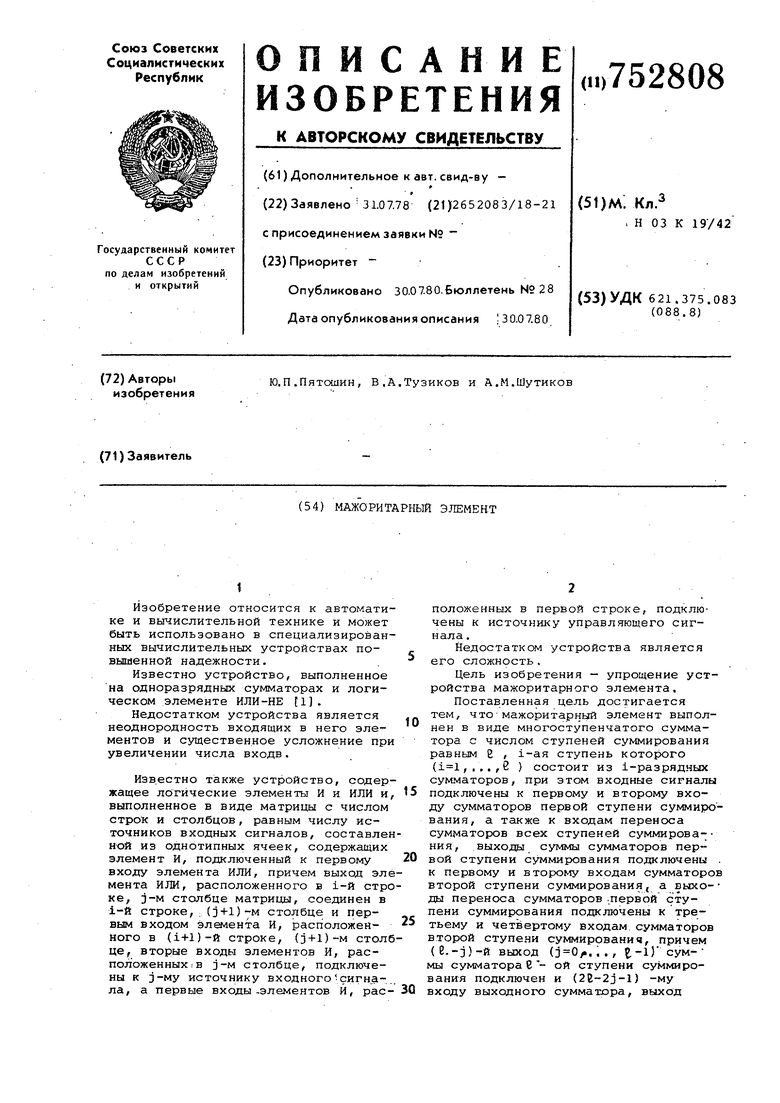

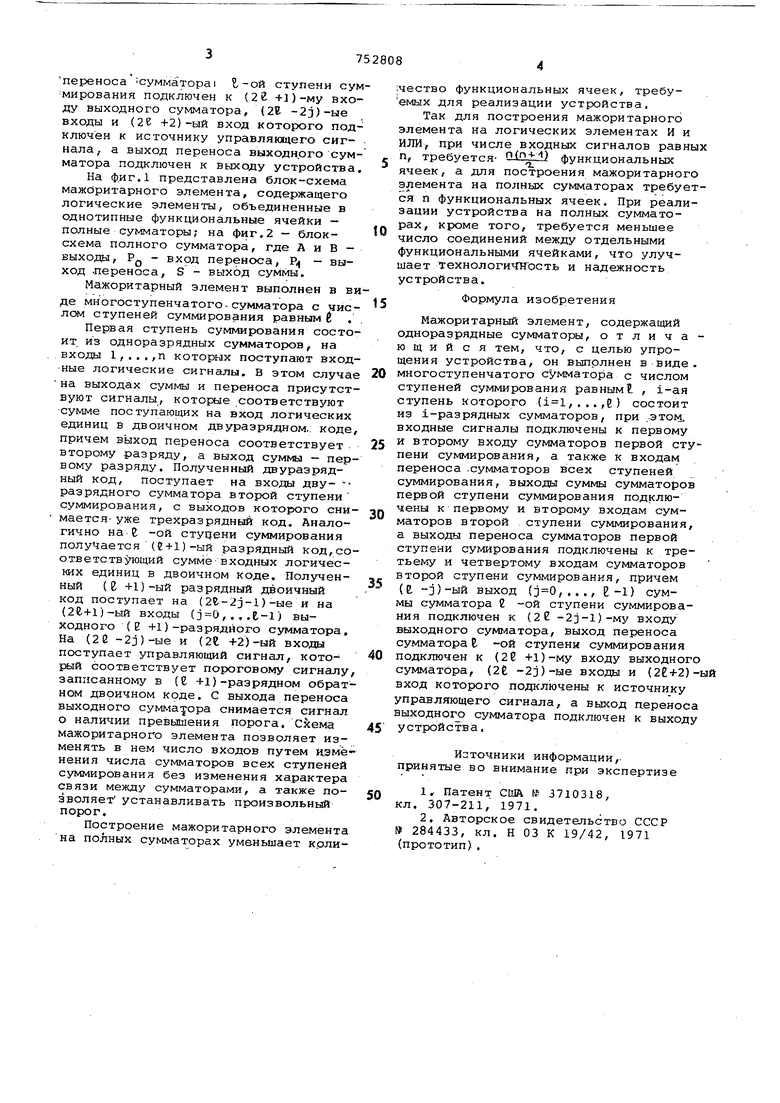

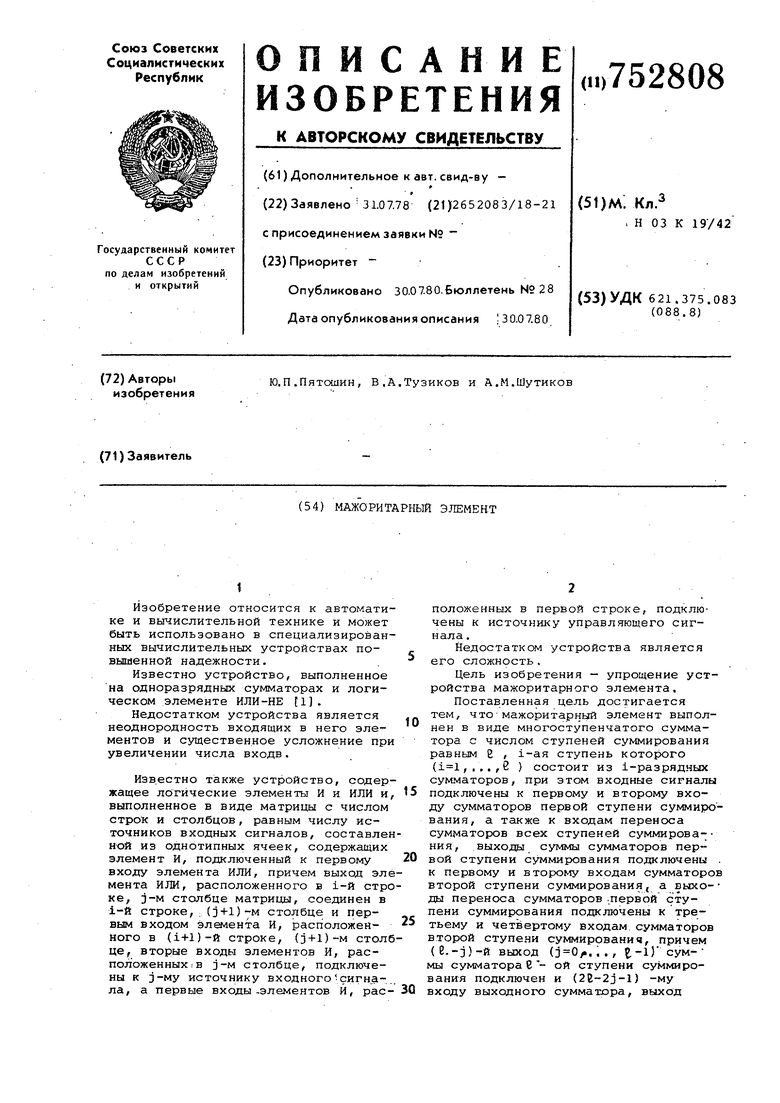

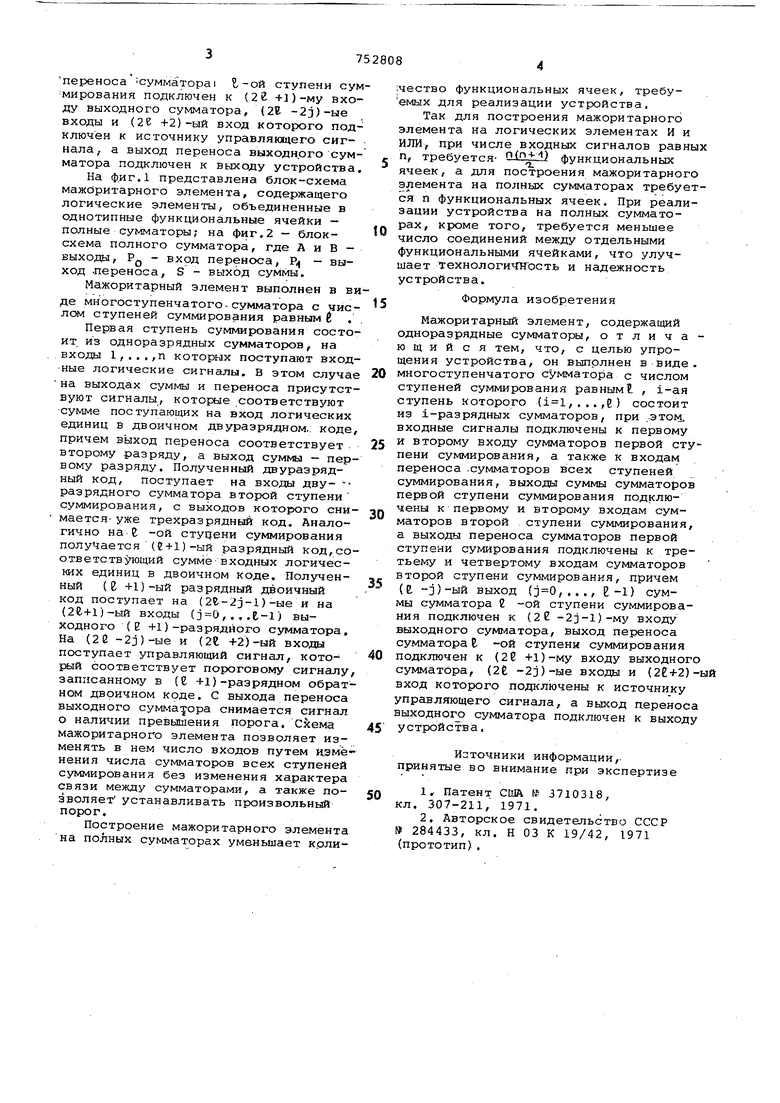

На фиг.1 представлена блок-схема мажоритарного элемента, содержащего логические элементы, объединенные в однотипные функциональные ячейки - полные сумматоры; на фиг.2 - блоксхема полного сумматора, где А и В - выходы, PQ - вход переноса, Р - выход -переноса, S - выход суммы.

Мажоритарный элемент выполнен в виде многоступенчатого- сумматора с числом ступеней суммирования равным б .

Первая ступень суммирования состоит из одноразрядных сумматоров, на входы 1, . . . ,п которых поступают входные логические сигналы. В этом случае на выходах суммы и переноса присутствуют сигналы, которые соответствуют сумме поступающих на вход логических единиц в двоичном двуразрядном., коде, причем выход переноса соответствует, второму разряду, а выход сумьм - первому разряду. Полученный двуразрядный код, поступает на входы дву- разрядного сумматора второй ступени суммирования, с выходов которого снимается- уже трехразрядный код. Аналогично на С -ой стуцени суммирования получается (5+1)-ый разрядный код,соответств пощий сумме-входных логических единиц в двоичном коде. Полученный (и +1)-ый разрядный двоичный код поступает на ()-ыe и на (2е.+1)-ый входы (, .. .t-l) выходного (Е +1)-разрядйого сумматора. На (212 -2j)-ыe и (21 +2)-ый входы поступает управляющий сигнал, который соответствует пороговому сигналу записанному в (С +1)-разрядном обратном двоичном коде. С выхода переноса выходного cyMMajopa снимается сигнал о наличии превышения порога. Схема мажоритарного элемента позволяет изменять в нем число входов путем и.змёнения числа сумматоров всех ступеней суммирования без изменения характера связи между сумматорами, а также позволяет устанавливать произвольный порог.

Построение мажоритарного элемента на полных сумматорах уменьшает крли;чество функциональных ячеек, требуемых для реализации устройства.

Так для построения мажоритарного элемента на логических элементах И и ИЛИ, при числе входных сигналов равны п, требуется- П,) функциональных ячеек, а для построения мажоритарного элемента на полных сумматорах требуется п функциональных ячеек. При реализации устройства на полных сумматорах, кроме того, требуется меньшее число соединений между отдельными функциональными ячейками, что улучшает технологичВость и надежность устройства.

Формула изобретения

Мажоритарный элемент, содержащий одноразрядные сумматоры, отличающий с я тем, что, с целью упрощения устройства, он выполнен в виде . многоступенчатого сумматора с числом ступеней суммирования равным. , i-ая ступень которого (,,..,8) состоит из 1-разрядных сумматоров, при .этом. входные сигналы подключены к первому и второму входу сумматоров первой ступени суммирования, а также к входам переноса .сумматоров всех ступеней суммирования, выходы суммы сумматоров первой ступени суммирования подключены к первому и второму входам сумматоров второй ступени суммирования, а выходы переноса сумматоров первой ступени сумирования подключены к третьему и четвертому входам сумматоров второй ступени суммирования, причем (I -j)-ый выход (,..., Е-1) суммы сумматора 2 -ой ступени суммирования подключен к (22 -2j-l)-My входу выходного сумматора, выход переноса сумматора t -ой ступени суммирования подключен к (2С -fl)-My входу выходного сумматора, (2Е -2j)-He входы и ()вход которого подключены к источнику управляющего сигнала, а выход переноса выходногр сумматора подключен к выходу устройства,

Маточники информации,, принятые во внимание при экспертизе

1,Патент США № 3710318, кл. 307-211, 1971.

2.Авторское свидетельство СССР 284433, кл. Н 03 К 19/42, 1971

(прототип),

CM

ч:

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ КОНВЕЙЕРНОГО СУММИРОВАНИЯ ЧИСЕЛ ПО ПРОИЗВОЛЬНОМУ МОДУЛЮ | 2023 |

|

RU2805939C1 |

| Матричное устройство для возведения в квадрат и извлечения квадратного корня | 1983 |

|

SU1107119A1 |

| Матричное устройство для возведения в квадрат и извлечения квадратного корня | 1983 |

|

SU1111155A1 |

| Матричное вычислительное устройство | 1982 |

|

SU1034032A1 |

| Устройство для умножения | 1989 |

|

SU1688238A1 |

| Пороговый логический элемент | 1981 |

|

SU1005317A1 |

| Вычислительное устройство | 1982 |

|

SU1164697A1 |

| ОДНОРОДНАЯ ВЫЧИСЛИТЕЛЬНАЯ СРЕДА ДЛЯ КОНВЕЙЕРНЫХ ВЫЧИСЛЕНИЙ СУММЫ M N-РАЗРЯДНЫХ ЧИСЕЛ | 2012 |

|

RU2486576C1 |

| Устройство для умножения с накоплением | 1986 |

|

SU1310810A1 |

| Матричное устройство для деления | 1985 |

|

SU1247863A1 |

м 3

фиг. 2

Авторы

Даты

1980-07-30—Публикация

1978-07-31—Подача