L .. 1

Г Изобретение относится к области ц 1фровой коммутационной техники и мЬжет быть использовано в устройст- многоканальной коммутации с запоминанием управляющих программ. Цель изобретения - расширение

соответствующей входной шине 8 комму-. татора, а стоки каждого из МДП-тран- зисторов 5 коммутационных элементоЕ 3 в каждом столбце матрицы подклю- 5 чены к соответствующей выходной шине 9 столбца, число которых в столбце также равно К.

Выходное устройство 2 выбора содержит М групп по К элементов 2 И 1C 10 в каждой, первые входы которых в каждой группе объединены и подключены к соответствующим шинам I1 выбора столбца. Вторые входы одноименных элементов 2И всех групп объединены

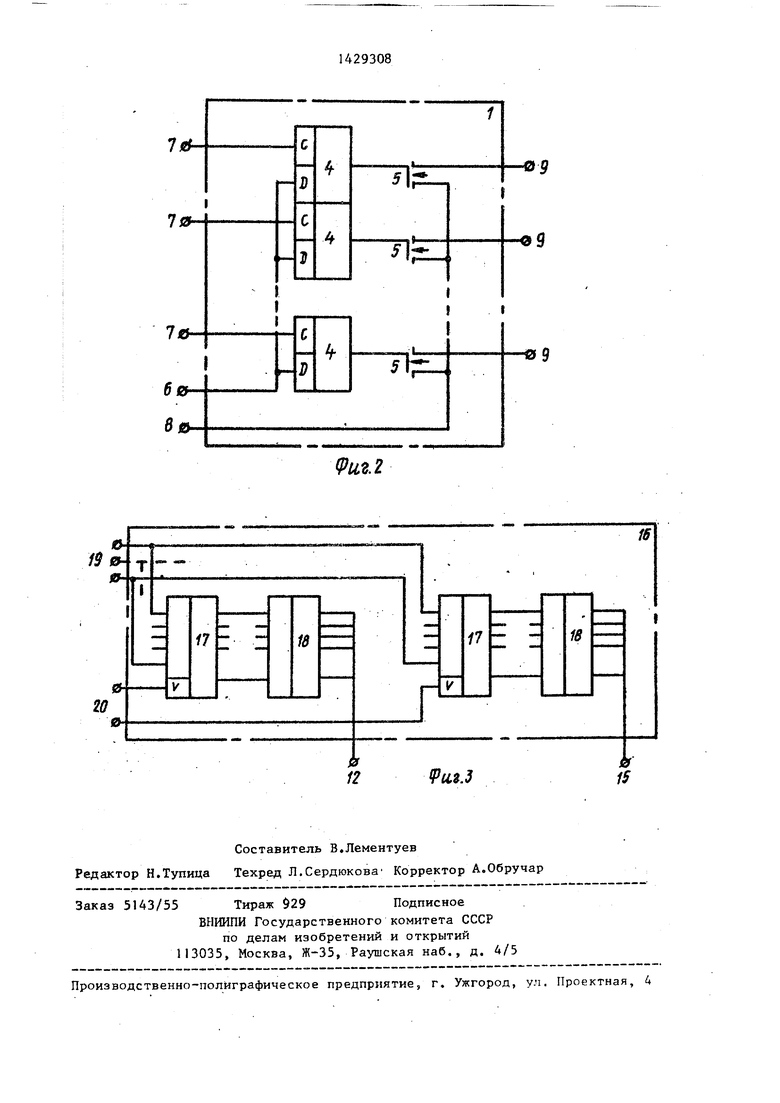

ункциональных возможностей и увеличение производительности коммутатора путем введения входного и, вькодного устройств выбора, а также введения в коммутационный элемент матрицы . дополнительных запоминающих и .комму- ти|рзтощих элементов, благодаря которым переход от одного, состояния матрицы к другому осуществляется за один15 и подключены к соответствующим вход- та|кт с возможностью сохранения ий- ным шинам 12 настройки. Выходное формации о предьщущем состоянии, вы устройство 3 выбора содержит М логи- бор программы настройки осуществля- ческих элементов Кх2И/ИЛИ 13, выхо- ется произвольно, а сама настройка ды которых подключены к выходным ши- производится во время работы коммута-20 нам 14 коммутатора. Первые входы од- тора по одной из программ настройки ноименных элементов 2И всех М логиНа фиг.1 приведена функциональная схема матричного коммутатора; на фиг.2 - принципиальная схема коммуческих элементов 13 объединены и подключены к соответствующим выходньи шинам 15 настройки, число которых

тадаонного элемента; на фиг.З - прин- также равно К. Вторые входы техжеэлесоответствующей входной шине 8 комму-. татора, а стоки каждого из МДП-тран- зисторов 5 коммутационных элементоЕ 3 в каждом столбце матрицы подклю- чены к соответствующей выходной шине 9 столбца, число которых в столбце также равно К.

Выходное устройство 2 выбора содержит М групп по К элементов 2 И 10 в каждой, первые входы которых в каждой группе объединены и подключены к соответствующим шинам I1 выбора столбца. Вторые входы одноименных элементов 2И всех групп объединены

и подключены к соответствующим вход- ным шинам 12 настройки. Выходное устройство 3 выбора содержит М логи- ческих элементов Кх2И/ИЛИ 13, выхо- ды которых подключены к выходным ши- нам 14 коммутатора. Первые входы од- ноименных элементов 2И всех М логических элементов 13 объединены и подключены к соответствующим выходньи шинам 15 настройки, число которых

также равно К. Вторые входы техжеэле

| название | год | авторы | номер документа |

|---|---|---|---|

| Матричное коммутационное устройство | 1986 |

|

SU1385286A2 |

| Матричное коммутационное устройство | 1988 |

|

SU1598145A1 |

| Коммутационное устройство | 1985 |

|

SU1307572A1 |

| Матричное коммутационное устройство | 1982 |

|

SU1075409A1 |

| Матричный коммутатор | 1985 |

|

SU1274143A1 |

| Матричный коммутатор | 1985 |

|

SU1275753A1 |

| Коммутационное устройство | 1985 |

|

SU1307573A1 |

| Многоканальный фотометр | 1987 |

|

SU1492224A1 |

| Коммутатор | 1977 |

|

SU738162A1 |

| МНОГОКАНАЛЬНЫЙ КОММУТАТОР | 1991 |

|

RU2026605C1 |

Изобретение относится к цифровой коммутационной технике и может быть использовано в устройствах многоканальной коммутации с запомина нием управляющих программ. Целью :- изобретения является расширение функциональных возможностей и увеличение производительности коммутатора. Для достижения поставленной цели в устройство, содержащее-матрицу коммута- ционнйх элементов I, каждый из которых содержит К триггеров и МДП-тран- зисторов, дополнительно введены входное 2 и выходное 3 устройства выбора, а в каждый коммутационный элемент 1 введено дополнительно (К-2-) D-триггера и (К-1) МДП-транзисторов. При этом входное устройство выбора содержит М групп по К элементов 2И 10, а выходное устройство выбора со г ( (Л с

цйпиальная схема блока управления.

Матричный коммутатор содержит матрицу NxM коммутационных элементов 1, входное 2 и выходное 3 устройства выбора.

Коммутационный .элемент I содержит К D -триггеров 4 .и соответствующее число МДП-транзисторов 5. D-входы D-триггеров 4 объединены и подключены к соответствующей шине 6 выбора строки, а выходы - к затворам соответствующих МДП-транзисторов 5. С-вх ды lD-триггеров 4 подключены к соот- ветйтвующим входным шинам 7 столбца, число которых в каждом столбце равно числу D-триггеров в каждом коммутационном элементе 1, т.е. равно К. Истоки МДП-транзисторов 5 в каждой строке объединены и подключены к

ментов 2И каждого из М логических элементов 13 подключены к соответст- вз ющин вьЕкодньм шинам 9 столбца. Блок 16 управления содержит два

О параллельных регистра 17 и два дешифратора 18. Входы регистров 17 подключены к шинам 19 номера матрицы, |а выходы - к входам дешифраторов 18. Число входов и выходов регистров 17.

35 и дешифраторов 18 равно . Выходы дешифраторов 18 образуют по К входных и выходных шин 12 и 15 настройки. Входы разрешения записи в регистры 17 подключены к командным

40 входам 20.

Коммутатор работает следующим образом.

В режиме настройки в регистр 17 записывается код коммутации. Для

этого на шины 19 номера матрицы подается двоич ый код, а на один из командных входов 20 - сигнал разрешения. При этом одна из К входных шин 12 настройки переходит в единичкое состояцие. Этот сигнал открывает в кпжд,ой группе элементов 2И 10 один из элементов 2И, разрешая прох.ожде- :-ше сигк, выбора -птолбца с шин 1J на входные шины столбца. С помощью этого 9игнала и сигнала с шины 6 выбора строки в один из К триггеров данного столбца записывается логичес||| ti

а в остальные - логическая

кий О.

Таким образом, устанав;швается с оединение с помощью МДП-транзисто ра 5 одной из входных шин 6 строки с одной из выходных шик 9 столбца Данная процедура повторяется К раз для каждой строки матрицы.

В режиме передачи во второй параллельный регистр 17 также записывается нбмер коммутационной матрицы, через которую будет осуществляться передача коммутируемьк сигналов. При этом одна из К выходных шин 15 настройки переходит в единичное COQ- тояние, что .позволяет передать сигнал логической 1 с соответствующег D-триггера 4 коммутационного элемента 1 через один и К элементов 2И логического элемента 13 на выходную шину 14 коммутатора.

Таким образом, в режиме передачи реализуется только одна из К комбинаций коммутации. Переход к другой комбинации коммутирующихся шин 8 и 14 осуществляется за один такт путем изменения кода на шинах 19 номера матрицы. При этом информация о соединениях в других комбинациях коммутации сохраняется, возможно повторное обращение через любое число тактов. Настройка матрицы на коммутацию в новой комбинации шин 8 .и 14 может осуществляться одновременно с режи- . мом передачи.

Формула изобретения 1. Матричный коммутатор, содержащий матрицу NxM коммутационных элементов, каждый из которых содержит два D-триггера и МДП-транзистор, исток которого соединен с входной шиной данной строки, а з.атвор подключен к выходу первого D-триггера, отличающийся тем, что, с целью расширения функциональных

5

0

возможностей и увеличения производительности коммутатора; в него , вя еде- :ы входное и вькодное устройств л выбора, а в кажп.ьш коммутационный элемент дополнителько введены (К-2) D- григгеров и (К-1) ЗДП-транзисторов, затвор каждого из которых соединен с выходом соответствующего D-триггера, включа уже имеющийся П-трит - гер, а истоки которых соединены с входной шиной соответствующей строки, D-входы всех триггеров коммутационных элементов данной строки подключены к соответствующей шине выбора данной строки, входное устройство выбора содержит М групп по К элементов 2И в каждой, первые входы элементов 2И в каждой группе объединены и подключены к соответствующей шине выбора столбца, вторые входы одноименных элементов 2И всех групп объединены и подключены к соответствующим вход- ным шинам настройки, число которых

5 также равно К, выходы К элементов 2И каждой группы подключен) к соот- ветствующ1-м входным шинa столбца, каждая из которых соединена с С-вхо- дом одного из К В триггеров коммутационных элементов данного столбца, выходное устройство выбора содержит М логических элементов Кх2И/ИЛИ, выходы которых подключены К выходным шинам коммутатора, причем первые входы одноименных элементов 2Й всех М логических элементов Кх2И/ИЛИ объединены и подключены к соответствующим выходным шинам настройки, число которых также равно К, а вторые входы тех же элементов 2И каждого из М логических элементов Кх2И/ИЛИ подключены к соответствующим выходным шинам столбца, каясдая из которых соединена со штоками соответ ствующих МДП-транзисторов коммутационных элементов данного столбца, причем К равно или больше двух.

g и подключены к шинам номера матрицы, число которых равно lop.K, а входы :разрешения записи в параллельные регистры соединены с соответствующими командными входами.

5

0

0

(Риг.2

| Матричное коммутационное устройство | 1982 |

|

SU1075409A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Матричный коммутатор | 1983 |

|

SU1102038A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1988-10-07—Публикация

1987-01-13—Подача