Предлагаемое устройство относится к области вычислительной техники.

Известны распределители импульсов, выполненные на потенциальных триггерах и логических элементах «И, «ИЛИ, «НЕ.

Известный распределитель с тержит большое число v oгичecкиx элементов типа «И. «ИЛИ, «НЕ, а надежность его работы в некоторой степени зависит от длительности импульсов тактовой частоты и выходных импульсов распределителя.

Предложенный распределитель отличается тем, что в нем одип из каналов тактовой частоты подключен ко входам элементов «И, предназначенных для выработки п-го и 2 л-го импульсов распределителя, вторые входы указанных элементов соединены с единичным н нулевым выходами вспомогательного триггера, единичный вход которого подключен к (п-1)-й выходной шине, а нулевой вход его соединен с (2п-1)-й выходной шиной, при этом единичный и нулевой входы коммутируюш,его триггера подключены к п-й и 2п-й выходным шинам соответственно (где п - число триггеров регистра).

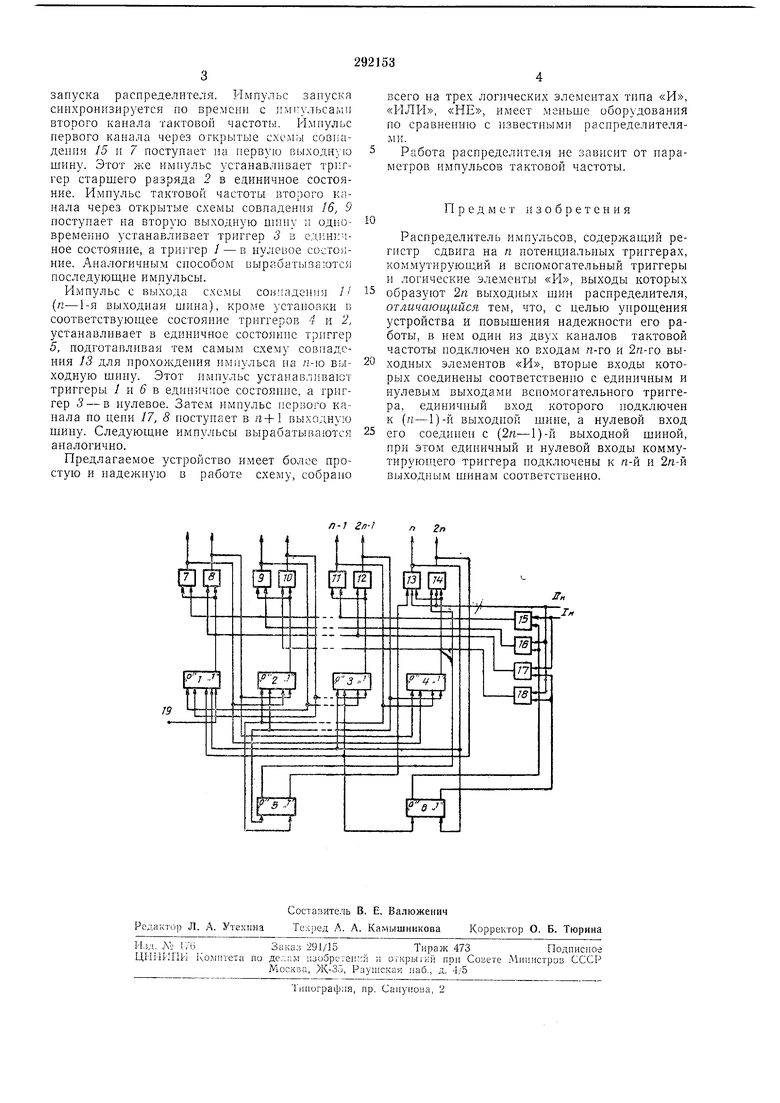

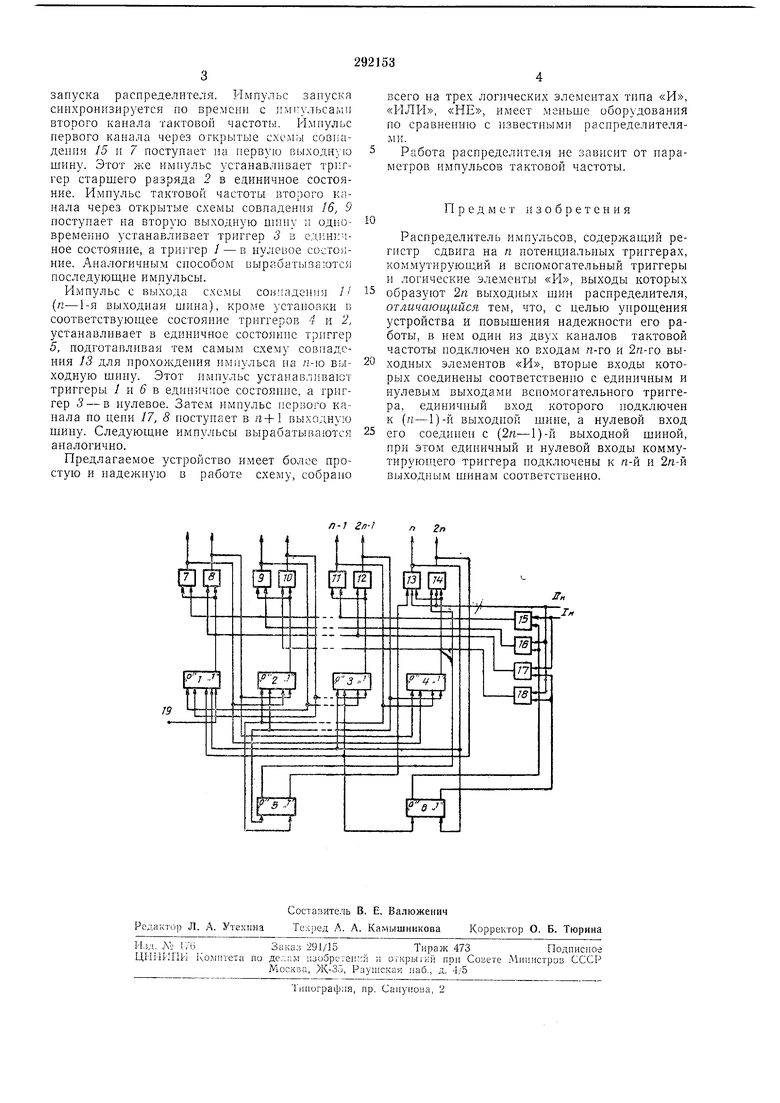

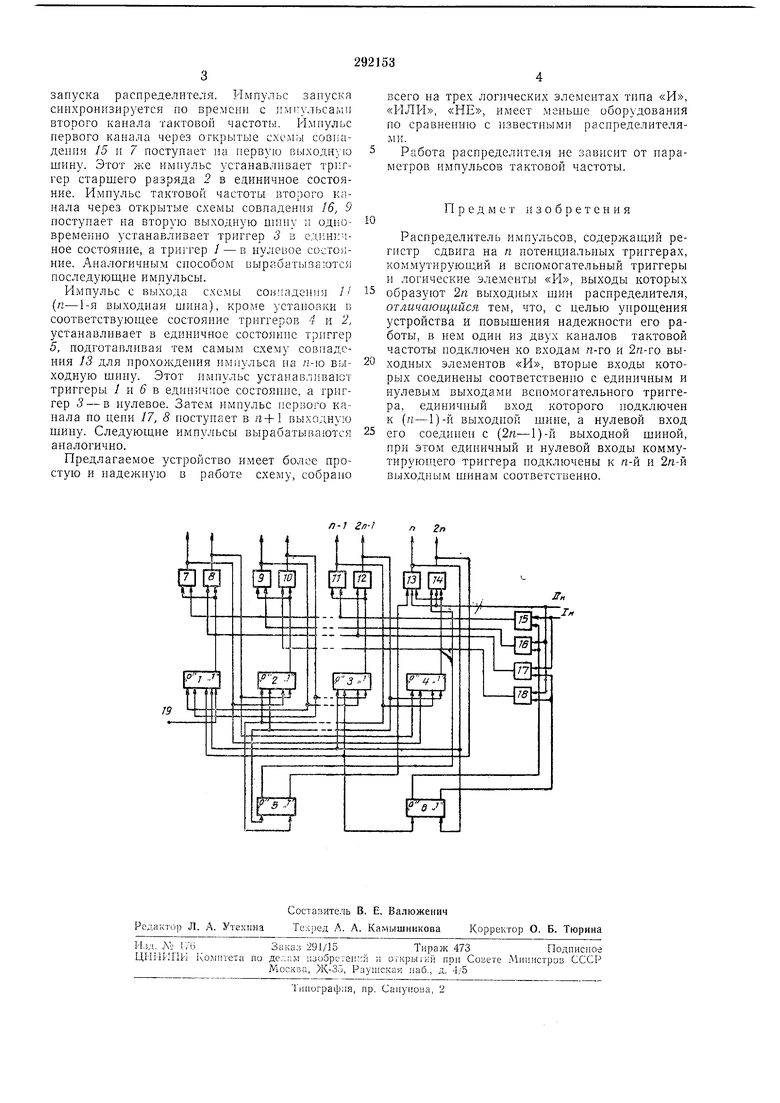

На чертеже приведена функциональная схема предлагаемого распределителя импульсов.

Он содержит триггеры /-4 регистра, вспомогательный триггер 5, коммутируюший триггер 6, логические элементы «И (схемы совпадения) /-18 и шину 19 включения распределителя.

Шпна тактово; частоты второго канала подключена ко входам схем совпадения 13 и

14. Вторые входы этих схем соединены с единичным и нулевым выходами триггера 5. Единичный вход триггера 5 подключен к (п-1)-й выходной шине, а его нулевой вход соединен с (2п-1)-й лыходпой шиной. Нулевой вход

триггера 6 подключен к 2/;-й выходной шине, а его единичный вход связан с п-й выходной шиной. Нулевой и единичный выходы триггера 6 соединены с входами схем совпадения 15, 16 и 17, 18 соответственно. Вторые входы

схем совпадения /5 и 17 соединены с шиной первого канала тактовой частоты, вторые входы схем соЕладеипя 16 и 18 - с шиной второго канала тактовой частоты. Каждая выходная шина распределителя

подключена к единичному входу триггера старшего разряда и к нулевому входу триггера младшего разряда. Шина 19 включения распределителя подключена к единичному входу триггера L

В исходном состоянии триггеры /-6 установлены в нулевое состояние. На выходных шинах распределителя (выходы схем совпадспия 7-14) нет сигналов.

запуска распределителя. Импульс запуска синхронизируется по временп с лмпульсаып второго канала тактовой частоты. 11.мпульс первого канала через открытые схемы совиадепии 15 и 7 поступает иа первую выходную шину. Этот же имиульс устанавливает тритгер старшего разряда 2 в единичное состояние. Импульс тактовой частоты второго канала через открытые схемы совпадения 16, 9 поступает на вторую выходную шппу и одновременно устанавливает триггер 3 в е;|, состояние, а триггер 1 - в нулевое состояние. Аналогичным способом вырабатываются последующие импульсы.

Импульс с выхода схемы соимаденпя / (п-1-я выходная шина), кроме установки в соответствующее состояние триггеров 4 и 2, устанавливает в единичное состояние триггер 5, подготавливая тем самым схему совпадения 13 для прохождения импульса на /г-ю выходную шину. Этот импульс устанавл1 вают триггеры 1 II 6 ъ еднпичиое состояиис, а триггер 3 - в нулевое. Затем импульс первого канала по цепи 17, 8 иостуиает в u-f 1 выходную щину. Следующие импульсы вырабатываются аналогично.

Предлагаемое устройство имеет более простую и надежную в работе схему, собрано

всего на трех логических элементах тина «И, «ИЛИ, «НЕ, имеет .меньше оборудования по сравнепию с известными распределителями.

Работа распределителя не зависит от параметров импульсов тактовой частоты.

Предмет изобретения

Распределитель импульсов, содержащий регистр сдвига на п потенциальных триггерах, коммутируюидий и вспомогательный триггеры и логические элементы «И, выходы которых

образуют 2« выходных щин распределителя, отличающийся тем, что, с целью упрощения устройства и повышения наделшости его работы, в нем один из двух каналов тактовой частоты подключен ко входам п-го и 2п-го выходных элементов «И, вторые входы которых соединены соответственно с единичным и нулевым выходами вспомогательного триггера, единичиый вход которого подключен к (гг-1)-й выходной щине, а нулевой вход

его соединен с (2я-1)-й выходной щиной, при этом единичный и нулевой входы коммутирующего триггера подключены к п-й и 2/г-й выходным шинам соответственно.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для суммирования несколь-КиХ чАСТОТ C ОпОРНОй чАСТОТОй | 1979 |

|

SU819922A1 |

| РАСПРЕДЕЛИТЕЛЬ ИМПУЛЬСОВ | 1970 |

|

SU262490A1 |

| Устройство для контроля коммутирующей среды | 1972 |

|

SU440667A1 |

| @ -Канальный распределитель | 1983 |

|

SU1166292A1 |

| Устройство для вычисления элементарных функций | 1984 |

|

SU1168930A1 |

| Трехканальный двухрежимный распределитель импульсов для управления шаговым двигателем | 1980 |

|

SU907753A1 |

| Распределитель | 1983 |

|

SU1088123A1 |

| УСТРОЙСТВО для МОДЕЛИРОВАНИЯ ВЕРОЯТНОСТНОГО | 1970 |

|

SU280064A1 |

| Цифровой измеритель временного положения середины видеоимпульсов | 1990 |

|

SU1718148A1 |

| Функциональный преобразователь | 1982 |

|

SU1100621A1 |

п-} гп-1

Даты

1971-01-01—Публикация