(54) УСТРОЙСТВО ДЛЯ СУММИРОВАНИЯ НЕСКОЛЬКИХ ЧАСТОТ С ОПОРНОЙ ЧАСТОТОЙ

делителя импульсов, выход первой схемы совпадения подключен ко входу S основного триггера, выход которого соединен с одним из вхидов логической схемы и одним входом второй схемы совпадения, другой вход которой подключен к 21-ому выходу распределителя импульсов и второму входу логической схемы, третий вход которой подключен к (2i + l)-OMy выходу, распределителя импульсов, выход второй схемы совпадения соединен со входом R вспомогательного триггера S, вход которого образует вход i-ой частоты, вход R основного триггера подключен к (21+2)-ому выходу распределителя импульсов, а выход логической схемы, каждого канала суммирования подключен к одному из входов схемы ИЛИ.

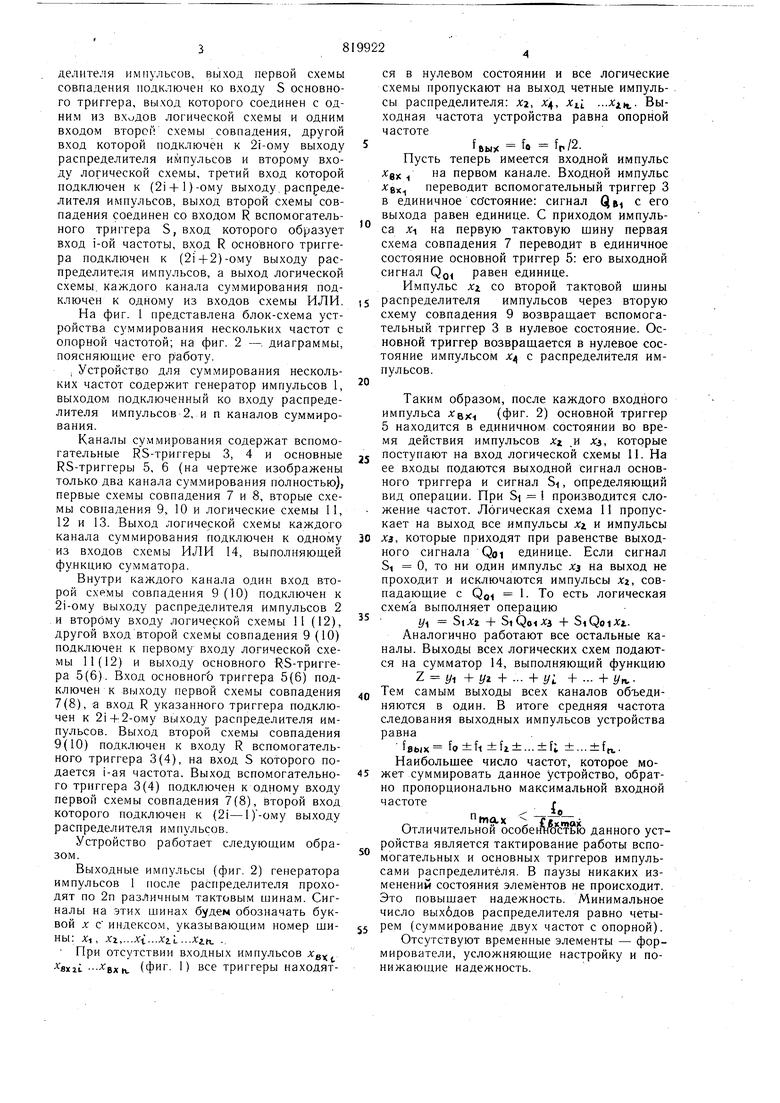

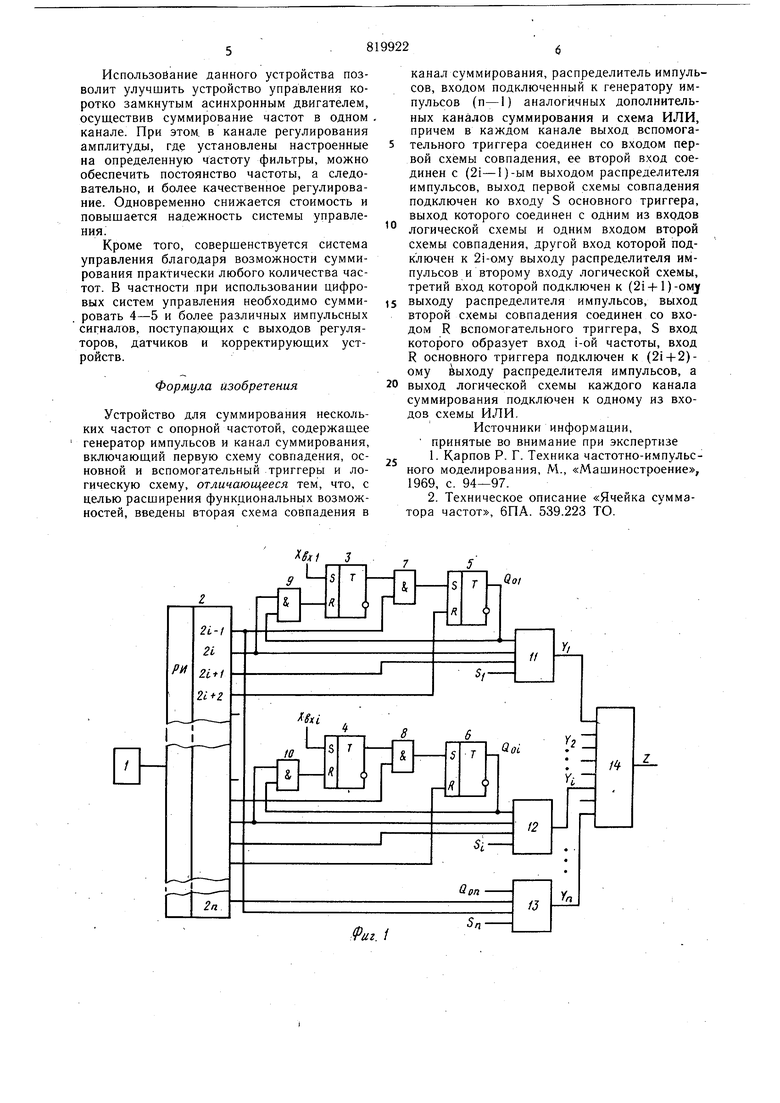

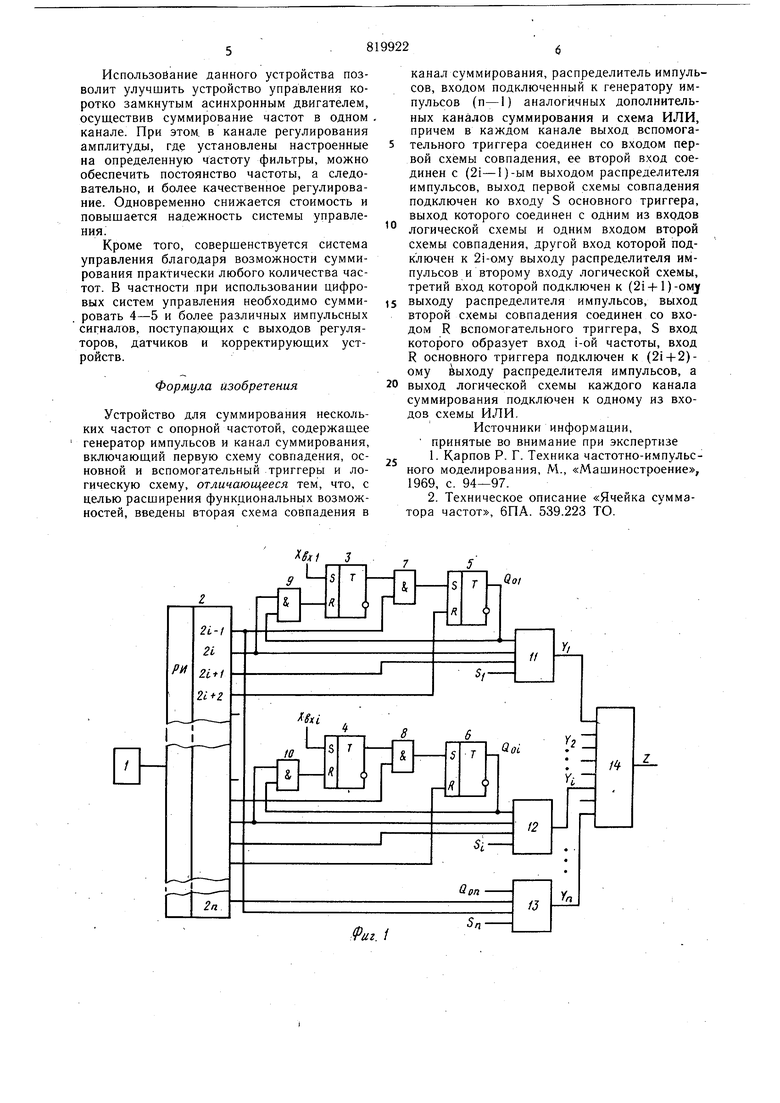

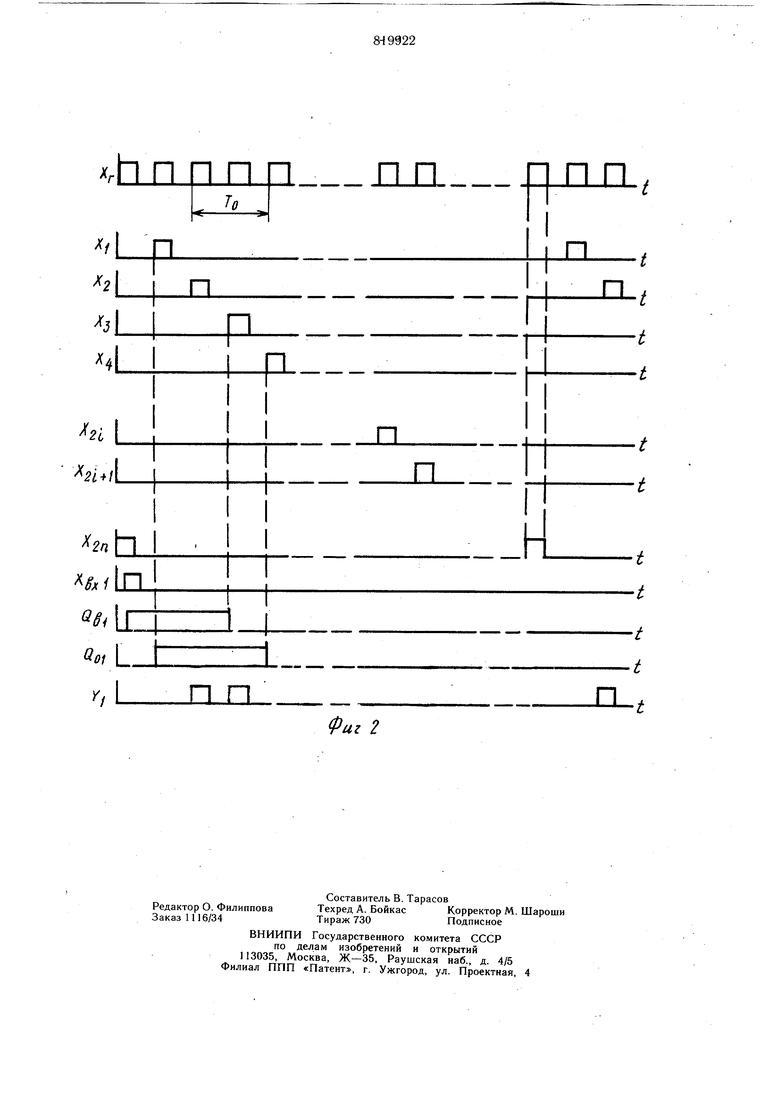

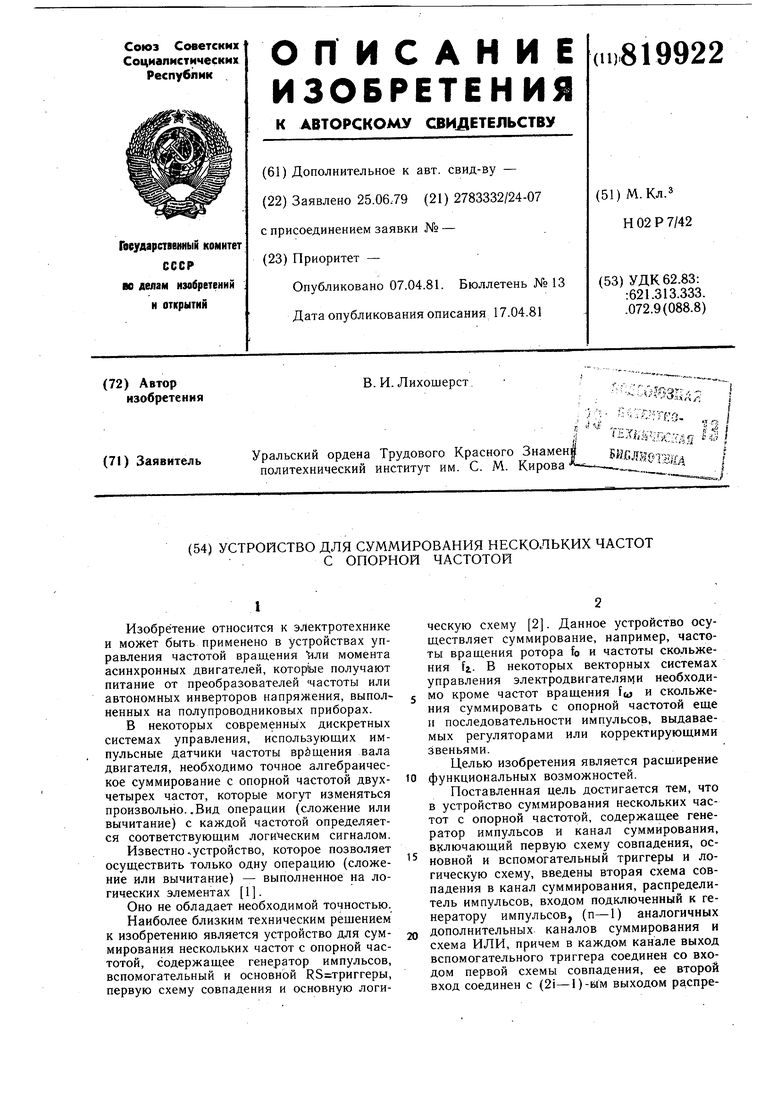

На фиг. 1 представлена блок-схема устройства суммирования нескольких частот с олорной частотой; на фиг. 2 -. диаграммы, поясняющие его работу.

Устройство ДЛЯ суммирования нескольких частот содержит генератор импульсов 1, выходом подключенный ко входу распределителя импульсов 2, и п каналов суммирования.

Каналы суммирования содержат вспомогательные RS-триггеры 3, 4 и основные RS-триггеры 5, 6 (на чертеже изображены только два канала суммирования полностью), первые схемы совпадения 7 и 8, вторые схемы совпадения 9, 10 и логические схемы II, 12 и 13. Выход логической схемы каждого канала суммирования подключен к одному из входов схемы ИЛИ 14, выполняюш,ей функцию сумматора.

Внутри каждого канала один вход второй схемы совпадения 9(10) подключен к 2i-OMy выходу распределителя импульсов 2 .и второму входу логической схемы 11 (12), другой вход второй схемы совпадения 9(10) подключен к первому входу логической схемы 11(12) и выходу основного RS-триггера 5(6). Вход основногЬ триггера 5(6) подключен к выходу первой схемы совпадения 7(8), а вход R указанного триггера подключен к 21-1-2-ому выходу распределителя импульсов. Выход второй схемы совпадения 9(10) подключен к входу R вспомогательного триггера 3(4), на вход S которого подается i-ая частота. Выход вспомогательного триггера 3(4) подключен к одному входу первой схемы совпадения 7(8), второй вход которого подключен к (21-1)-ому выходу распределителя импульсов.

Устройство работает следуюш.им образом.

Выходные импульсы (фиг. 2) генератора импульсов 1 после распределителя проходят по 2п различным тактовым шинам. Сигналы на этих шинах будем обозначать буквой X с индексом, указывающим номер шины: Х-1 , Xi,...X-i...X2.l...Xin ..

При отсутствии входных импульсов Хд exii. (фиг. 1) все триггеры находятся в нулевом состоянии и все логические схемы пропускают на выход четные импульсы распределителя: Х2, х/(, ...Xit.- Выходная частота устройства равна опорной частоте

fo fp/2.

6ЫХ

Пусть теперь имеется входной импульс Xg на первом канале. Входной импульс й переводит вспомогательный триггер 3 в единичное состояние: сигнал QB с его выхода равен единице. С приходом импульса x-i на первую тактовую шину первая схема совпадения 7 переводит в единичное состояние основной триггер 5: его выходной сигнал QQJ равен единице.

Импульс Xi со второй тактовой шины распределителя импульсов через вторую схему совпадения 9 возвращает вспомогательный триггер 3 в нулевое состояние. Основной триггер возвращается в нулевое состояние импульсом х с распределителя импульсов.

Таким образом, после каждого входного импульса .TBXI (фиг. 2) основной триггер 5 находится в единичном состоянии во время действия импульсов хг. ,и хз, которые , поступают на вход логической схемы 11. На ее входы подаются выходной сигнал основного триггера и сигнал Si, определяющий вид операции. При Sj производится сло. жение частот. Логическая схема 11 пропускает на выход все импульсы Xi и импульсы 0 хз, которые приходят при равенстве выходного сигнала Qoi единице. Если сигнал S, О, то ни один импульс хз на выход не проходит и исключаются импульсы xi, совпадающие с Qo 1. То есть логическая схема выполняет операцию

i/1 Si.X2 -Ь SiQoi.AJ3 + SiQoi.x:i. Аналогично работают все остальные каналы. Выходы всех логических схем подаются на сумматор 14, выполняющий функцию

2 У1 + г/2 + ... + У1 + ... + Уп,. Тем самым выходы всех каналов объединяются в один. В итоге средняя частота следования выходных импульсов устройства равна

fo±fi±fi±...±fi ±...±f. Наибольшее число частот, которое мо5 жет суммировать данное устройство, обратно пропорционально максимальной входной частотег

п/ в

)c

Отличительной особентюстью данного устройства является тактирование работы вспомогательных и основных триггеров импульсами распределителя. В паузы никаких изменений состояния элементов не происходит. Это повышает надежность. Минимальное число выхбдов распределителя равно четырем (суммирование двух частот с опорной).

Отсутствуют временные элементы - формирователи, усложняющие настройку и понижающие надежность.

Использойание данного устройства позволит улучшить устройство управления коротко замкнутым асинхронным двигателем, осуществив суммирование частот в одном канале. При этом, в канале регулирования амплитуды, где установлены настроенные на определенную частоту фильтры, можно обеспечить постоянство частоты, а следовательно, и более качественное регулирование. Одновременно снижается стоимость и повышается надежность системы управления.

Кроме того, совершенствуется система управления благодаря возможности суммирования практически любого количества частот. В частности при использовании цифровых систем управления необходимо суммировать 4-5 и более различных импульсных сигналов, поступающих с выходов регуляторов, датчиков и корректирующих устройств.

Формула изобретения

Устройство для суммирования нескольких частот с опорной частотой, содержащее генератор импульсов и канал суммирования, включающий первую схему совпадения, основной и вспомогательный триггеры и логическую схему, отличающееся тем, что, с целью расщирения функциональных возможностей, введены вторая схема совпадения в

канал суммирования, распределитель импульсов, входом подключенный к генератору импульсов (п-1) аналогичных дополнительных каналов суммирования и схема ИЛИ, причем в каждом канале выход вспомогательного триггера соединен со входом первой схемы совпадения, ее второй вход соединен с (21-1)-ым выходом распределителя импульсов, выход первой схемы совпадения подключен ко входу S основного триггера, выход которого соединен с одним из вхддов

логической схемы и одним входом второй схемы совпадения, другой вход которой подключен к 2i-OMy выходу распределителя импульсов и второму входу логической схемы, третий вход которой подключен к (2i-bl)-OMjf

выходу распределителя импульсов, выход второй схемы совпадения соединен со входом R вспомогательного триггера, S вход которого образует вход i-ой частоты, вход R основного триггера подключен к (2i + 2)ому ыходу распределителя импульсов, а

выход логической схемы каждого канала суммирования подключен к одному из входов схемы ИЛИ.

Источники информации, принятые во внимание при экспертизе

1.Карпов Р. Г. Техника частотно-и.мпульсного моделирования, М., «Машиностроение, 1969, с. 94-97.

2.Техническое описание «Ячейка сумматора частот, бПА. 539.223 ТО.

Фи1 2

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство суммирования частот | 1990 |

|

SU1705824A1 |

| Устройство для измерения частоты | 1985 |

|

SU1292162A1 |

| Устройство для сравнения частот | 1982 |

|

SU1083335A1 |

| Устройство для управления регулятором переменного напряжения со звеном повышенной частоты | 1985 |

|

SU1347112A1 |

| Измеритель частоты | 1989 |

|

SU1691768A1 |

| Устройство для раздельного управления реверсивным тиристорным преобразователем | 1987 |

|

SU1503055A1 |

| Синтезатор частот | 1984 |

|

SU1293841A1 |

| Трехфазный преобразователь частоты | 1985 |

|

SU1319193A1 |

| Устройство для определения момента равенства двух частот | 1984 |

|

SU1201778A1 |

| УСТРОЙСТВО ОБНАРУЖЕНИЯ СИГНАЛОВ С ПРОГРАММНОЙ ПЕРЕСТРОЙКОЙ РАБОЧЕЙ ЧАСТОТЫ | 1997 |

|

RU2110890C1 |

Авторы

Даты

1981-04-07—Публикация

1979-06-25—Подача