подключен к входу сброса третьего триггера и к первому входу генератора одиночных импульсов, вход начального запуска преобразователя соединен с входом второго коммутатора, выход которого подключен к второму входу генератора одиночных импульсов, выход которого соединен с информационным входом третьего коммутатора, первый выход которого подключен к входу установки третьего триггера, вход задания состояния преобразоват й ЬоДключен к управляющему входу т ётьего коммутатора, отличающийся тем, что, с целью повышения точности, в него введены вычитатель, второй регистр аргумента и четвертый элемент ИЛИ, а в блок управления введены двухразрядный распределитель импульсов, восьмой элемент И и второй элемент задержки, причем первый выход двухразрядного распределителя импульсов блока управления соединен с первым входом пятого элемента И и вторым входом третьего элемента И, третий вход которого подключен к выходу второго регистра сдвига и информационному входу первого регистра сдвига, выход которого соединен с первым входом вычитатепя, второй вход которого подключен к выходу третьего элемента И, а выход вычитателя соединен с информационным вхрдом второго регистра сдви.га и с вторым входом первого коммутатора, вход управления которого подключен к входу задания режима преобразователя, вход данных первого регистра сдвига соединен с

прямым выходом третьего триггера блока управления, входы управления и данных второго регистра сдвига подключены к шине нулевого потенциала преобразователя, выход первого ре-гистра аргумента соединен с вторым входом пятого элемента И, выход которого подключен к первому входу третьего элемента ИЛИ, выход которого соединен с вторым входом блока сравнения, первый и второй выходы которого подключены соответственно к первому и второму входам четвертого элемента ИЛИ, вьЬсод которого соединен с вторым входом четвертого элемента И, выходы п -р&зрядного распределителя импульсов блока управления подключены к входам второго регистра аргумента, выход которого соединен с первым входом шестого элемента И, выход которого подключен к второму входу третьего элемента ИЛИ, второй выход двухразрядного распределителя импульсов блока управления соединен со вторым входом шестого элемента И,при этом в блоке управления выход последнего разряда П-разрядного распределителя импульсов со1единен с входом двухразрядного распределителя импульсов и первым входом восьмого элемента И, выход которого подключен к второму входу седьмого элемента И и второму входу второго элемента И, вход сброса блока сравнения соединен через второй элемент задержки с выходом седьмого элемента И, второй выход двухразрядного распределителя импульсов подключен к второму входу восьмого элемента И.

| название | год | авторы | номер документа |

|---|---|---|---|

| Квадратор | 1987 |

|

SU1501049A1 |

| Функциональный преобразователь | 1983 |

|

SU1108442A1 |

| Вычислительное устройство | 1983 |

|

SU1144105A2 |

| Устройство для вычисления экспоненциальной функции | 1982 |

|

SU1057944A2 |

| Устройство для вычисления показателя экспоненциальной функции | 1985 |

|

SU1270770A1 |

| Вычислительное устройство | 1982 |

|

SU1070545A1 |

| Генератор функций Хаара | 1980 |

|

SU947847A2 |

| Устройство для вычисления элементарных функций | 1984 |

|

SU1168930A1 |

| Устройство для цифровой обработки сигналов | 1985 |

|

SU1336028A1 |

| Устройство для вычисления показателя экспоненциальной функции | 1986 |

|

SU1335990A1 |

ФУНКЦИОНАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ, содержащий первый, второй и третий регистры сдвига, первый регистр аргумента, блок сравнения, первый коммутатор, первый и второй триггеры, первый, второй, третий, четвертый, пятый и шестой элементы И, первый второй и третий элементы ИЛИ, первый элемент задержки и блок управления, который состоит из П- разрядного распределителя импульсов генераторов тактовых и одиночных импульсов, второго и третьего коммутаторов, третьего триггера, элемента НЕ, седьмого элемента И, причем выход генератора тактовых им-пульсов блока управления соединен с входами синхронизации первого, второго и третьего регистров сдвига, выход которого подключен к первому . входу первого элемента Ник входу сброса первого триггера, инверСньй выход которого соединен через пертвый элемент задержки с вторым входом первого элемента И, прямой выход третьего триггера блока управления подключен к управляющим входам первого и третьего регистров сдвига и первому входу первого элемента ИЛИ, выход которого соединен с входом сброса второго триггера, прямой выход которого подключен к первому входу второго элемента И, выход которого соединен с входом установки первого триггера, прямой выход которого подключен к первому входу второго элемента ИЛИ, выход первого элемента И соединен с вторым входом второго элемента ИЛИ, выход которого подключен к информационному входу третьего регистра сдвига и первому входу первого коммутатора, выход которого соединен с первым информационным (Л входом блока сравнения, второй выход с третьего коммутатора блока управления подключен к входу установки С второго триггера, прямой вькод которого соединен с первым входом третьего элемента И, вход синхронизации блока сравнения подключен к выходу генератора тактовых импульсов блока управления, выход седьмого элемента И блока управления соединен с первым д входом четвертого элемента И, выход .которого подключен к второму входу первого элемента ИЛИ, выходы п-разрядного распределителя импульсов блока- управления соединены с входами первого регистра аргумента, шина нулевого потенциала преобразователя подключена к входу данных третьего регистра сдвига, при этом в блоке управления выход генератора тактовых импульсов соединен с входом П -разрядного распределителя импульсов и через элемент НЕ с первым входом седьмого элемента И, выход которого

Изобретение относится к .области автоматики и вычислительной техники и может быть использовано в вычислитепьных устройствах и устройствах дискретной автоматики для вычисления экспоненхщальной или логарифми ческой функции.

Известно устройство для логарифмирования двоичных чисел, содержащее три регистра сдвига, генератор такто-. выхимпульсов, реверсивный счетчик.

генератор счетчика, управляемый делитель, три триггера, пять элемен.тов И и вход Пуск

Недостаток этого устройства заключается в ограниченных функциональных возможностях, которые не позволяют вычислять экспоненциальную функцию.

Наиболее близким к предлагаемому является устройство для вычисления экспоненциальной функции, содержащее три регистра сдвига, сумматор, регистр аргумента, блок управления блок сравнения, коммутатор, три триггера, шесть элементов И, три элемента ИЛИ и два элемента задержки 2. Недостаток этого устройства заключается в ограниченной точности вычислений. Цель изобретения - повышение точности. Поставленная цель достигается тем, что в функциональный преобразователь, содержащий первьш, второй и третий регистры сдвига, первый регистр аргумента, блок сравнения, первый коммутатор, первый и второй триггеры, первый, второй, третий, четвертый, пятый и шестой элементы И, первый, второй и третий элементы.ИЛИ, первый элемент задержки и блок управления, который состоит из П -разрядного распределителя импульсов, генераторов тактовых и одиночных импульсов, второго и трет его коммутаторов, третьего триггера элемента НЕ, седьмого элемента И, причем выход генератора тактовых импульсов блока управления соединен с входами синхронизации первого, второго и третьего регистров сдвига выход которого подключен к первому входу элемента И и к входу сброса первого триггера, инверсный выход которого соединен через первьш элемент задержки с вторым входом первого элемента И, прямой выход трет его триггера блока управления подключен к управляющим входам первого и третьего регистров сдвига и к пер вому входу первого элемента ИЛИ, выход которого соединен с входом сброса второго триггера, прямой вы ход которого подключен к первому входу второго элемента И, выход ко торого соединен с входом установки первого триггера, прямой выход которого подключен к первому входу второго элемента ИЛИ, выход первог элемента И соединен с вторым входо второго элемента ИЛИ, выход которо подключен к информадаонному входу третьего регистра сдвига и первому входу первого коммутатора, выход которого соединен с первым информационным входом блока .сравнения, второй выход третьего коммутатора блока управления подключен к входу 214 установки второго триггера, прямой выход которого соединен с первым входом третьего элемента И, вход синхронизации блока сравнения подключен к выходу генератора тактовых импульсов блока управления, выход седьмого элемента И блока управления соединен с первым входом четвертого элемента И, выход которого подключен к второму входу первого элемента ИЛИ, выходы п -разрядного распределителя импульсов блока управления соединены с входами первого регистра аргумента, шина нулевого потенциала преобразователя подключена к входу данных третьего регистра сдвигов, при этом в блоке управления выход генератора тактовых импульсов соединен с входом п -разрядного распределителя импульсов и через элемент НЕ с первым входом седьмого элемента И, выход которого подклк)чен к входу сброса третьего триггера i к первому входу генератора одиночных импульсов, вход начального запуска преобразователя соединен с входом второго коммутатора, выход которого подключен к второму входу генератора одиночных импульсов, выход которого соединен с информационным входом третьего коммутатора первый выход которого подклю чей к входу установки третьего триггера, вход задания состояния преобразователя подключен к управляющему входу третьего коммутатора, введены вычитатель, второй регистр аргумента и четвертый элемент ИЛИ, а в блок управления введены двухразрядный распределитель импульсов, восьмой элемент И и второй элемент задержки, причем первый выход двухразрядного распределителя импульсов блока управления соединен с первым входом пятого элемента И и вторым входом третьего элемента И, третий вход которого подключен к выходу второго регистра сдвига и информационному входу первого регистра сдвига, выход которого соединен с первым входом вычитателя, второй вход которого подключен к выходу третьего элемента И, а выход вычитателя соединен с Информационным входом второго регистра сдвига и с вторым входом первого коммутатора, вход управления которого подключен к входу задания режима преобразователя, вход данных первого регистра сдвига соединен с прямы ВЫХОДОМ третьего блока управления, входы управления и данных второго регистра сдвига подключены к шине нулевого потенциала преобразователя выход первого регистра аргумента соединен с вторым входом пятого элемента И, выход которого подключен к первому входу третьего элемента ИЛИ, вь1ход которого соединен с вторым входом блока сравнения,первый и второй выходы которого подключены соответственно к первому и второму входам четвертого элемента ИЛИ, выход которого соединен с вторым вх дом четвертого элемента И, выходы tJ-разрядного распределителя импульсов блока управления подключены к входам второго регистра аргумента, выход которого соединен с первым

входом шестого элемента И, выход которого подключен к второму входу третьего элемента ИЛИ, второй выход двухразрядного распределителя импульсов блока управления соединен с вторым входом шестого элемента И, при этом в блоке управления выход последнего разряда. Ц -разрядного распределителя импульсов соединен с входом двухразрядного распределителя импульсов и первым входом восьмого элемента И, вькод которого подключен к второму входу седьмого элемента И и второму входу второго элемента И, вход сброса блока сравнения соединен через второй элемент задержки с выходом седьмого элемента И, второй выход двухразрядног распределителя импульсов подключен к второму входу восьмого элемента И.

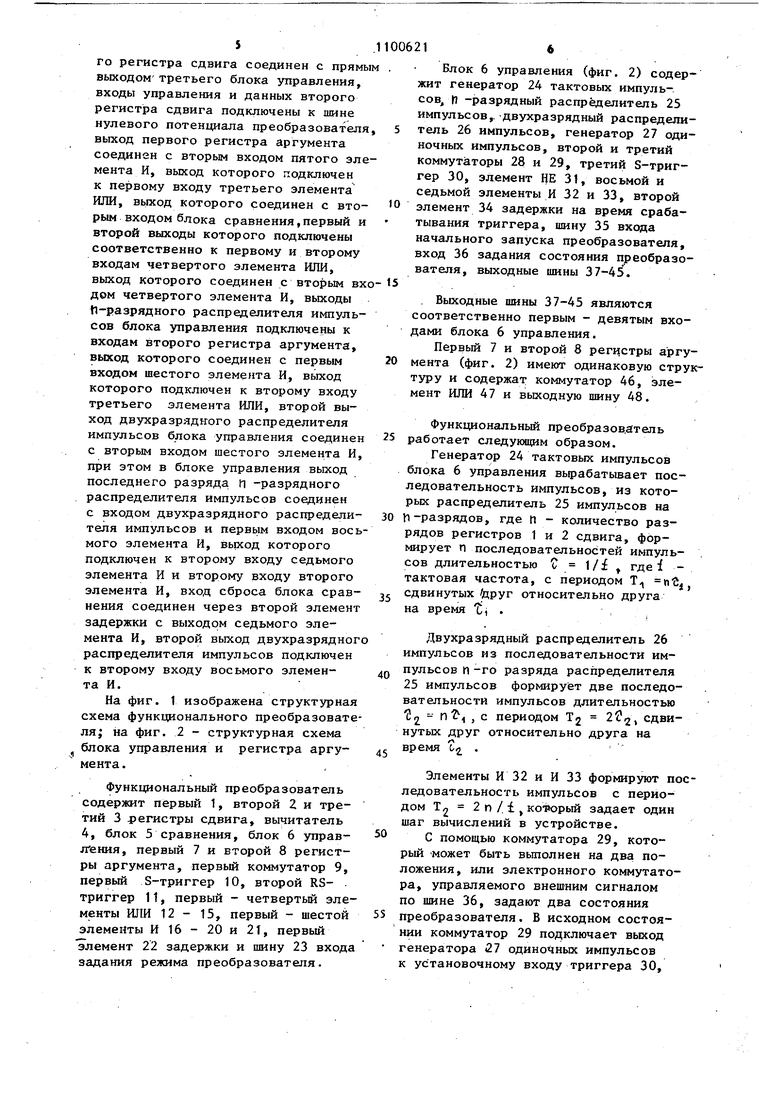

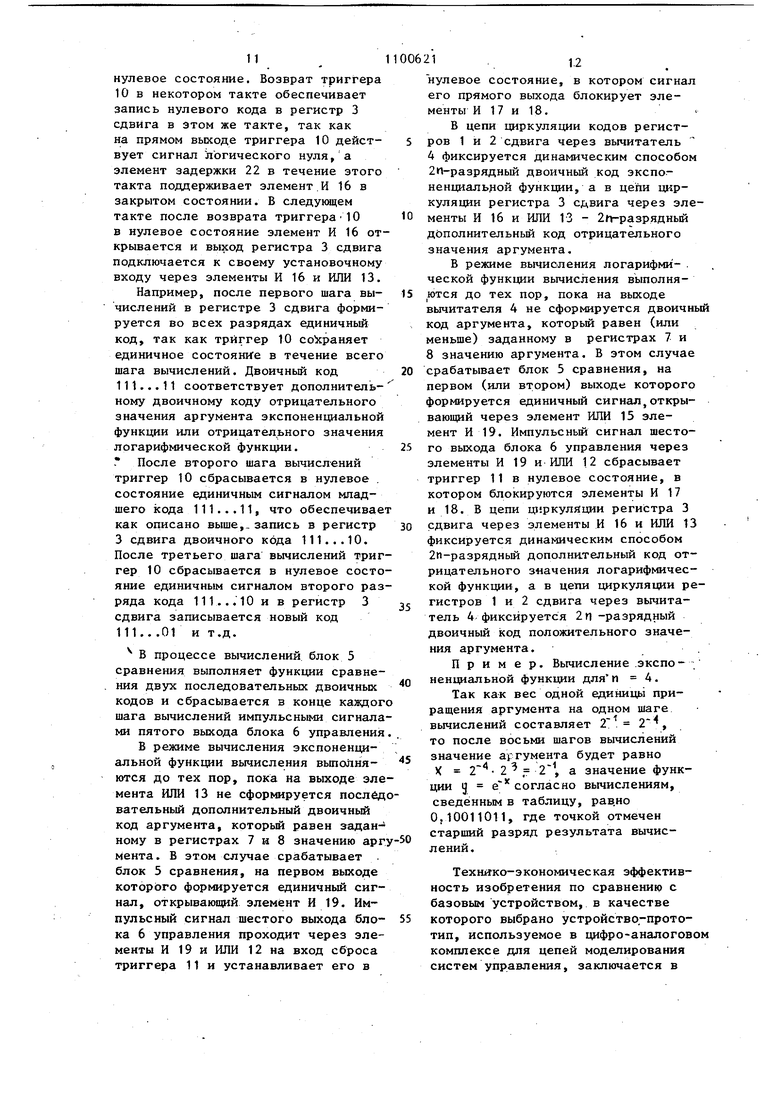

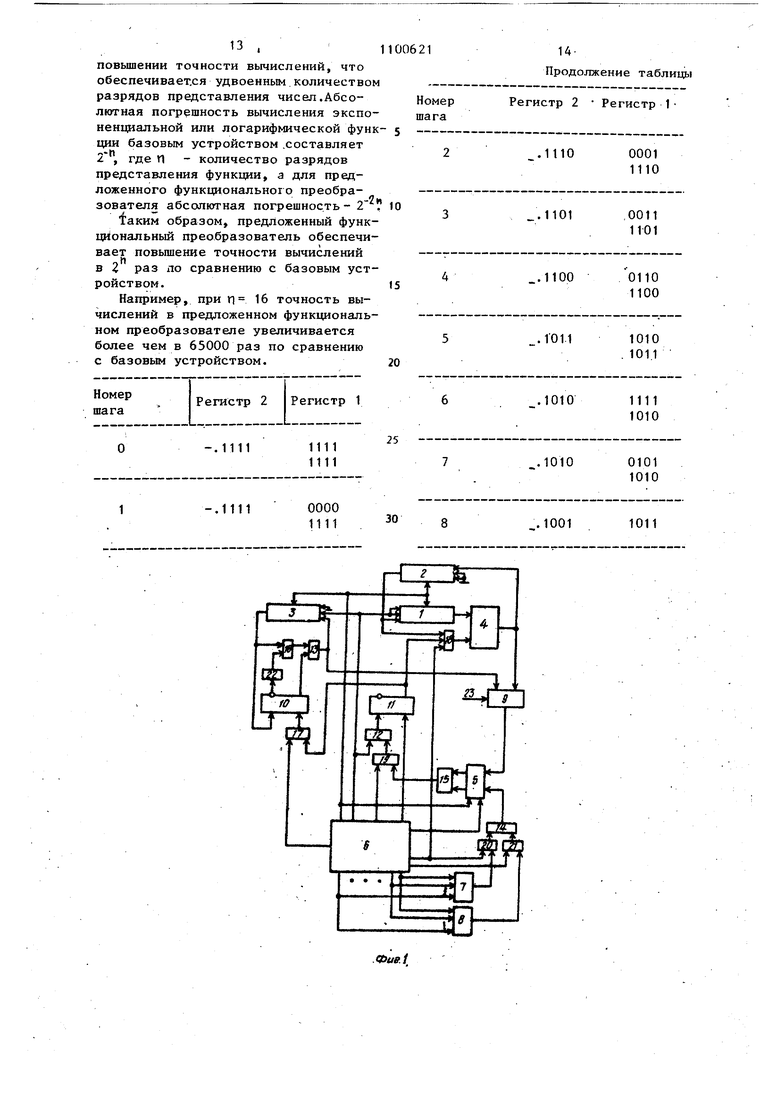

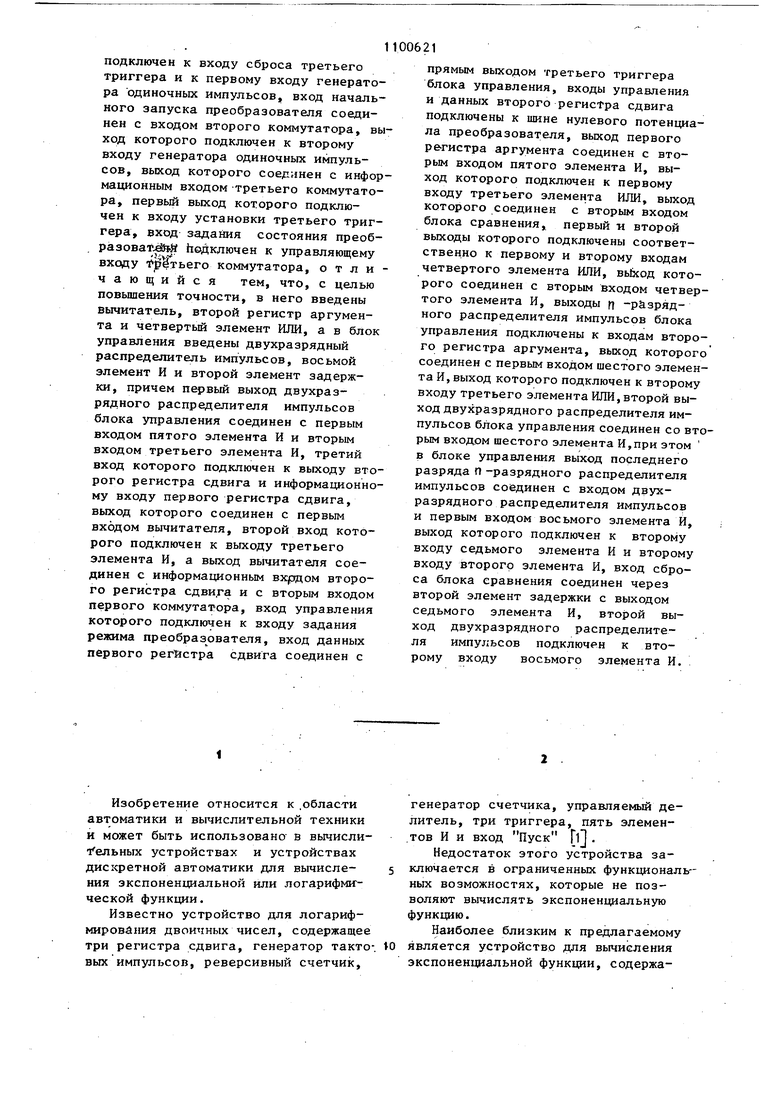

На фиг. 1 изображена структурная схема функционального преобразователя; на фиг. 2 - структурная схема блока управления и регистра аргумента.

Функциональный преобразователь содерямт первый 1, второй 2 и третий 3 4 егистры сдвига, вычитатель 4, блок 5 сравнения, блок 6 управления, первый 7 и второй 8 регистры аргумента, первый коммутатор 9, первый S-триггер 10, второй RSтриггер 11, первый - четвертый элементы ИЛИ 12 - 15, первый - шестой элементы И 16 - 20 и 21, первый Элемент 22 задержки и шину 23 входа задания режима преобразователя.

Блок 6 управления (фиг. 2) содержит генератор 24 тактовых импульсов, П -разрядный распределитель 25 импульсов,, двухразрядный распределитель 26 импульсов, генератор 27 одиночных импульсов, второй и третий коммутаторы 28 и 29, третий S-триггер 30, элемент НЕ 31, восьмой и седьмой элементы И 32 и 33, второй элемент 34 задержки на время срабатывания триггера, шину 35 входа начального запуска преобразователя, вход 36 задания состояния преобразователя, выходные шины 37-45.

. Выходные шины 37-45 являются соответственно первым - девятым входами блока 6 управления.

Первый 7 и второй 8 регистры аргумента (фиг. 2) имеют одинаковую струтуру и содержат коммутатор 46, элемент ИЛИ 47 и выходную шину 48.

Функциональный преобразов.атель работает следукицим образом.

Генератор 24 тактовых импульсов блока 6 управления вьфабатывает последовательность импульсов, из которых распределитель 25 импульсов на И-разрядов, где И - количество разрядов регистров 1 и 2 сдвига, формирует П последовательностей импульсов длительностью С li гдеi тактовая частота, с периодом Т/, nuj сдвинутых /друг относительно друга на время t ,

Двухразрядный распределитель 26 импульсов из последовательности импульсов П-го разряда распределителя 25 импульсов формирует две последовательности импульсов длительностью ,с периодом Т2 , сдвинутых друг относительно друга на время Oj.

Элементы И 32 и И 33 формируют поледовательность импульсов с периодом Тл 2п/. f, КО1ЮРЫЙ задает один шаг вычислений в устройстве.

С помощью коммутатора 29, который может быть выполнен на два положения, или электронного коммутатора, управляемого внешним сигналом по шине 36, задают два состояния преобразователя. В исходном состоянии коммутатор 29 подключает выход генератора 27 одиночных импульсов к установочному входу триггера 30, а в рабочем состоянии - к шине 39 третьего выхода блока 6 управления. Установка преобразователя в исход ное состояние обеспечивается с помощью.коммутатора 28, который может быть выполнен в виде кнопочного переключателя либо в виде электронн го ключа, управляемого внешним сигналом по шине 35. С помощью коммутатора 28 запуска ют генера тор 27 одиночных- ймпульсов, выходной сигнал которого устанавливает триггер 30 в единичное состояние на 2п тактов, так как следующий импульс последовательност действующий на выходе элемента И 33 сбрасывает триггер 30 в нулевое сос тояние. Сигнал логической единицы прямого выхода триггера 30 поступае по шине 38 на второй вход блока 6 управления. Сигнал второго выхода блока 6 управления поступает через элемент ИЛИ 12 на вход сброса триггера 11, устанавливая его в нулевое состояние, а таюке на входы управления и ввода данных регистра 1 сдвига и на вход управления регистра 3 сдвига. Триггер 11 в нулевом состоянии блокирует элементы И 17 и 18. В /h-разрядные регистры 1 и 2 сдвига под действием тактовых импульсов первого выхода блока 6 управления записываются единичные коды во все разряды. Информация в регистр 2 сдвига поступает через :вычитатель А с выхода регистра 1 сдвига. В это время в 2п-разрядный регистр 3 сдв га под действием тактовых импульсов первого выхода блока 6 yпp.aJвлeния записываются нулевые коды во все разряды, так как его вход ввода данных соединен с нулевой шиной, преобразователя. , Триггер 10: сбрасывается в нулевое состояние под действием информа ции, сформированной в результате предшествукицей работы устройства и сдвигаемой с выхода регистра 3 сдвига. Таким образом, в исходном состоя нии триггеры 10 и 11 находятся в,ну левом состоянии, а в 2Л-разрядном кольцевом регистре, образованном последовательным соединением регист ра 1 сдвига, вычитателя 4 и регис ра 2 сдвига, хранится динамическим 18 способом код 11... 1, а в 24-разрядном регистре 3 сдвига - нулевой код. С помощью коммутатора 9, который может быть выполнен в виде переключателя на два Положения либо в виде электронного коммутатора, управляемого внешним сигналом по шине 23, задают режим работы преобразователя. В режиме вычисления экспоненциальной функции первый информационный вход блока 5 сравнения подключается к выходу элемента ИЛИ 13, а в режиме вычисления логарифмической функции к выходу вычитателя 4. Затем в регистрах 7 и 8 аргумента задают Ц младших и п старших разрядов аргумента соответственно. В режиме вычисления экспоненциальной функции в регистрах 7 и 8 аргумента задают дополнительный двоичный код отрицательного значения аргумента, а в режиме вычисления логарифмической функции - прямой двоичный код положительного значения аргумента. Задание двоичного кода аргумента выполняется с помощью коммутатора 46 регистров 7 и 8 аргумента. Коммутатор 46 может быть выполнен, например, в виде переключателя на п направлений и два положения. Коммутатором 46 подключают в единичных разрядах соответствующие выходы распределителя 25 импульсов к входам элемента ИЛИ 47, на выходе которого фор1даруется последовательный п -разрядный код мпадших или старших разрядов набранного значения аргумента. Выходные сигналы распределителя 26 импульсов, действующие на восьмом и девятом выходах блока 6 управления, поочередно подключают через элементы И 20 и 21 выходы регистров 7 и 8 аргумента соответственно к входам элемента ИЛИ 14, на выходе которого формируется 2п-разрядный последовательный двоичный код заданного значения аргумента. „ В режиме вычисления экспоненциальной функции от начальных условий Чо 1 о регистрах 1 и 2 сдвигд формируется 2п-разрядный двоичный код функции, а в регистре 3 сдвига - 2п-разрядиьй двоичный код аргумента. В режиме вычисления логарифмической функции от начальных условий УР о, Xg 1 в регистрах 1 и 2 сд га формируется 2г1-разрядный двоичный код аргумента, а в регистре 3 сдвига - 2п-разрядный двоичный код функции. Работа устройства в режимах вычи ления экспоненциальной и логарифмической функций аналогична. В рабочем состоянии коммутатор 29 подключает выход генератора 27 одиночных импульсов блока 6 управления к установочному входу триггера 11. Запуск процесса вычислений осуществляется коммутатором 28, который запускает генератор 27 одиночных импульсов, формирующий импульсный сигнал на третьем выходе блока управления. Сигнал третьего выхода блока 6 управления устанавливает триггер 11 в единичное состояние, в котором сигнал его прямого выхода снимает блокировку элементов И 17 и 18. Преобразователь в режиме вычисления экспоненциальной функции рабо тает следующим образом. Первый импульс длительностью вп тактов, действующий на восьмом выходе блока 6 управления, открывает элемент И 18. На первый и второй входы вычитателя 4 сдвигаются с выходов 1)ёгистров 1 и 2 сдвига соответственно п младших разрядов и И старших разрядов начального зна чения функции. Вычитатель 4 осущест вляет последовательное вычитание из двоичного кода h младших разрядов начального значения функции двоичного кода л старших разрядов началь ного значения функции. Результат вычитания записывается в регистр 2

сдвига, с выхода которого в это время п старших разрядов начальног значения функции переписываются в регистр 1 сдвига. Через п тактов оэлемент И 18 закрывается и в течение следующих h тактов находится в закрытом состоянии. В это время вычитатель 4 производит вычитание из и старших разрядов двоичного кода функции, который сдвигается с выхода регистра 1 сдвига, сигнал займа, который может образоваться в результате предыдущего вычитания из п младших разрядов п старших разрядов двоичного кода функции.

ки на такт устанавливается сигнал логического нуля инверсного выхода триггера 10, который блокирует элемент И 16. В это время на выходе элемента ИЛИ 13 формируется сигнал логической единицы прямого выхода

триггера 11, который .обеспечивает запись единичных кодов в младшие разряды нового значения двоичного кода, сдвигаемого в регистр 3 сдвига. Так продолжается до момента

считывания первого (начиная с млад.шего разряда) единичного кода с

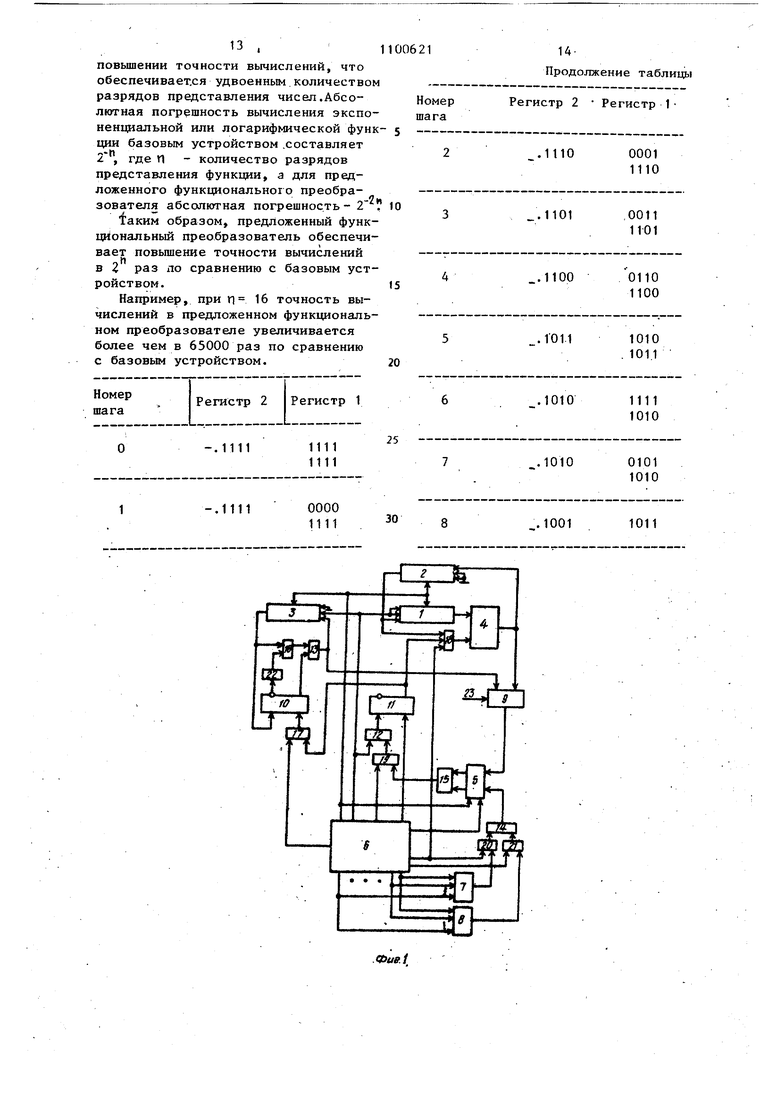

выхода регистра 3 сдвига, сигнал которого сбрасывает триггер 10 в Результат вычитания сигнала займа из и старших разрядов двоичного кода начального значения функции записывается под действием тактовых импульсов первого выхода блока 6 управления в регистр 2 сдвига, с выхода которого ц младших разрядов двоичного кода нового значения функции сдвигаются в регистр 1 сдвига. Таким образом, за 2 ц тактов выполняется один шаг вычислений, после которого в регистре 1 сдвига содержится h младших разрядов нового значения функции, а в регистре 2 сдвига - И старших разрядов нового значения функции. В режиме формирования логарифмической функции аналогичным образом за 2п тактов преобразователь выполняет один шаг вычислений, после которого в регистрах 1 и 2 сдвига содержатся п младших и п старших разрядов нового значения аргумента. Содержимое регистра 3 сдвига после выполнения каждого шага вычисления за 2 п тактов уменьшается на единицу младшего разряда. Рассмотрим процесс формирования кодов в регистре 3 сдвига в течение одного шага вычислений, так как на всех последующих шагах вычислений процесс формирования кодов в регистре 3 сдвига осуществляется аналогичным образом. Перед началом каждого шага вычислений импульсный сигнал четвертого выхода блока 6 управления поступает через элемент И 17 и устанавливает триггер 10 в единичное состояние, К моменту сдвига 14ладшего разряда двоичного кода с выхода регистра 3 сдвига на выходе элемента 22 задержнулевое состояние. Возврат триггера 10 в некотором такте обеспечивает запись нулевого кода в регистр 3 сдвига в этом же такте, так как на прямом выходе триггера 10 действует сигнал логического нуля, а элемент задержки 22 в течение этого такта поддерживает элемент.И 16 в закрытом состоянии. В следукицем такте после возврата триггера10 в нулевое состояние элемент И 16 открывается и выход регистра 3 сдвига подключается к своему установочному входу через элементы И 16 и ИЛИ 13. Например, после первого шага вычислений в регистре 3 сдвига формируется во всех разрядах единичный код, так как триггер 10 сокраняет единичное состояние в течение всего шага вычислений. Двоичный код 111... 11 соответствует дополнительному двоичному коду отрицательного значения аргумента экспоненциальной функции или отрицательного значения логарифмической функции. После второго шага вычислений триггер 10 сбрасывается в нулевое состояние единичным сигналом младшего кода 111... 11, что обеспечивае как описано выше,, запись в регистр 3 сдвига двоичного кода 111...10. После третьего шага вычислений триг гер 10 сбрасывается в нулевое состо яние единичным сигналом второго раз ряда кода 111...10 и в регистр 3 сдвига записывается новый код 111.. .01 и т.д. В процессе вычислений блок 5 сравнения выполняет функции сравнения двух последовательных двоичных кодов и сбрасывается в конце каждог шага вычислений импульсными сигнала ми пятого выхода блока 6 управления В режиме вычисления экспоненциальной функции вычисления вьтолняются до тех пор, пока на выходе эле мента ИЛИ 13 не сформируется послбд нательный дополнительный двоичный код аргумента, который равен заданному в регистрах 7 и 8 значению арг мента. В этом случае срабатывает блок 5 сравнения, на первом выходе которого формируется единичный сигнал, открываюш1Ий элемент И 19. Импульсный сигнал шестого выхода блока 6 управления проходит через элементы И 19 и ИЛИ 12 на вход сброса триггера 11 и устанавливает его в нулевое состояние, в котором сигнал его прямого выхода блокирует элементы И 17 и 18. В цепи циркуляции кодов регистров 1 и 2 сдвига через вычитатель 4 фиксируется динамическим способом 211-разрядный двоичный код экспоненциальной функции, а в цепи циркуляции регистра 3 сдвига через элементы И 16 и ИЛИ 13 - 2п-разрядный дополнительный код отрицательного значения аргумента. В режиме вычисления логарифми- . ческой функции вычисления выполняются до тех пор, пока на выходе вычитателя 4 не сформируется двоичный код аргумента, который равен (или меньше) заданному в регистрах 7 и 8 значению аргумента. В этом случае срабатывает блок 5 сравнения, на первом (или втором) выходе которого формируется единичный сигнал,открывающий через элемент ИЛИ 15 элемент И 19. Импульсный сигнал шестого выхода блока 6 управления через элементы И 19 и ИЛИ 12 сбрасывает триггер 11 в нулевое состояние, в котором блокируются элементы И 17 и 18. В цепи циркуляции регистра 3 сдвига через элементы И 16 и ИЛИ 13 фиксируется динамическим способом 2п-разрядньй дополнительный код отрицательного значения логарифмической функции, а в цепи циркуляции регистров 1 и 2 сдвига через вычитатель 4 фиксируется 2ц -разрядный двоичный код положительного значения аргумента.. Пример. Вычисление экспоненциальной функции дляп 4. Так как вес одной единиць приращения аргумента на одном шаге вычислений составляет 2 . 2, то после восьми шагов вычислений значение аргумента будет равно X 2 2 2 а значение функции Ч е согласно вычислениям, сведенным в таблицу, рав.но 0.10011011, где точкой отмечен старший разряд результата вычислений. Технйко-экономическая эффективность изобретения по сравнению с базовым устройством, в качестве которого выбрано устройство-прототип, используемое в цифро-аналоговом комплексе для цепей моделирования систем управления, заключается в

qyus.i

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для логарифмирования двоичных чисел | 1977 |

|

SU696445A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Авторское свидетельство СССР по заявке № 3412196/18-24, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-06-30—Публикация

1982-12-17—Подача