Изобретение относится к области цифровой вычислительной техники и может быть использовано для приема в вычислительную машину спорадически поступающих двухпозиционных импульсов.

Известно устройство для сопряжения вычислительной машины с двухпозиционными датчиками, содержащее блок управления, распределитель опроса, групповое запоминающее устройство, двухпозиционные переключателидатчики, групповой регистр - фиксатор единичного приращения, буферный регистр, в котором двухпозиционные .переключатели-датчики через распределитель опроса соединены с блоком управления, а через последовательно, соединенные групповой регистрфиксатор и групповое запоминающее устройство подключены также к блоку управления, который через буферный регистр связи с вычислительной машиной соедийен с групповым регистром - фиксатором единичного приращения, шины связи с вычислительной машиной подсоединены к буферному регистру и блоку управления, осуществляющего одновременный прием по всем входным каналам двухпозиционных импульсов, асинхронных относительно друг друга и относительно сигналов опроса, в регистр - фиксатор единичных приращений с последующим сбросом после считывания в машину.

Недостаток известного устройства состоит в том, что при приеме коротких спорадически поступающих двухпозиционных импульсов может происходить пропуск импульсов, так как для приема импульсов нужно, чтобы импульс считывания совпал со входным импульсом от датчика хотя бы один раз. Если такого совпадения нет, то импульс теряется. Кроме того, сброс регистра - фиксатора после считывания осуществляется одновременно по всем разрядам, а в это время по одному из каналов импульс может появиться или исчезнуть. Известная схема ставит ограничение к длительности входных импульсов в зависимости от максимальной частоты опроса.

С целью /повышения надежности приема спорадически поступающих двухпозиционных импульсов любой длительности в предложенном устройстве выход блока формирователей соединен с регистром -- фиксатором единичных приращений, с буферным регистром, на второй вход которого поступает сигнал опроса из вычислительной мащины, а выход буферного регистра через блок линий задержек соединен с регистром - фиксатором единичных приращений, входные щины подключены к блоку формирователей, а шины связи с вычислительной машиной подключены к буферному регистру.

Это позволяет исключить потерю входных импульсов.

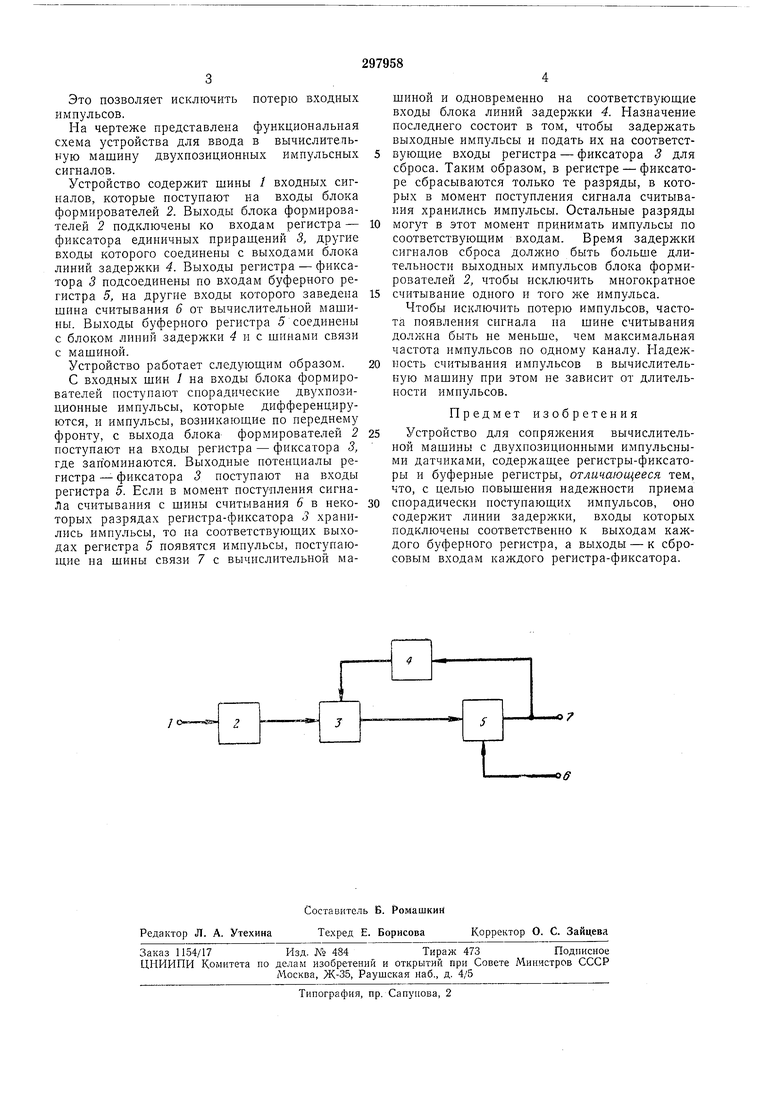

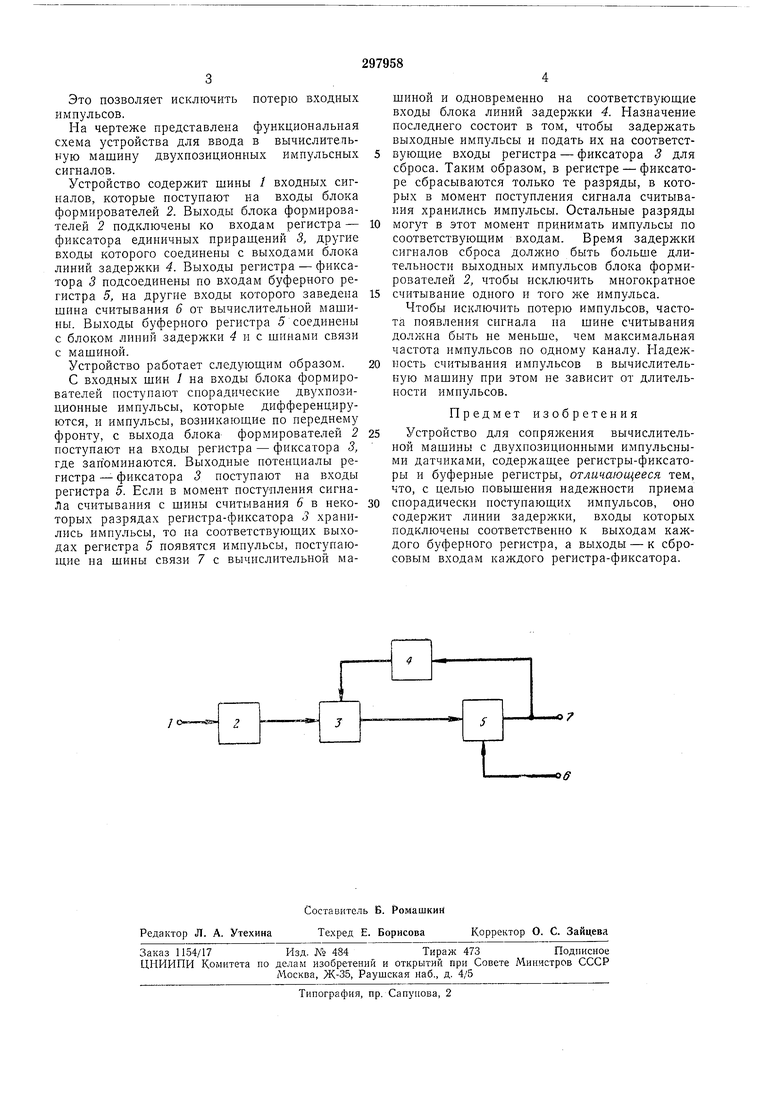

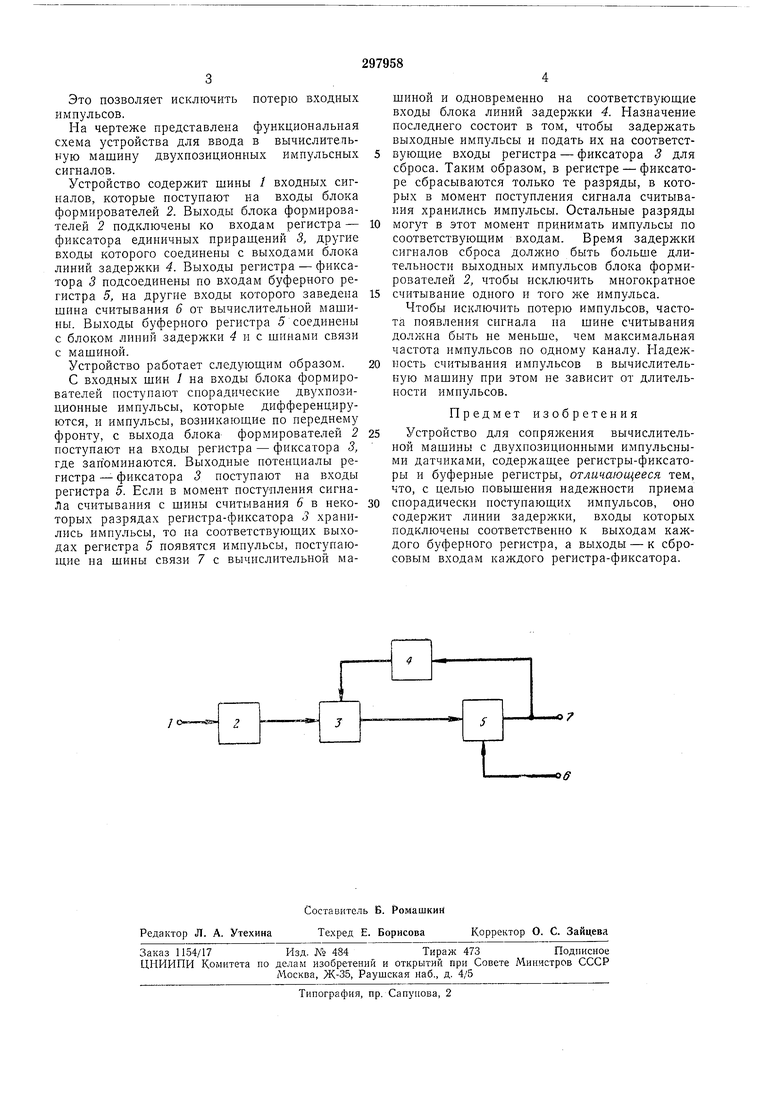

На чертеже представлена функциопальная схема устройства для ввода в вычислительную машипу двухпозициоппых импульсных сигналов.

Устройство содержит шины / входных сигналов, которые поступают на входы блока формирователей 2. Выходы блока формирователей 2 подключены ко входам регистра - фиксатора единичных приращений 3, другие входы которого соединены с выходами блока линий задержки 4. Выходы регистра - фиксатора 3 подсоединены по входам буферного регистра 5, на другие входы которого заведена шина считывания 6 от вычислительной машины. Выходы буферного регистра 5 соединены с блоком линий задержки 4 и с шинами связи с машиной.

Устройство работает следуюндим образом.

С входных шин / на входы блока формирователей поступают спорадические двухпозиционные импульсы, которые дифференцируются, и импульсы, возникаюш,ие по переднему фронту, с выхода блока формирователей 2 поступают на входы регистра - фиксатора 3, где запоминаются. Выходные потенциалы регистра - фиксатора 3 поступают на входы регистра 5. Если в момент ноступления сигнала считывания с шины считывания 6 в некоторых разрядах регистра-фиксатора 3 хранились импульсы, то на соответствующих выходах регистра 5 появятся импульсы, поступающие на шины связи 7 с вычислительной машиной и одновременно на соответствующие входы блока линий задержки 4. Назначение последнего состоит в том, чтобы задержать выходные импульсы и подать их на соответствующие входы регистра - фиксатора 3 для сброса. Таким образом, в регистре - фиксаторе сбрасываются только те разряды, в которых в момент поступления сигнала считывания хранились импульсы. Остальные разряды могут в этот момент принимать импульсы по соответствующим входам. Время задержки сигналов сброса доллаю быть больше длительности выходных импульсов блока формирователей 2, чтобы исключить многократное считывание одного и того же импульса.

Чтобы исключить потерю импульсов, частота появления сигнала па шине считывания должна быть не меньше, чем максимальная частота нмпульсов по одному каналу. Надежность считывания импульсов в вычислительную машину при этом не зависит от длительности имнульсов.

Нредмет изобретения

Устройство для сопряжения вычислительной машины с двухпозиционными импульсными датчиками, содержащее регистры-фиксаторы и буферные регистры, отличающееся тем, что, с целью повышения надежности приема спорадически поступающих импульсов, оно содержит линии задержки, входы которых подключены соответственно к выходам каждого буферного регистра, а выходы - к сбросовым входам каждого регистра-фиксатора.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО СОПРЯЖЕНИЯ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ с ДВУХПОЗИЦИОННЫМИ ИМПУЛЬСНЫМИ ДАТЧИКАМИ | 1973 |

|

SU378834A1 |

| УСТРОЙСТВО для СОПРЯЖЕНИЯ BЬfЧИCЛИTEЛЬHOЙ MAfUHHbf с ДВУХПОЗИЦИОННЫМИ ИМПУЛЬСНЫМИ ДАТЧИКАМИ | 1968 |

|

SU222004A1 |

| Устройство для ввода информации | 1982 |

|

SU1056175A1 |

| Устройство для сопряжения цифровой вычислительной машины | 1987 |

|

SU1444793A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ С КАНАЛАМИ СВЯЗИ | 1990 |

|

RU2020565C1 |

| Буферное запоминающее устройство | 1978 |

|

SU942132A1 |

| Многоканальное устройство тестового контроля логических узлов | 1988 |

|

SU1564623A1 |

| Устройство для считывания графической информации | 1973 |

|

SU667976A1 |

| Устройство для обслуживания групповых заявок | 1986 |

|

SU1381507A1 |

| МИКРОПРОЦЕССОР ВВОДА-ВЫВОДА ИНФОРМАЦИИ | 1992 |

|

RU2042182C1 |

Даты

1971-01-01—Публикация