Предлагаемое устройство относится к области автоматики и может быть использовано в приборах автоматики и измерительной техники.

По авт. св. № 224566 известно устройство для формирования импульсных последовательностей, в котором используется программный блок, задающий генератор, делитель частоты, схема совпадения кодов и статический регистр. В известном устройстве повышение точности формирования временных интервалов требует повышения частоты сигнала задающего генератора, а это, в свою очередь, требует повыщения быстродействия отдельных узлов.

Предложенное устройство отличается тем, что оно содержит блок дискретного измерения фазы сигнала, входы которого соединены с выходами блока уточнения и программного блока, а выход блока дискретного изменения фазы сигнала подключен к выходу устройства и входу программного блока. Это повышает точность формирования импульсных последовательностей.

Дополнительный блок дискретного изменения фазы сигнала, в котором может быть использован, например, нониусный метод или метод гетеродинирования, управляется сигналов из программного блока и обеспечивает изменение временного положения формируемого импульсного сигнала в пределах периода сигнала задающего генератора. Причем точная установка временного положения осуществляется в выходных цепях устройства,

где выходные сигналы имеют низкую частоту повторения, и, благодаря этому, переходные процессы, возникающие в блоке при изменении кода точного значения временного положения, не нарушают работу устройства.

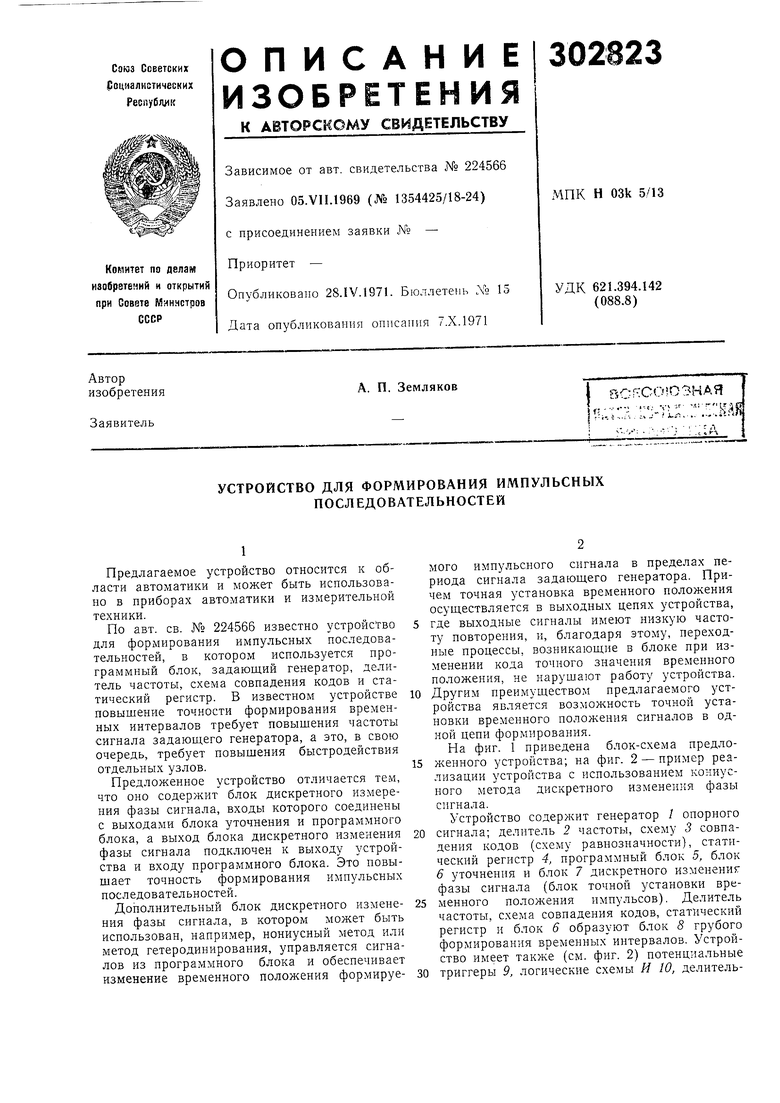

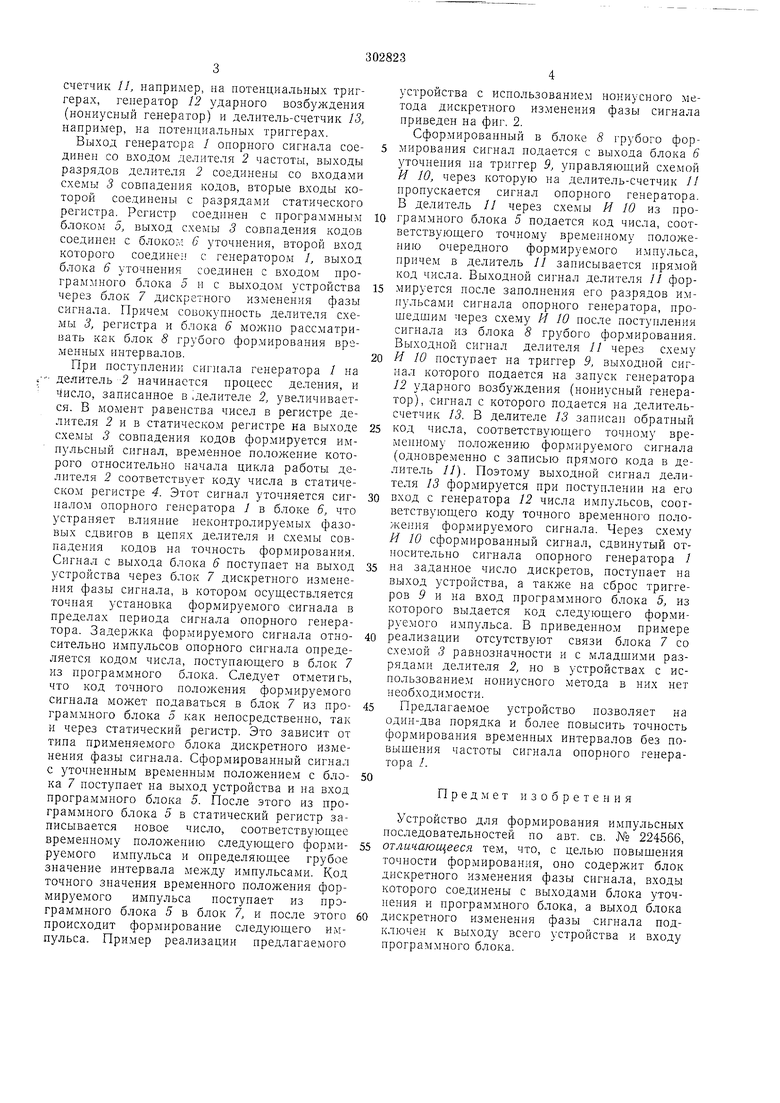

Другим преимуществом предлагаемого устройства является возможность точной установки временного положения сигналов в одной цепи формирования. На фиг. 1 приведена блок-схема предложенного устройства; на фиг. 2 - пример реализации устройства с использованием кокиусного метода дискретного изменения фазы сигнала. Устройство содержит генератор / опорного

сигнала; делитель 2 частоты, схему 3 совпадения кодов (схему равнозначности), статический регистр 4, программный блок 5, блок 6 уточнения и блок 7 дискретного изменениг фазы сигнала (блок точной установки временного положения импульсов). Делитель частоты, схема совпадения кодов, статический регистр и блок 6 образуют блок 8 грубого формирования временных интервалов. Устройство имеет также (см. фиг. 2) потенциальные

счетчик //, например, на потенциальных триггерах, геператор 12 ударного возбуждения (нониусный генератор) и делитель-счетчик 13, например, на потенциальных триггерах.

Выход генератора / опорного сигнала соедивен со входом делителя 2 частоты, выходы разрядов делителя 2 соединены со входами схемы 3 совпадения кодов, вторые входы которой соединены с разрядами статического регистра. Регистр соединен с программным блоком 5, выход схемы 3 совпадения кодов соединен с блоко.м 6 уточнения, второй вход которого соедине; с генератором I, выход блока 6 уточнения соединен с входом программного блока 5 и с выходом устройства через блок 7 дискретного изменения фазы сигнала. Причем совокупность делителя схемы 3, регистра и блока 6 можио рассматривать как блок 8 грубого формирования временных интервалов.

При поступлении генератора / на делитель -2 начинается процесс деления, и число, записанное в делителе 2, увеличивается. В момент равенства чисел в регистре делителя 2 и в статическом регистре на выходе схемы 3 совпадения кодов формируется импульсный сигнал, временное положение которого относительно начала цикла работы делителя 2 соответствует коду числа в статическом регистре 4. Этот сигнал уточняется сигпалом опорного генератора 1 в блоке 6, что устраняет влияние неконтролируемых фазовых сдвигов в цепях делителя и схемы совпадения кодов на точность формирования. Сигнал с выхода блока 6 поступает на выход устройства через блок 7 дискретного изменения фазы сигнала, в котором осуществляется точная установка формируемого сигнала в пределах иериода сигнала опорного генератора. Задержка формируемого сигнала относительно импульсов опорного сигнала определяется кодом числа, поступающего в блок 7 из программного блока. Следует отметигь, что код точного положения формируемого сигнала может подаваться в блок 7 из программного блока 5 как непосредственно, так и через статический регистр. Это зависит от типа применяемого блока дискретного изменения фазы сигнала. Сформированный сигнал с уточненным временным положением с блока 7 ноступает на выход устройства и на вход программного блока 5. После этого из программного блока 5 в статический регистр записывается новое число, соответствующее временному положению следующего формируемого импульса и определяющее грубое значение интервала импульсами. Код точного значения временного положения формируемого импульса поступает из программного блока 5 в блок 7, и после этого происходит формирование следующего импульса. Пример реализации предлагаемого

устройства с использованием иониусного метода дискретного изменения фазы сигнала приведен на фиг. 2.

Сформированный в блоке 8 грубого формирования сигнал подается с выхода блока 6 уточнения на триггер 9, управляющий схемой Я 10, через которую на делитель-счетчик // пропускается сигнал опорного генератора. В делитель 11 через схемы Я 10 из программного блока 5 подается код числа, соответствующего точному временному положению очередного формируемого импульса, приче.м в делитель 11 записывается прямой код числа. Выходной сигнал делителя // формируется после заполнения его разрядов импульсами сигнала опорного геператора, прощедщим через схему Я 10 после иостуи.аения сигнала из блока 8 грубого формирования. Выходной сигнал делителя // через схему Я 10 поступает па триггер 9, выходной сигнал которого подается на запуск генератора 12 ударного возбуждения (нониусиый генератор), сигнал с которого подается на делительсчетчик 13. В делителе 13 записан обратный код числа, соответствующего точному временному положению формируемого сигнала (одновременно с записью прямого кода в делитель 11. Поэтому выходной сигнал делителя 13 формируется при поступлении на его вход с генератора 12 числа импульсов, соответствующего коду точного временного положения формируемого сигнала. Через схему Я 10 сформированный сигнал, сдвинутый относительно сигнала опорного генератора / на заданное число дискретов, поступает на выход устройства, а также на сброс триггеров 9 и на вход программного блока 5, из которого выдается код следующего формируемого импульса. В приведенном примере реализации отсутствуют связи блока 7 со схемой 3 равнозначности и с младщими разрядами делителя 2, но в устройствах с использованиел нониусиого метода в них нет необходимости.

Предлагаемое устройство позволяет на один-два порядка и более повысить точность формирования временных интервалов без повыщения частоты сигнала опорного генератора /.

Предмет изобретения

Устройство для формирования импульсных последовательностей по авт. св. ° 224566, отличающееся тем, что, с целью повыщения точности формирования, оно содержит блок дискретного изменения фазы сигнала, входы которого соединены с выходами блока уточнения и программного блока, а выход блока дискретного изменения фазы сигнала подключен к выходу всего устройства и входу программного блока.

1 tL

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для формирования импульсных последовательностей | 1969 |

|

SU439909A1 |

| ПАТЕНТНО- ^г^^ | 1970 |

|

SU272367A1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ИМПУЛЬСНЫХ ПОСЛЕДОВАТЕЛЬНОСТЕЙ | 1967 |

|

SU224566A1 |

| УСТРОЙСТВО ФОРМИРОВАНИЯ ВРЕМЕННЫХ ИМПУЛЬСНЫХ ПОСЛЕДОВАТЕЛЬНОСТЕЙ | 1970 |

|

SU280535A1 |

| ВСЕСОЮЗН.АЯ ПАТЕНТНО-ГЕХВг:Е-ЯД^1 | 1970 |

|

SU287105A1 |

| УСТРОЙСТВО ФОРМИРОВАНИЯ СИГНАЛА С ДИСКРЕТНО ИЗМЕНЯЕМОЙ ФАЗОЙ | 1971 |

|

SU320036A1 |

| Формирователь импульсных последовательностей | 1988 |

|

SU1539973A1 |

| ПРИЕМОПЕРЕДАЮЩАЯ АППАРАТУРА ШИРОКОПОЛОСНЫХ ПСЕВДОСЛУЧАЙНЫХ СИГНАЛОВ | 1979 |

|

SU1840119A1 |

| СИСТЕМА ПЕРЕДАЧИ И ПРИЕМА ДИСКРЕТНОЙ ИНФОРМАЦИИ ПО РАДИОКАНАЛАМ ИМПУЛЬСНО-ФАЗОВОЙ РАДИОНАВИГАЦИОННОЙ СИСТЕМЫ | 1994 |

|

RU2079855C1 |

| Устройство фазовой синхронизации | 1981 |

|

SU995360A1 |

Даты

1971-01-01—Публикация