Предлагаемое изобретение относится к области автоматики и может быть исиользоваио в ирИборах автоматики, измерительной техники, радиолокации и радиоеавигации, в частности, для формирования точных временных интервалов с иомощыо импульсных иоследовательиостей.

Известны различные устройства для формирования Времеииых интервалов с помощью бинарной иоследовательности импульсов.

Известное устройство содержит двоичный делитель частоты, работающий от генератора опорных И1м.пульсов, статический регистр, многовходовую схему совпадения и программный блок, причем импульс иа выходе схемы совнаде иия, являющемся выходом всего устройства формироваиия, появляется три точном со.впаденИ состояний двоичного делителя и статического регистра. В последний из програММлого блока последовательио во времени по командарм из схемы совпадения записываются числа, соответствующие Бременно.му положению очередных формируемых импульсов относительно момента обнуления двоичного делителя. В известио.м устройстве имеется связь, с иомощью «оторой в коице цикла форМироваиия импульсов производится сброс в нулевое положение двоичного делителя по команде из программного блока (вход цикловой синхронизации двоичного делителя). Эта

связь существенно ограничивает бглстродействие схемы, и слсдоватольпо, точность временного положения формируемых н ш льcoв. Действительно после формирования последнего импульса по:ледовательности в данном цикле работы регистра из программного блока подается команда на установку регпстра делителя в нулевое положение и записывается новое число в регнстр. , что любая команда из программиого блока на установку в нуль двоичного делителя должна быть жестко сиихронизироваиа с работой двоичного делнтеля и схемы сравнения. В нроTOiBHOM случае все последующие (после установки в ноль двоичного делителя) импульсы будут сфор}.ироваиы с ошибкой во времени. Для цели этой синхронизации служит, в частности, связь схемы совпадения е тактовым входом программного блока. Следует отметить, что если (п- 1)-й входной имнульс двоичного делнтеля устанавливает последний в состояиие, совпадающее с состояиием статического регистра, в 1 отором запнсаи код временного ноложенпя иоследнего нмиульса цикла формируемой импульсной последовательности, то выработанный лри этом импульс иа выходе схемы совпадений должен успеть обеспечить срабатывание программного блока и установку в ноль двоичиого дел1ителя до поступления иа вход делителя следующего, п-го

входного импульса. В противном случае все последующие формируемые импульсы будут иметь ошибку во временном положении, та« как «ноль деЛИтеля будет сбит, причем эта ошибка будет увеличиваться с каждым новым циклом. Следовательно, суммарное время срабатывания програлигиого блока и время установки в «ноль двоичного делителя по входу цикловой синхронизации должно быть значнтельно меньше нериода входных импульсов двоичного делителя.

Это €оображенне, при учете реальных времен срабатывания программного блока и установки в ««оль (но входу цикловой оинхронизацни) двоичного делителя, вынуждает при иснользованни прототияа увеличивать нериод входной частоты двонччюго дел.ителя.

Последнее, в свою очередь, обусловливает невысокую точность задания временного ноложення импульсов из программного блока, делает невозможным получение импульсов, времевное положение которых определяется с малым дискретом, т. е. с вььсожой степенью точности. Например, Б случае, если быстродействне программного блока /пр.бл 1 мксек н время установки двончиого делителя в «нуль по входу цикловой синхронизации уст.в.о 1 мксгк-., и нериод входных импульсов двоичного делителя Гдх должен быть

J вх пр.бл Г уст.в„0,

..«л:сел:,

т. е. задать из программлого блока (и получить иа выходе устройства) имнульс, временное положение которого определялось бы (для цифр нашего примера) с точностью, превышающей 2 мксек, иевозможио.

Таким образом, наличие цикловой синхронизации двоичиого делителя по команде из програ.ммиого блока создает зависимость точности формирования импульсных последовательностей от быстродействия ирограммного блока. Этот недостаток существенно олраничивает возможности ирактического, использования известного устройства. Целью изобретения является устранение зависимости точности фор.мированяя произвольных импульсных последовательностей от быстродействия программного блока, или другими словалш, повышение быстродействия формирователя.

Эта цель достигается в предлагаемом устрОЙстве введением суммирующего устройства с разрядностью, равной разрядности двоичного делителя (и регистра памяти), и неучитываемым иереполнением разрядной сетки. Выход суммирующего устройства соединен с входо.м регистра памяти, а один вход суммирующего устройства соединен с выходом программного устройства, другой-с выходом регнстра намятн, присоединениым одновременно к входу схемы совнадения.

ясняющая нринцип работы суммирующего устройства.

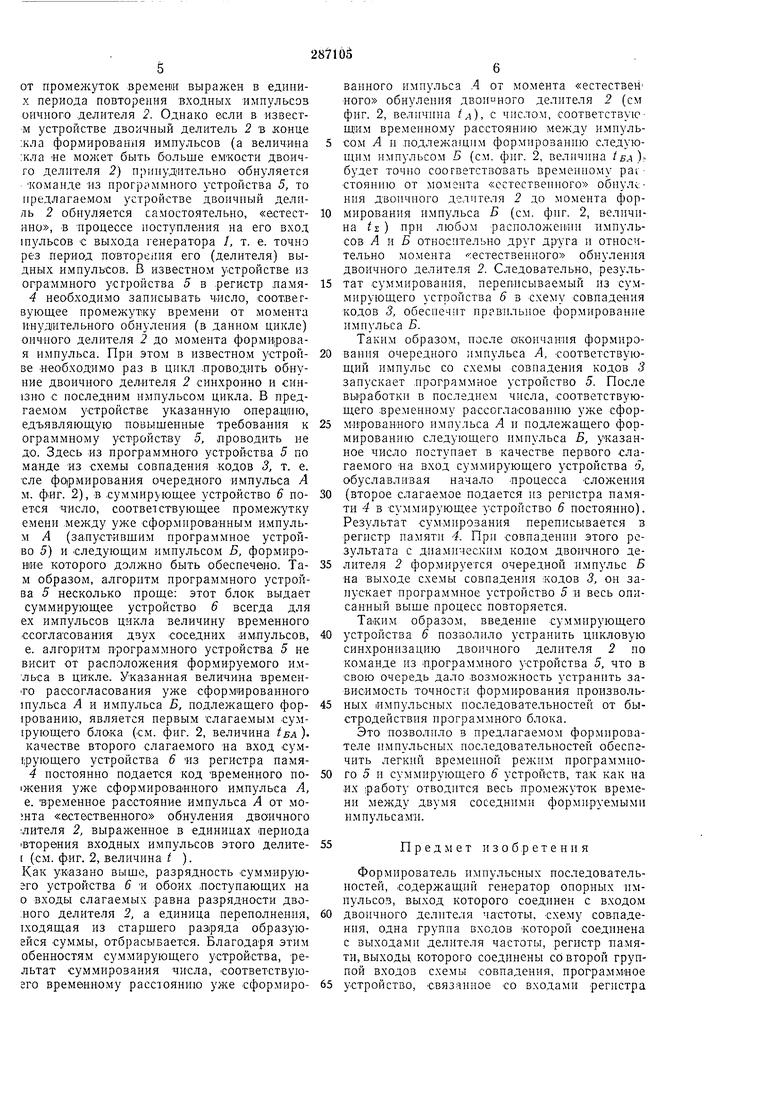

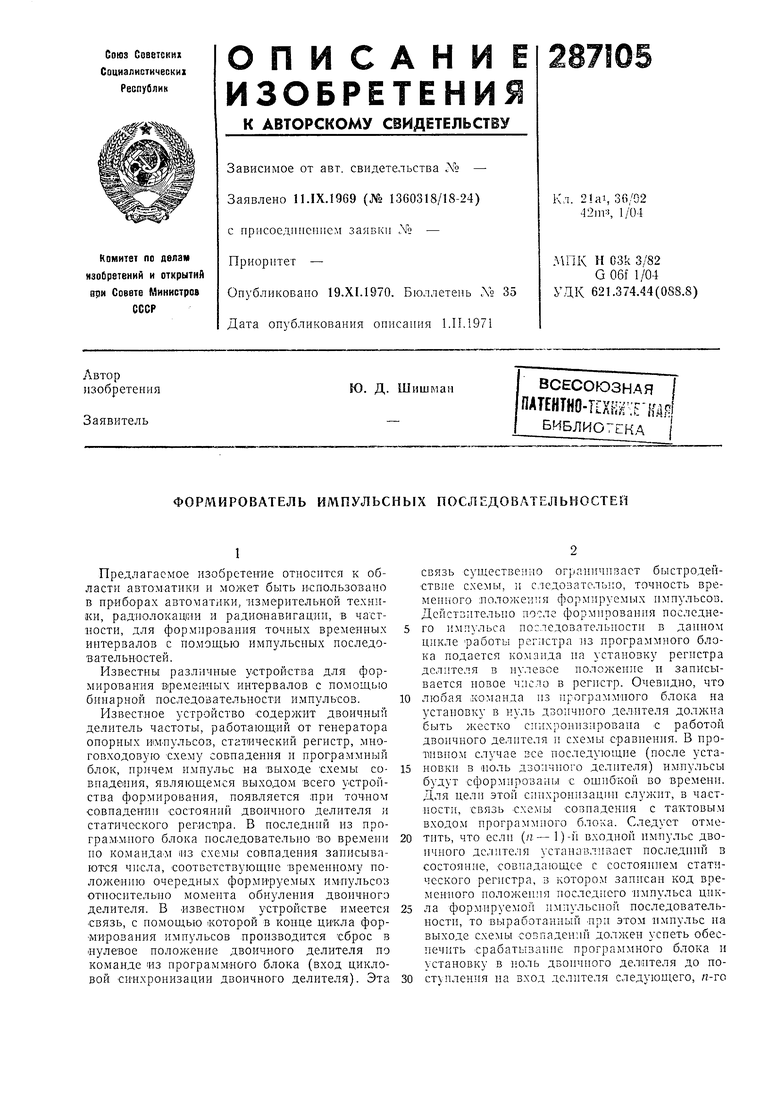

Предлагаемый формирователь имиульсных последовательностей содержит генератор / опорных импульсов, выхад которого соединен с входом двоичного делителя 2. С целью увеличения быстродействия этот делитель может быть выполнен, например, по схеме с параллельным переносом, что обеспечивает постоянную (и гораздо меньшую периода повторения входных импульсов) паразитную задержку установления в нем любого двоичного кода при поступлении любого очередного входного имяульса. Выходы всех разрядов

двоичного делителя 2 соединены с соответствующими входами многоразрядной схемы совнадения кодов 3, причем на вторые входы схемы .совпадения кодов 3 подаются соответствуюои е разряды регистра ламяти 4. Логнчески .схема совпадения кодов 3 выполняет операцию равнозначности кодов двоичного делителя 2 и регистра памяти 4. Выход схемы совпадения кодов 3 является выходом формирователя и присоединен одновременно

ко 1ВХОДУ программного устройства 5, обеспечивая запуск выполнения программы в последнем.

Отличительной особенностью предлагаемого формирователя импульсных последовательностей является введение суммирующего устройства 6. Один его многоразрядный вход (первое слагаемое) соединен с выходом программного устройства 5, другой многоразрядный вход (второе слагаемое) соединен с выходом регистра памяти 4, присоединенным одновременно и к схеме совпадения кодов 3. Многоразрядный выход суммирующего устройства 6 (сумма) присоединен к входу регистра памяти 4. Разрядность всех указанных входов

и выходов, а также самого суммирующего устройства 6, равна разрядности двоичного делителя 2 и регистра памяти 4. Особенность выполнения суммирующего устройства 6 состоит в том, что еди11ииа пе(ревыполнения, выходящая при суммировании слагаемых ,за разрядную сетку блока из старщего разряда суммы, отбрасывается и нигде в дальнейшем не учитывается. Эго принципиально важно для работы предлагаемого устройства и в то

же время существенно облегчает техническую реализацию суммирующего устройства 6.

Как известно, в подобных схемах импульс на выходе схемы совпадения кодов 3 вырабатывается при совпадении (с точностью до

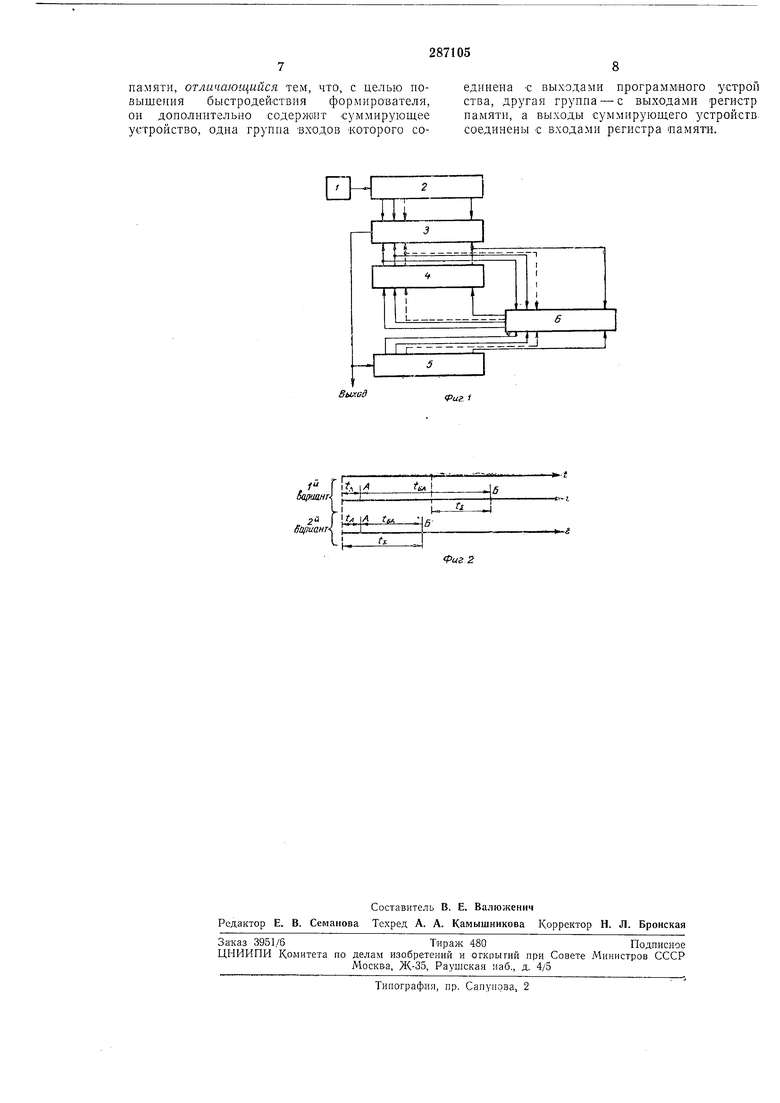

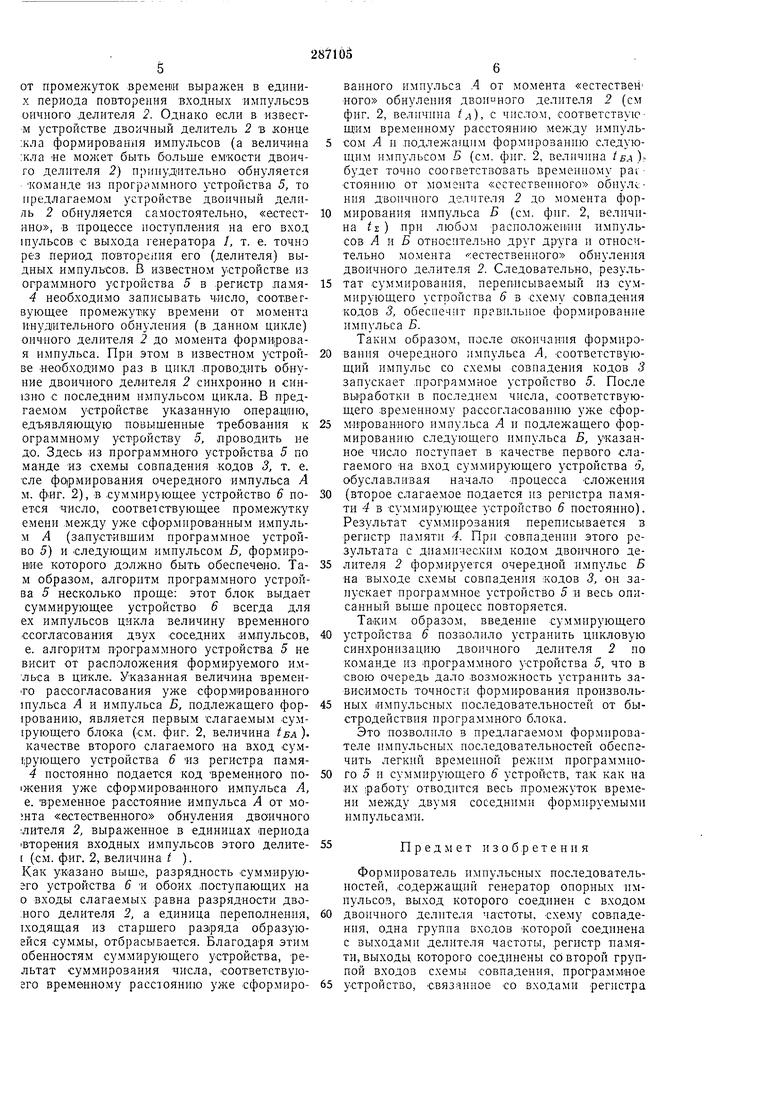

младшего разряда) динамического, меняющегося с каждым входным импульсом, кода двоичиого делителя 2 со статичеаким кодом регистра памяти 4. Код в этом регистре меняется значительно реже: один раз для каждого из формируемых импульсов. Код временного положения очередного формируемого нмнульса, записаниый в регистр 4, численно равен промежутку времени от момента обнуления двоичного делителя 2 до требуемого от промежуток времени выражен в единиX периода повтореиия входпых импульсэв ойчиого делителя 2. Одпако если в известм устройстве двоичный делитель 2 в конце :кла формиров ания импульсов (а величина :кла не может быть больше емкости двоичго делителя 2) принудительно обнуляется Команде из ирогруммного устройства 5, то предлагаемом устройстве двоичный делпль 2 обнуляется самостоятельно, «естестнно, в ироцессе поступления на его вход шульсов с выхода генератора 1, т. е. точно рез период noBTOpeiniH его (делителя) выдных импульсов. В известном устройстве из ограммного устройства 5 в .регистр ламя4 необходимо записывать ч-нсло, соотвегвующее промежутку времени от момента Инудительного обнуления (в данном цикле) ончного делителя 2 до момента форми;ровая импульса. При этом в известном устройве Необходимо раз в цикл .проводить обнуние двоичного дел«теля 2 синхронно и син13НО с носледним нмпульсом цикла. В предгаемом устройстве указанную опера.цию, едъявляющую повышенные требоваиия к ограммному устройству 5, проводить не до. Здесь :из нрограммного устройства 5 по манде из схемы совпадения кодов 3, т. е. еле формирования очередного импульса Л м. ф|Иг. 2), в суммир.ющее устройство 6 поется число, соответствующее иромежутку еменн .между уже сформированным импульм Л (за.пустившим программное устройво 5) и следующим импульсом Б, формироН1ие которого должно быть обеспечено. Там образом, алгоритм нрограммного устройва 5 несколько проще: этот блок выдает суммирующее устройство 6 всегда для ех импульсов цикла величину временного ссогласования дзух соседних импульсов, е. алгоритм программного устройства 5 не висит от расположения формируемого имльса в цикле. Указанная величина временто рассогласования уже сформированного шульса А и импульса Б, подлежащего форфованию, является первым слагаемым сумфующето блака (см. фиг. 2, величина IBA ). качестве второго слагаемого на вход сумфующего устройства 5 из регистра памя4 постоянно подается код временного по1жения уже сформироваиного импульса А, е. Временное расстояние импульса А от «естественного обнуления двоичного лителя 2, выраженное в единицах периода вторения входных импульсов этого делите (см. ф-иг. 2, величина i ). Как указано выше, разрядность суммируюгго устройства 6 И обоих поступающих на о входы слагаемых равна разрядности дво;ного делителя 2, а единица переполнения, 1ходящая из старшего разряда образуюейся сум.мы, отбрасывается. Благодаря этим обенностям суммирующего устройства, рельтат суммирования числа, соответствуюего временному расстоянию уже сформированного импульса .4 от момента «естествен ного обнуления двоичного делителя 2 (см фиг. 2, величина i А}, с Ч11слом, соответствующим временному расстоянию между имиульсом А и .подлен ащим формирован 1ю следующим импульсом 5 (см. фиг. 2, величина iBA} будет точно соогветствовать временному pat стоянию от момента «естественного обнуления двоичного делителя 2 до момента формирования импульса Б (см. фиг. 2, величпна t-L) при любом расположении импульсов А и Б относительно друг друга и относительно момента естественного обнуления двоичного делителя 2. Следовательно, результат суммиро.вания, переписываемый из суммирующего устройства 6 в схему совпадения кодов 3, обеспе-итт правильное формирование имиульса Б. вання очередного импульса А, соответствующий импульс со схемы совпадения кодов 3 запускает .программное устройство 5. После выработки в последнем числа, соответствующего временному рассогласованию уже сформпрованного импульса Л и подлежащего формированию следующего импульса Б, указанное число поступает в качестве первого слагаемого -на вход суммирующего устройства 5, обуславливая начало процесса сложения ти 4 в суммирующее устройство В постоянно). Результат суммирования переписывается в регистр памяти 4. При совпадении этого результата с диамическим кодом двоичного делителя 2 фор.мируется очередной имнульс Б на выходе схемы совпадения кодов 3, он запускает программное устройство 5 :и весь описанный выше процесс повторяется. устройства 5 позволило устранить цикловую синхронизацию двоичного делителя 2 по команде из программного устройства 5, что в свою очередь дало .возможность устранить зависимость точности формирования ироизвольных импульсных последовательностей от быстродействия программного блока. теле импульсных последовательностей обеспечить легкий времеппой режим программного 5 и суммирующего 6 устройств, так как на их работу отводится весь промежуток времени двумя соседними формируемыми нмпульсамИ. ностей, содержащий генератор опорных нмпульсоз, выход которого соедннен с входом двоичного делителя частоты, схему совпадения, о.дна группа входов которой соединена с выходами .делителя частоты, регистр па.мяти, выходы, которого соединены со второй группой входов схемы совпадения, программиое Таким образом, иосле окончания формиро(второе слагаемое подается из регистра памяТаким образо.м, введение суммирующего Это позволило в предлагаемом формироваПредмет изоб.ретения Формирователь импульсных последовательпамяти, отличающийся тем, что, с целью повышения быстродействия формирователя, он дополнительно содержит суммирующее устройство, одна группа входов которого соединена с выходами программного устрой ства, другая группа--с выходами регистр памяти, а выходы суммирующего устройств соединены с входами регистра памяти.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой адаптивный линейный интерполятор | 1982 |

|

SU1095189A1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ИМПУЛЬСНЫХ ПОСЛЕДОВАТЕЛЬНОСТЕЙ | 1967 |

|

SU224566A1 |

| Формирователь импульсных последовательностей | 1988 |

|

SU1539973A1 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА СИГНАЛОВ С ОГРАНИЧЕННЫМ СПЕКТРОМ (ВАРИАНТЫ) | 2004 |

|

RU2265278C1 |

| Цифровой линейный интерполятор | 1989 |

|

SU1631518A1 |

| СПОСОБ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ ДЛЯ СИГНАЛОВ С СОСРЕДОТОЧЕННОЙ ИЛИ РАСПРЕДЕЛЕННОЙ ПО ЦИКЛУ СИНХРОГРУППОЙ | 2021 |

|

RU2780048C1 |

| Генератор псевдослучайных чисел | 1981 |

|

SU962931A1 |

| Устройство для цикловой синхронизации | 1978 |

|

SU758551A1 |

| УСТРОЙСТВО ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2021 |

|

RU2782473C1 |

| УСТРОЙСТВО для ЦИФРОВОГО РЕГУЛИРОВАНИЯ СКОРОСТИ | 1973 |

|

SU374580A1 |

вы-чвд

Риг.

Даты

1970-01-01—Публикация