Изобретение относится к импульсной технике и может быть использовано в измерительных приборах, устройствах автоматики, радиолокации и радионавигации, в частности для формирования точных временных интервалов с помощью импульсных последовательностей .

Целью изобретения является повы- шение точности формирования импульсных последовательностей.

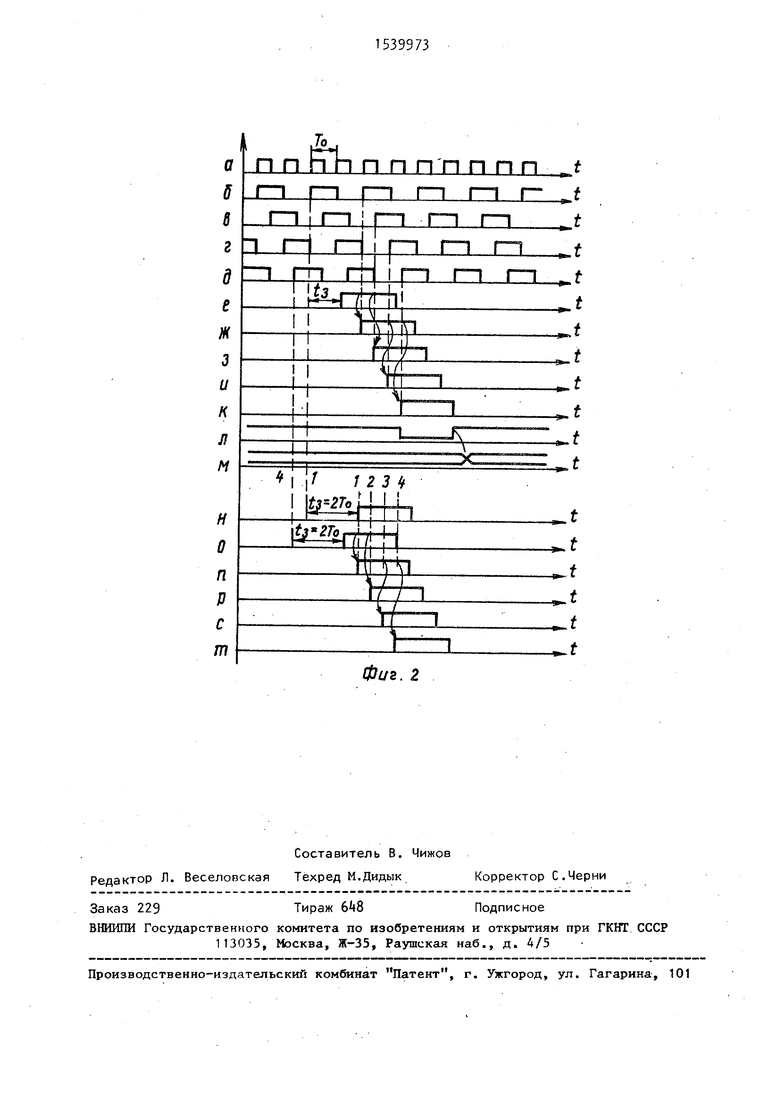

На фиг, 1 представлена функциональная схема формирователя импульсных последовательностей; на фиг. 2 - временные диаграммы, поясняющие принцип его работы.

Формирователь импульсных последовательностей содержит (фиг„ 1) генератор 1 опорной частоты, двоичный счетчик 2, блок 3 сравнения кодов, регистр Ц памяти, программный блок 5, сумматор 6, генератор 7 сдвинутых последовательностей, переключатель 8, D-триггеры и мульти- плексор 13« Выход генератора 1 соединен с входом генератора 7, выходы генератора 7 подключены к входам переключателя 8, выход которого подсоединен к тактовому входу двоичного счетчика 2, выходы (N-2) счетчика 2 подключены к первой группе входов блока 3 сравнения кодов, вторая группа входов которого соединена с (N-2) старшими разрядами N-разрядного регистра , два младших выходных разряда (первый и второй) регистра k подключены к адресным входам (соответственно, нулевому и первому) мультиплексора 13. Все N выходов ре- гистра k подключены к первой группе входов сумматора 6, вторая группа (разрядностью N) входов которого соединена с выходами программного блока 5. Выходы сумматора 6 (N разрядов) соединены с входами регистра Ь, выход блока 3 сравнения кодов соединен с информационными входами триггеров 9 и 10, выход (прямой) триггер 9 соединен с информационными входами триггеров 11 и 12, тактовые входы триггеров соединены соответственно с первым-четвертым выходами генератора 7, прямые выходы триггеров соединены соответственно с первым-четвертым информационными входами мультиплексора 13, инверсный выход триггера 12 подключен к входу программного блока 5. Выходной шиной

.

Q Q 5

5

устройства является выход мультиплексора 13

Генератор 1 формирует меандровый сигнал.

Переключатель 8 имеет организацию х1, т„е0 осуществляет коммутацию одной из четырех линий с выходной линией о Этот переключатель позволяет учесть реальные задержки распространения сигналов, зависящие от типа применяемых интегральных схем при конкретной реализации устройства

Регистр 4 является синхронным регистром памяти, запись информации в него осуществляется по поступлении переднего фронта сигнала, поступающего на вход синхронизации.

Двоичный счетчик 2 и блок 3 сравнения кодов имеют разрядность N-2, a программный блок.5, регистр памяти k и сумматор 6 - разрядность N.

Генератор 7 при подаче на его вход меандрового сигнала формирует на своем выходе четыре сдвинутые (на половину периода тактового сигнала) последовательности (две прямые, две инверсные) „ Первая из четырех последовательностей выбирается условно, так как все они равноценны и циклически взаимозаменяемы.

Программный блок 5 предназначен для задания кодов временных интервалов между импульсами в формируемых последовательностях и может состоять, например, из двоичного счетчика, работающего по переднему фронту сигнала синхронизации, и постоянного запоминающего устройства (ПЗУ)„

Формирователь импульсных последовательностей работает следующим образом

С выхода генератора 1 сигнал опорной частоты (фиг. 2, а) поступает на вход генератора 7 сдвинутых последовательностей, который формирует импульсные последовательности (фиг. 2, б, в, г, д), сдвинутые по фазе на 1/2 периода тактовой частоты (фиг.2, а).

Одна из последовательностей, например первая,поступает на тактовый вход счетчика 2„ С выхода счетчика 2 динамически меняющийся двоичный (N-2)-разрядный код поступает на блок 3 сравнения кодов,, С другой стороны на этот блок поступает статический двоичный также (N-2)-разрядный код с выхода регистра +. В момент совпадения этих кодов на выходе блока 3 сравнения кодов появляется импульс.

Импульс (фиг. 2, е) имеет длительность, равную двум периодам опорной частоты, и некоторую задержку относительно фронта первой последовательности, являющейся тактовым сигналом для счетчика 2. Эта задержка складывается из задержек в счетчике 2 и блоке 3 сравнения кодов и зависит от типа используемых микросхем.

Пусть эта задержка tj (фиг. 2, е) такова, что передний фронт первой последовательности попадает приблизительно в середину импульса с выхода блока 3 сравнения кодов. При этом триггеры 9 и 10 (фиг. 2, ж, з) осуществляют надежную временную привязку импульса к передним фронтам соответственно первой и второй импульсных последовательностей, поступающих на тактовые входы этих триггеров.

Импульс с выхода триггера 9 далее поступает на информационные входы триггеров 11 и 12, которые также осуществляют надежную фиксацию временного положения импульса (фиг, 2, и, к) по передним фронтам соответственно третьей и четвертой импульсной последовательности с выходов генератора 7

Следующими (после окончания импульса с выхода блока 3 сравнения кодов) передними фронтами импульсных последовательностей с выходов генератора 7 триггеры 9-12 сбрасываются в исходное нулевое состояние, так как на их информационных входах к этим моментам единичный сигнал уже отсутствует.

В результате один импульс с выхода блока 3 сравнения кодов (фиг. 2, е) . оказывается расщепленным на четыре импульса (фиг. 2, ж, з, и, к), сдвинутые по фазе на половину периода опорной частоты один относительно

другого.

Задачу выбора из четырех импульсов одного, соответствующего заданному временному интервалу, выполняет мультиплексор 13. Кодовая комбинация на его адресных входах определяет номер информационного входа, сигнал которого передается на выход мультиплексора,, Импульс с выхода мультиплексора 13 поступает на выходную шину устройства и является выходным импульсом формирователя.

Импульс с инверсного выхода триггера 12 (фиг„ 2, л) подается на вход

0

5

0

5

синхронизации регистра fl и на вход программного блока 5

По переднему фронту згого импульса в регистр записывается двоичный код, который определяет временное положение очередного формируемого импульса о

Двоичный код, записываемый в регистр k, образуемся с помощью сумматора 6. На первую группу входов сумматора подается код предыдущего импульса с выхода регистра , Этот код определяет временное положение импульса с момента естественного об нуления счетчика 2, На другую группу входов сумматора поступает код с программного блока 5-. Этот код определяет величину формируемого временно го интервала между соседними импульсами. На выходе сумматора 6 образуется двоичный ксп. который задает временное расстояние от момента естественного обнуления счетчика 2 до момента формирования очередного импульса на выходе устройства о

Смена кода на выходах программного блока 5 (фиг. 2, м) происходит также в результате прихода переднего фронта сигнала с инверсного выхода триггера 12 (фиг. 2. л).

Таким образом, с помощью импульса с выхода триггера 12 в регистр А записывается код временного положения очередного формируемого импульса, а на выходах программного блока 5 выс тавляется код уже следующего за формируемым временного интервала

Причем переключение каналов мультиплексора 13 осуществляется сразу после смены кода на выходе регистра k, т.е. в тот момент, когда все импульсы на информационных входах мультиплексора 13 уже закончились. На информационных входах мультиплексора 13 сигналы отсутствуют, все входы имеют состояние логического нуля, поэтому переключение каналов не пои- водит к появлению ложных импульсов на его выходе и, следовательно, не вносит сбоев в работу формирователя импульсных последовательностей.

Задержки распространения в счетчике 2 и блоке 3 сравнения кодов приводят к появлению постоянной задержки

0

0

5

0

5

tj (фиг. 2, е) между передним фронтом первой последовательности и импульсом на выходе блока 3 сравнения- кодов. В зависимости от типа применяемых микросхем эта задержка может быть различна. В том случае (фиг.2,н) если задержка окажется равной или близкой к двум периодам опорной частоты Т0 (фиг. 2, а), могут возникнуть сбои в работе триггера 9 (ввиду совпадения передних фронтов первой последовательности и импульса с выхода блока 3 сравнения кодов). В этом случае следует поменять импульсную последовательность, поступающую на вход счетчика 2 через переключатель 8, таким образом (фиг. 2, о), чтобы передний фронт первой последовательности вновь оказался примерно посередине импульса с выхода блока 3 сравнения кодов. В данном случае (фиг. 2, о) на вход счетчика 2 через переключатель 8 следует подать четвертую импульсную последовательность. После этого дальнейшее фазовое расщепление будет проходить, как обычно (фиг. 2, п, р, с, т).

Таким образом, введение в формирователь импульсных последовательностей генератора сдвинутых последовательностей, четырех D-триггеров, переключателя и мультиплексора позволяет повысить точность формирования временных интервалов до половины периода опорной частоты.

Программный блок работает следующим образом

В ПЗУ записаны двоичные коды, величина которых определяет длительность временных интервалов между импульсами. Порядок записи кодов по возрастающим адресам соответствует порядку следования временных интервалов в выходной последовательности.

Импульсы с инверсного выхода триггера 12, поступая на тактовый вход счетчика в программном блоке, переключают адреса запоминающего устройства. В результате этого программный блок 5 последовательно выставляет на своих выходах N-разрядные параллельные двоичные коды, соответствующие временным интервалам между импульсами в последовательности.

Выходная импульсная последовательность при такой реализации программного блока будет циклически повторяться.

5

0

5

0

5

0

5

0

В данном устройстве повышена надежность при том же быстродействии за счет того, что без потерь в,точности частота опорного генератора уменьшается вдвое, а частота, поступающая на двоичный счетчик, - в четыре раза, В результате значительно улучшаются и условия работы многоразрядных блоков - двоичного счетчика и блока сравнения кодов, которые обычно являются источниками сбоев при работе на частоте, близкой к граничной.

Формула изобретения

Формирователь импульсных последовательностей, содержащий генератор опорной частоты, двоичный счетчик, выходы которого соединены с первой группой входов блока сравнения кодов, вторая группа входов которого подключена к выходам регистра памяти и к первой группе входов сумматора, вторая группа входов которого подключена к выходам программного блока, выходы сумматора соединены с разрядными входами регистра памяти, отличающийся тем ,что, с целью повышения точности формирования, в него дополнительно введены переключатель, первый, второй, третий и четвертый D-триггеры, мультиплексор и генератор сдвинутых последовательностей, вход которого подключен к выходу генератора опорной частоты, а выходы генератора сдвинутых последовательностей соединены соответственно через переключатель с входом двоичного счетчика и с С-входами и первого, второго, третьего и четвертого D-триггеров, D-входы первого и второго D-триггеров подключены к выходу блока сравнения кодов, D-входы третьего и четвертого D-триггеров пбд- ключены к прямому выходу первого D-триггера, прямые выходы D-триггеров подключены к информационным входам мультиплексора, адресные входы которого соединены с первым и вторым выходами младших разрядов регистра памяти, вход которого соединен с входом программного блока и с инверсным выходом четвертого триггера.

Фиг. 2

| название | год | авторы | номер документа |

|---|---|---|---|

| Многофазный импульсный стабилизатор | 1985 |

|

SU1265743A1 |

| Цифровой имитатор радиотелеграфного канала связи | 1985 |

|

SU1275465A1 |

| Устройство синхронизации источников сейсмических сигналов | 1991 |

|

SU1787278A3 |

| Цифровой синтезатор частоты | 1984 |

|

SU1252939A1 |

| Устройство программного управления | 1984 |

|

SU1246055A1 |

| Манипулятор частоты без разрыва фазы | 1987 |

|

SU1515384A1 |

| Устройство для регулирования скорости электродвигателя | 1984 |

|

SU1267375A1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ИНТЕРВАЛА ВРЕМЕНИ | 2000 |

|

RU2173934C1 |

| Цифровой интерполяционный фильтр | 1990 |

|

SU1728962A1 |

| Цифровой следящий электропривод | 1981 |

|

SU1008703A1 |

Изобретение относится к автоматике, цифровой технике и измерительной технике и может быть использовано для формирования точных временных интервалов с помощью импульсных последовательностей. Целью изобретения является повышение точности формирования импульсных последовательностей. Устройство содержит генератор 1 опорной частоты, двоичный счетчик 2, блок 3 сравнения кодов, регистр 4 памяти, сумматор 6 и программный блок 5. Введение в формирователь импульсных последовательностей генератора 7 сдвинутых последовательностей, переключателя 8, D - триггеров 9-12, мультиплексора 13 позволяет повысить точность временной установки импульсов в последовательности до половины периода опорной частоты. 2 ил.

| СПОСОБ ИЗГОТОВЛЕНИЯ ЧЕРТЕЖЕЙ ДЛЯ ОДНООБРАЗНОЙ РАСКРОЙКИ ПРЕДМЕТОВ ОДЕЖДЫ | 1919 |

|

SU287A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| ( ФОРМИРОВАТЕЛЬ ИМПУЛЬСНЫХ ПОСЛЕДОВАТЕЛЬНОСТЕЙ | |||

Авторы

Даты

1990-01-30—Публикация

1988-05-05—Подача