Логический импульсный дискриминатор совпадения предназначен для использования в устройствах автоматики и вычислительной техники, Б которых для решения поставленной задачи необходимо контролировать совпадение моментов поступления импульсов, имеющих одинаковые порядковые номера в двух непрерывных последовательностях импульсов, при возникающих между ними в рабочем режиме временных рассогласованиях до нескольких периодов повторения импульсов.

Известен логический импульсный дискриминатор, содержащий два кольцевых счетчика, логические схемы фиксации совпадения и относительного расхождения на «+1 показаний кольцевых счетчиков и импульсный фазовый дискриминатор, состоящий из статического триггера и усилителя с противофазными входами и фильтрами для выделения постоянной составляющей напряжения.

Известный логический импульсный дискриминатор не выдает выходного напряжения при временном рассогласовании на полпериода между передними фронтами сравниваемых импульсов. При совпадении передпих фронтов импульсов дискриминатор вырабатывает максимальное выходное напряжение. Но так как максимальное выходное напряжение вырабатывается и при временных рассогласованиях, превыщающих полпериода, с помощью

известного логического импульсного дискриминатора невозможно однозначно контролировать совпадение моментов поступления сравниваемых импульсов. Принципиально такая зависимость выходного напряжения от временного рассогласования обусловлена тем, что в импульсном фазовом дискриминаторе управление усилителем производится сигпалами, снимаемыми с выходов одного триггера.

Целью предлагаемого изобретения является осуществление контроля совпадения моментов поступления сравниваемых импульсов при отсчете времепного рассогласования между ними относительно этого совпадения и при сохранении рабочей области дискриминационной характеристики до ±Л периодов временного рассогласования с линейным участком в прО делах +1 период.

Для этого предлагаемый логический импульсный дискриминатор совпадения дополнительно содержит логическую схему фиксации относительного расхождения на «-1 показаний кольцевых счетчиков и второй статический триггер, к первому и второму установочным входам которого подключепы соответственно выходы логических схем фиксации совпадения и относительного расхождения на «-1 показаний кольцевых счетчиков, а второй выход триггера подключен к одному из

которого подключен ко второму выходу первого статического триггера, первый и второй устаповочпые входы которого подключены соответственно к выходам логических схем фиксации совпадения и относительного расхожде НИИ на «-|-1 показаний кольцевых счетчиков. В предлагаемом логическом импульсном дискриминаторе совпадения из логических схем фиксации совпадения и относительного расхождения на «-)-1 и «-1 показаний кольцевых счетчиков и двух идентичных статических триггеров образованы две цепи для формирования напряжений соответственно па нервый или второй противофазные входы усилителя в зависимости от знака временного рассогласования между сравниваемыми импульсами. Предлагаемый логический импульсный дискриминатор совпадепия не выдает выходного напряжения при совпадении передних фронтов сравниваемых импульсов (а также при установке в исходное положение) и выраОатывает выходное напряжение соответствующей полярности, пронорциопальное временному рассогласованию, при временных рассогласованиях в пределах ±1 период и максимальное выходное напряжение соответствуюш,ей полярности при времепных рассогласованиях, преваышающих 1 период.

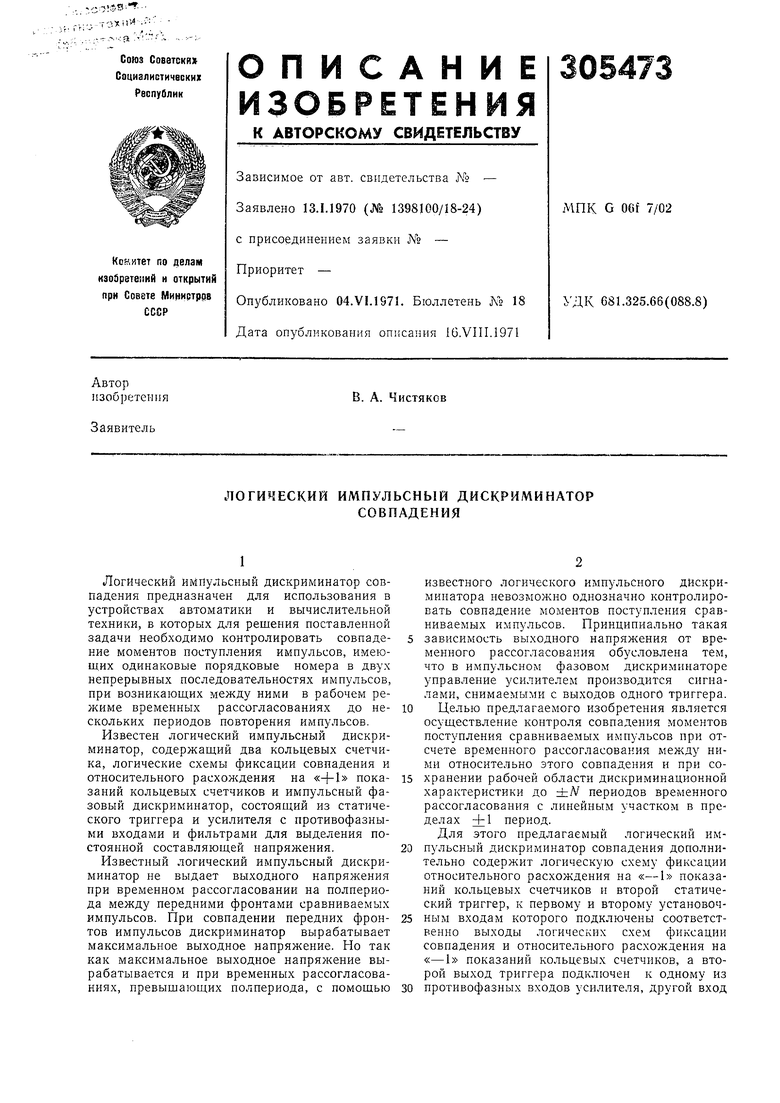

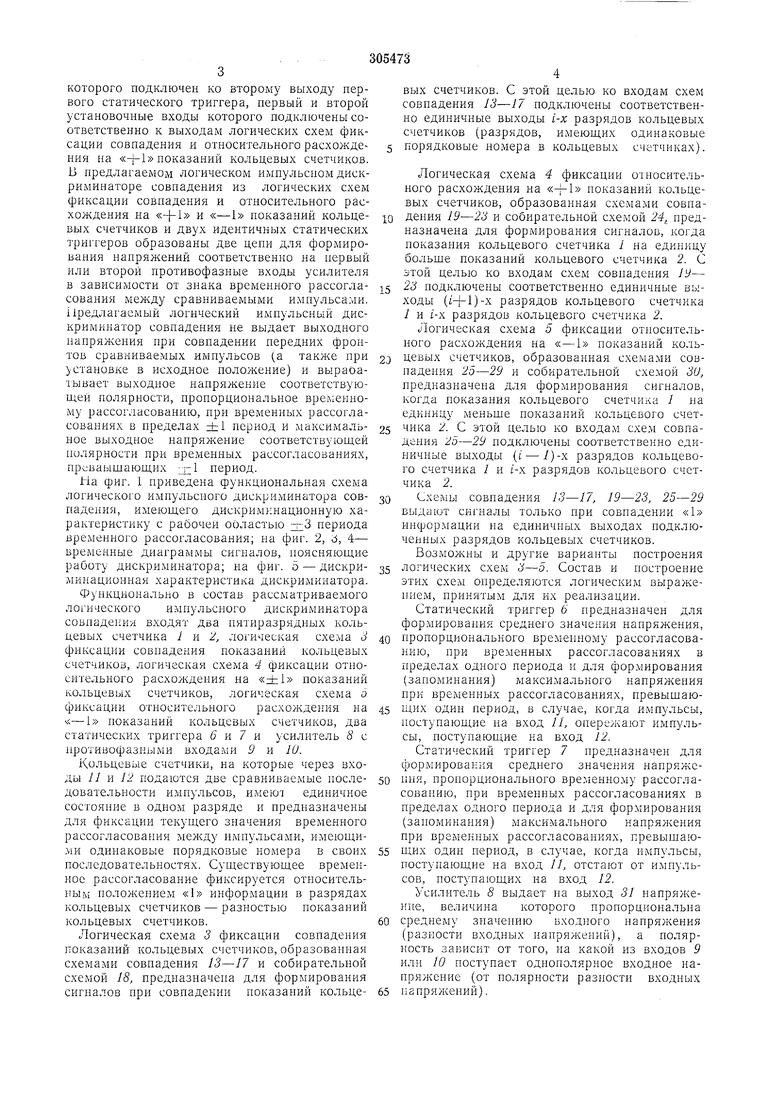

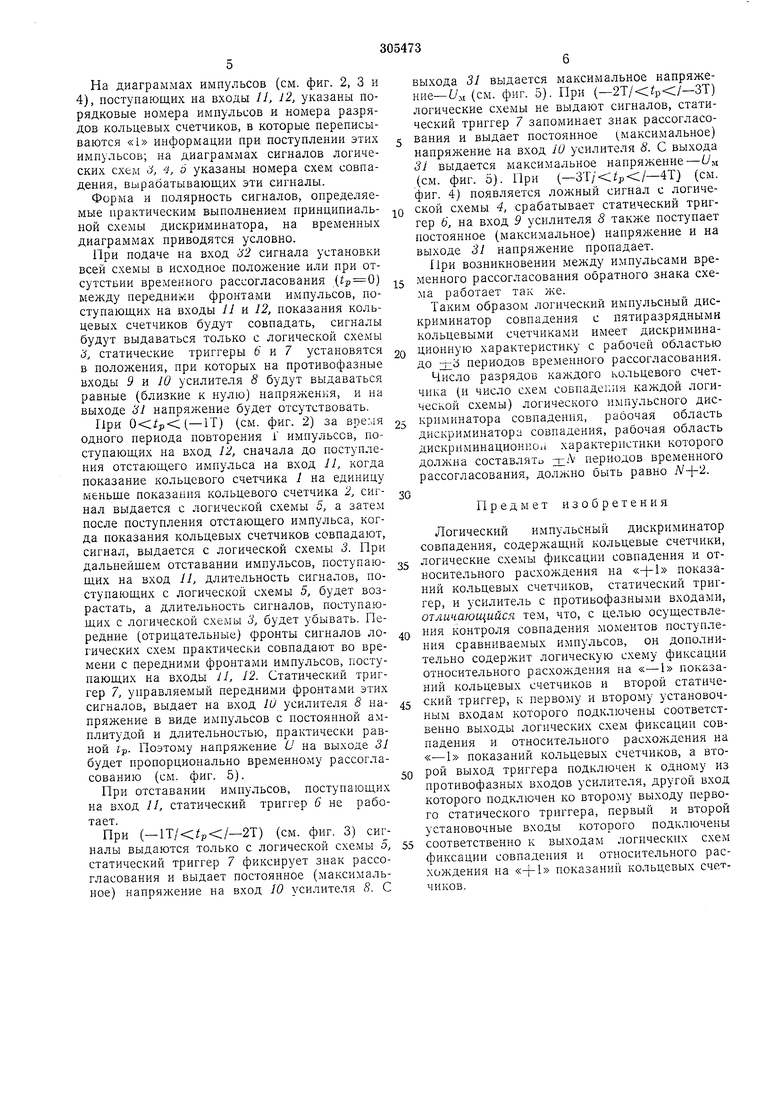

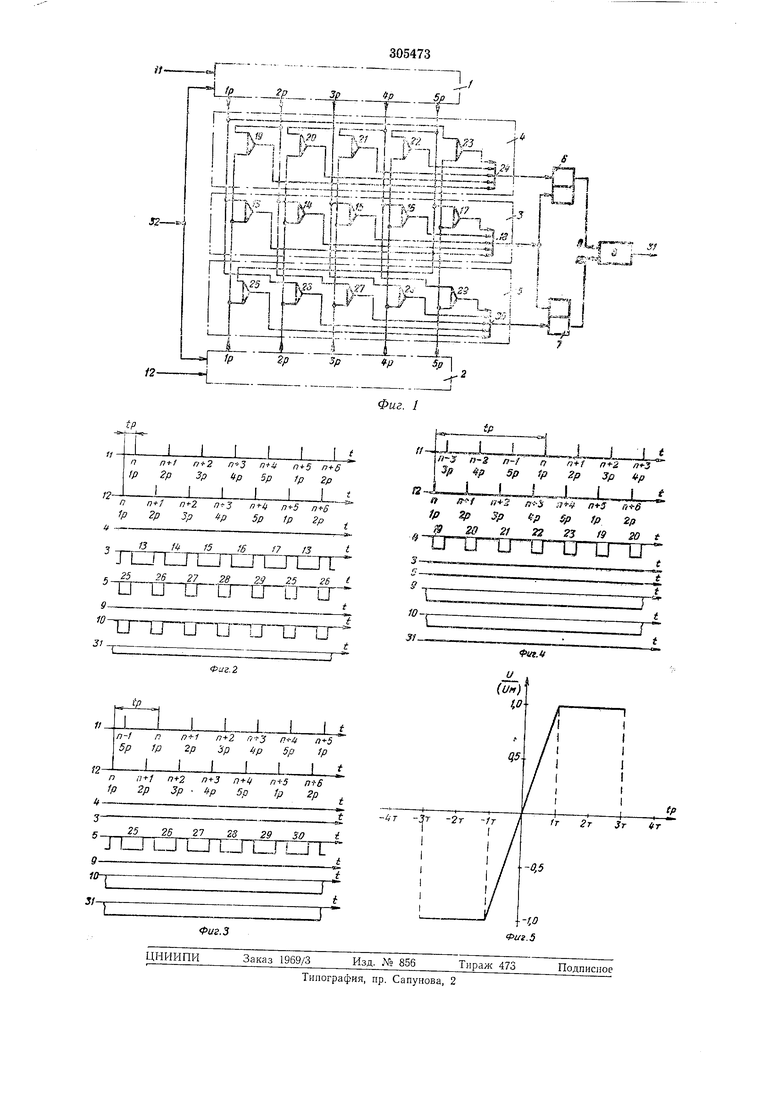

На фиг. 1 приведена функциональная схема логического импульсного дискриминатора совпадения, имеющего дискриминационную характеристику с рабочей O0vlacтью -р-З периода временного рассогласования; на фиг. 2, а, 4- временные диаграммы сигналов, поясняющие работу дискриминатора; на фиг. 5 - дискриминационная характеристика дискриминатора.

Функционально в состав рассматриваемого логического импульсного дискриминатора совпадения входят два пятиразрядных кольцевых счетчика 1 и 2, логическая схема J фиксации совпадения показаний кольцевых счетчиков, логическая схема 4 фиксации относительного расхождения на «±1 показаний кольцевых счетчиков, логическая схема о фиксации относительного расхождения на показаний кольцевых счетчиков, два статических триггера 6 и 7 и усилитель 8 с противофазными входами 9 и 10.

Кольцевые счетчики, на которые через входы 11 и 12 подаются две сравниваемые последовательности импульсов, имеют единичное состояние в одном разряде и предназначены для фиксации текущего значения временного рассогласования между импульсами, имеющими одинаковые порядковые номера в своих последовательностях. Существующее временное рассогласование фиксируется относительным ноложением «1 информации в разрядах кольцевых счетчиков - разностью показаний кольцевых счетчиков.

Логическая схема 3 фиксации совпадения показаний ко.тьцевых счетчиков, образованная схемами совпадения 13-17 и собирательной схемой 18, предназначена для формирования сигналов при совпадении показапий кольцевых счетчиков. С этой целью ко входам схем совпадения 13-17 подключены соответственно единичные выходы i-x разрядов кольцевых счетчиков (разрядов, имеющих одинаковые порядковые номера в кольцевых счетчиках).

Логическая схема 4 фиксации относительного расхождения па «-р1 показаний кольцевых счетчиков, образованная схемами совпадения 19-23 и собирательной схемой 24 предназначена для формирования сигналов, когда показания кольцевого счетчика 1 на единицу больше показаний кольцевого счетчика 2. С этой целью ко входам схем совпадения УУ-

23 подключены соответственно единичные выходы ()-x разрядов кольцевого счетчика 1 и i-x разрядов кольцевого счетчика 2.

Логическая схема 5 фиксации относительного расхождения на «-1 показаний кольцевых счетчиков, образованная схемами совпадепия 25-29 и собирательной схемой 30, предназначена для формирования сигналов, когда показания кольцевого счетчика / на единицу меньгпе показаний кольцевого счетчика 2. С этой целью ко входам схем совпадения 25-29 подключены соответственно единичные выходы (i - 1)-х разрядов кольцевого счетчика / и t-x разрядов кольцевого счетчика 2.

Схемы совпадения 13-17, 19-23, 25-29 выдают сигналы только при совпадении «1 информации на единичных выходах подключенных разрядов кольцевых счетчиков.

Возможны и другие варианты построения

логических схем 3-5. Состав и построепие этих схем определяются логическим выражением, принятым для их реализации.

Статический триггер 6 предназначен для формирования среднего значения напряжения,

пропорционального временному рассогласованию, при временных рассогласованиях в пределах одного периода и для формирования (запоминания) максимального напряжения нрп временных рассогласованиях, нревышающих один период, в случае, когда импульсы, поступающие на вход //, опережают импульсы, поступающие на вход 12.

Статический триггер 7 предназначен для формирования среднего значения папряжеПИЯ, пронорциопальпого времеппому рассогласовапию, при временных рассогласованиях в пределах одного периода и для формирования (запоминания) максимального напряжения при времепных рассогласованиях, превыщающих одип период, в случае, когда импульсы, поступающие па вход 11, отстают от импульсов, поступающих на вход 12.

Усилитель 8 выдает на выход 31 напряжение, величина которого пропорциональна

среднему значению входного напряжения (разности входпых напряжений), а полярность зависит от того, на какой из входов 9 или 10 поступает однополярное входное напряжение (от полярности разности входных

На диаграммах импульсов (см. фиг. 2, 3 и 4), поступающих на входы П, 12, указаны порядковые номера импульсов и номера разрядов кольцевых счетчиков, в которые переписываются «1 информации при поступлении этих импульсов; на диаграммах сигналов логических схем , , а указаны номера схем совпадения, вырабатывающих эти сигналы.

Форма и полярность сигналов, определяемые практическим выполнением принципиальной схемы дискриминатора, на временных диаграммах приводятся условно.

При подаче на вход 32 сигнала установки всей схемы в исходное положение или при отсутствии временного рассогласования (ip 0) между передними фронтами импульсов, поступающих на входы 11 и 12, показания кольцевых счетчиков будут совпадать, сигналы будут выдаваться только с логической схемы i, статические триггеры 6 и 7 установятся в положения, при которых на противофазные входы 9 и 10 усилителя 8 будут выдаваться равные (близкие к нулю) напряжения, и на выходе 31 напряжение будет отсутствовать.

При (-IT) (см. фиг. 2) за время одного периода повторения Г импульсов, поступающих на вход 12, сначала до поступления отстающего импульса на вход 11, когда показание кольцевого счетчика / на единицу меньще показания кольцевого счетчика 2, сигнал выдается с логической схемы 5, а зате.м после поступления отстающего импульса, когда показания кольцевых счетчиков совпадают, сигнал, выдается с логической схемы 3. При дальнейщем отставании импульсов, поступающих на вход 11, длительность сигналов, поступающих с логической схемы 5, будет возрастать, а длительность сигналов, поступающих с логической схемы 3, будет убывать. Передние (отрицательные) фронты сигналов логических схем практически совпадают во времени с передними фронтами импульсов, поступающих на входы П, 12. Статический триггер 7, управляемый передними фронтами этих сигналов, выдает на вход 10 усилителя 8 напряжение в виде импульсов с постоянной амплитудой и длительностью, практически равной ip. Поэтому напряжение U на выходе 31 будет пропорционально временному рассогласованию (см. фиг. 5).

При отставании импульсов, поступающих на вход 11, статический триггер 6 не работает.

При () (см. фиг. 3) сигналы выдаются только с логической схемы 5, статический триггер 7 фиксирует знак рассогласования и выдает постоянное (максимальное) напряжение на вход 10 усилителя 8. С

выхода 31 выдается максимальное напряжение-L/M (см. фиг. 5). При () логические схемы не выдают сигналов, статический триггер 7 запоминает знак рассогласования и выдает постоянное (.максимальное) напряжение на вход 10 усилителя 8. С выхода 31 выдается максимальное напряжение-Ьм (см. фиг. 5). При (-ЗТ/ /р /-41} (см. фиг. 4) появляется сигнал с логической схемы 4, срабатывает статический триггер 6, на вход 9 усилителя 8 также поступает постоянное (максимальное) напряжение и на выходе 31 напряжение пропадает. При возникновении между импульсами временного рассогласования обратного знака схема работает так же.

Таким образом логический импульсный дискриминатор совпадения с пятиразрядными кольцевыми счетчиками имеет дискриминадионную характеристику с рабочей областью до г6 периодов временного рассогласования. Число разрядов каждого кольцевого счетчика (и число схем совпадения каждой логической схемы) логического импульсного дискриминатора совпадения, рабочая область дискриминатора совпадения, рабочая область дискриминационной характеристики которого должна составлять периодов временного рассогласования, должно быть равно .

Предмет изобретения

Логический импульсный дискриминатор совпадения, содерл ащий кольцевые счетчики,

логические схемы фиксации совпадения и относительного расхол-;дения на показаний кольцевых счетчиков, статический триггер, и усилитель с протиьофазными входами, отличающийся тем, что, с целью осуществления контроля совпадения моментов поступления сравниваемых импульсов, он дополнительно содержит логическую схему фиксации относительного расхолчдения на «-1 показаний кольцевых счетчиков и второй статический триггер, к первому и второму установочным входам которого подключены соответственно вы.коды логических схем фиксации совпадения и относительного расхолхдения на «-1 показаний кольцевых счетчиков, а второй выход триггера подключен к одному из противофазных входов усилителя, другой вход которого подключен ко второму выходу первого статического триггера, первый и второй установочные входы которого подключены

соответственно к выходам логпческих схем фиксации совпадения и относительного расхолчдения на «+1 показаний кольцевых счетчиков.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство компенсации сдвига частот | 1985 |

|

SU1316097A2 |

| Дискриминатор временного сдвигадВуХ КОгЕРЕНТНыХ СлучАйНыХ СигНАлОВ | 1979 |

|

SU807314A1 |

| Способ формирования периодических двуполярных колебаний с заданным фазовым сдвигом и устройство для его реализации | 2016 |

|

RU2625047C1 |

| ЫТ:ввитое** *У*ЬАМ. Кл. G 05Ь 11/14УДК 621.316.7(088.8) | 1973 |

|

SU408269A1 |

| Устройство для синхронизации раздельных носителей звука и изображения | 1979 |

|

SU930201A1 |

| Фазовая следящая система | 1979 |

|

SU788075A1 |

| ЦЕЗИЕВЫЙ СТАНДАРТ ЧАСТОТЫ | 1994 |

|

RU2076411C1 |

| Устройство синхронизации в одночастотных многоканальных адресных системах с временным разделением каналов | 1989 |

|

SU1811018A1 |

| ЦИФРОВОЙ ЧАСТОТНЫЙ ДИСКРИМИНАТОР | 1991 |

|

RU2040852C1 |

| Фазовый дискриминатор | 1983 |

|

SU1171970A1 |

Даты

1971-01-01—Публикация