Предложение относится к области автоматики и вычислительной техники и предназначено для использования в микроэлектронных цифровых устройствах.

Известен элемент «исключающее ИЛИ (сложение по модулю два), содержащий 14 МДП-транзисторов и использующий три ступени логической обработки информации.

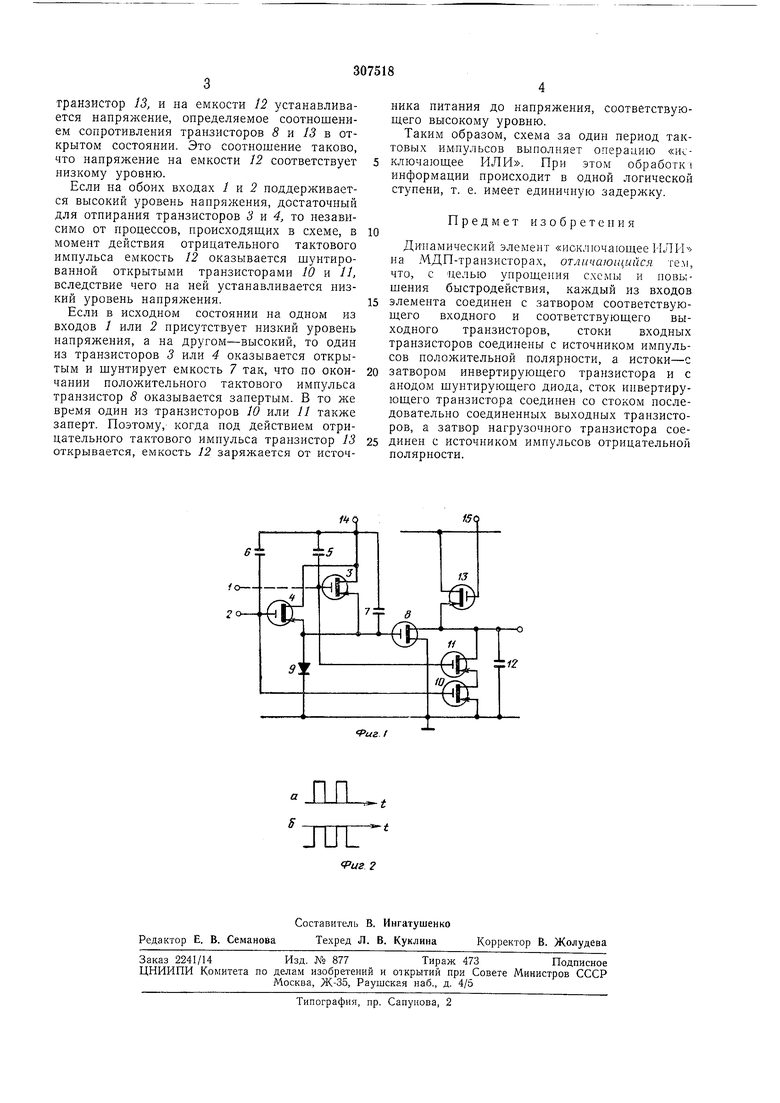

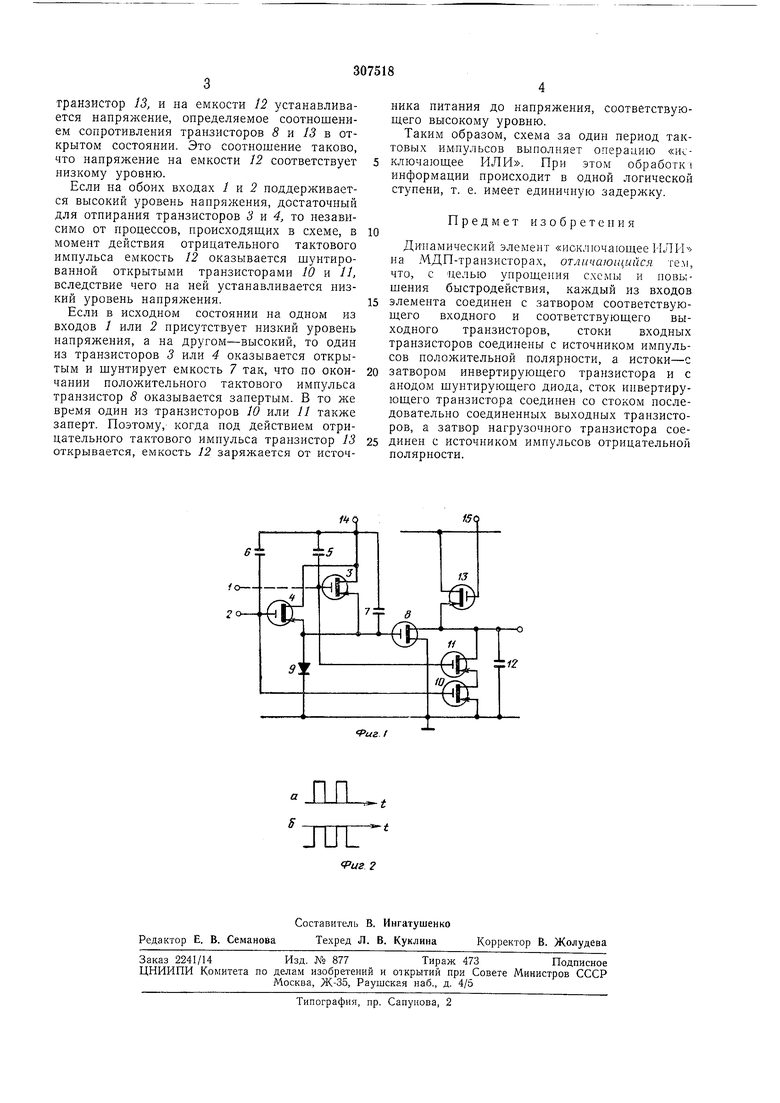

Предложенный динамический элемент отличается тем, что каждый из входов элемента соединен с затвором соответствующего входного и соответствующего выходного транзисторов. Стоки входных транзисторов соединены с источником импульсов положительной полярности, а истоки- с затвором инвертирующего транзистора и с анодом шунтирующего диода. Сток инвертирующего транзистора соединен со стоком последовательно соединенных выходных транзисторов, а затвор нагрузочного транзистора соединен с источником импульсов отрицательной полярности.

Это позволяет упростить схему элемента и повысить его быстродействие за счет уменьшения числа ступеней логической обработки информации до одной.

Устройство содержит входы / и 2, входные транзисторы 3 а 4 с паразитными емкостями 5 и 6 исток-затвор соответственно и с общей паразитной емкостью (конденсатором) 7 исток-сток, инвертирующий транзистор 8 и щуитирующий его диод 9, выходные транзисгоры 10 V. 11 с общей паразитной емкостью 12 исток-сток, нагрузочный транзистор 13 и шины 14 и 15 для подачи тактовых импульсов положительной и отрицательной полярности соответственно.

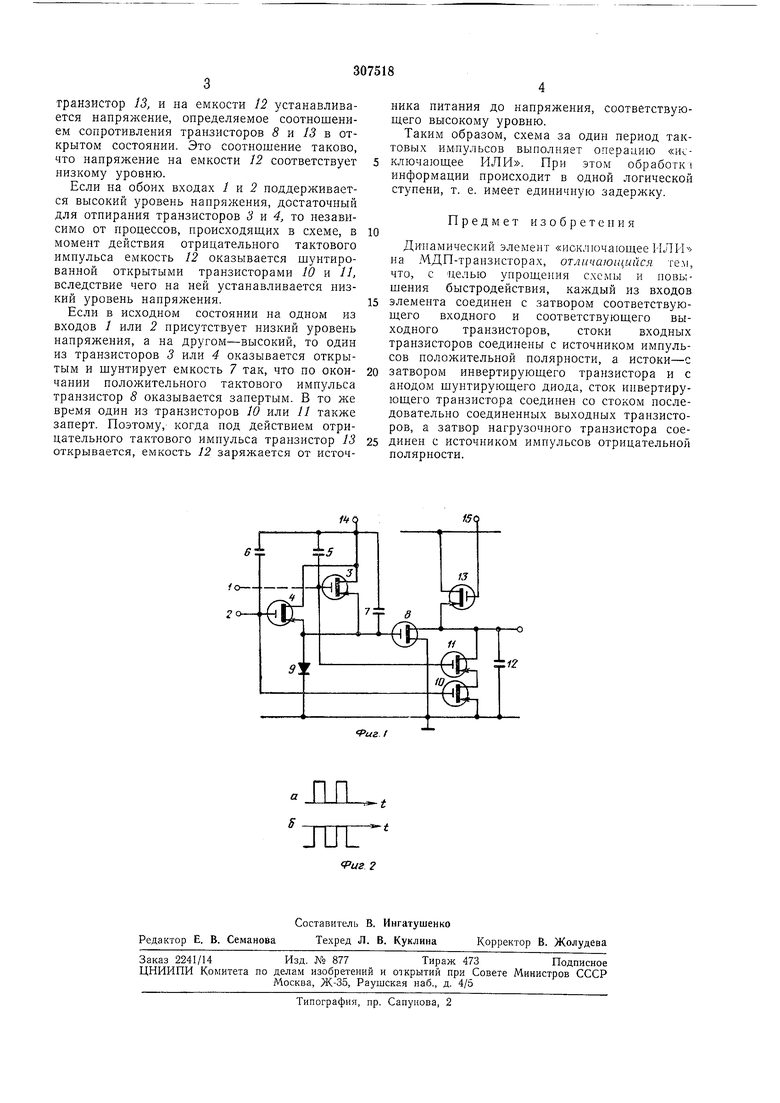

Устройство работает следующим образом. Пусть в исходном состоянии на обоих входах 1 2 поддерживается низкий потенциал,

недостаточный для отпирания транзисторов 3 и 4, а также транзисторов 10 и //. Тактовый импульс положительной полярности через шину 14 заряжает конденсатор 7 через диод 9 и, действуя через емкости 5 и 5 на затворы транзисторов 3 и 4, препятствует отпиранию последних. По окончании импульса диод 9 закрывается, а положительно заряженная обкладка конденсатора 7 оказывается заземленной через внутреннее сопротивление генератора тактовых импульсов.

Таким образом, затвор инвертирующего транзистора 8 оказывается под отрицательным потенциалом, достаточным для отпирания транизстора. Орицательный тактовый имтранзистор 13, и на емкости 12 устанавливается напряжение, определяемое соотношением сопротивления транзисторов 5 и /5 в открытом состоянии. Это соотношение таково, что напряжение на емкости 12 соответствует низкому уровню.

Если на обоих входах 1 и 2 поддерживается высокий уровень напряжения, достаточный для отпирания транзисторов 3 и 4, т:о независимо от процессов, происходящих в схеме, в момент действия отрицательного тактового импульса емкость 12 оказывается шунтированной открытыми транзисторами 10 и 11, вследствие чего на ней устанавливается низкий уровень напряжения.

Если в исходном состоянии на одном из входов 1 или 2 присутствует низкий уровень напряжения, а на другом-высокий, то один из транзисторов 3 или 4 оказывается открытым и шунтирует емкость 7 так, что по окончании положительного тактового импульса транзистор 8 оказывается запертым. В то же время один из транзисторов 10 или 11 также заперт. Поэтому, когда под действием отрицательного тактового импульса транзистор 13 открывается, емкость J2 заряжается от источника питания до напряжения, соответствующего высокому уровню.

Таким образом, схема за один период тактовых имлульсов выполняет операцию «исключающее ИЛИ. При этом обработк t информации происходит в одной логической ступени, т. е. имеет единичную задержку.

Предмет изобретения

Динамический элемент «исключающее ИЛИ на МДП-транзисторах, отличающийся тем, что, с целью упрощения схемы и повышения быстродействия, каждый из входов

элемента соединен с затвором соответствующего входного и соответствующего выходного транзисторов, стоки входных транзисторов соединены с источником импульсов положительной полярности, а истоки-с

затвором инвертирующего транзистора и с анодом шунтирующего диода, сток инвертирующего транзистора соединен со стоком последовательно соединенных выходных транзисторов, а затвор нагрузочного транзистора соединен с источником импульсов отрицательной полярности.

| название | год | авторы | номер документа |

|---|---|---|---|

| ВСЕСОЮЗН.АЯйЛКНТИ-лХКг^ГЯДЯ,БИБЛИОТЕКА | 1971 |

|

SU320056A1 |

| Схема управления силовым ключом на основе БТИЗ или МДП-транзисторов | 2024 |

|

RU2825437C1 |

| Схема управления силовым ключом на основе БТИЗ или МДП-транзисторов | 2022 |

|

RU2785321C1 |

| Логический элемент "не" | 1976 |

|

SU573884A1 |

| СХЕМА УПРАВЛЕНИЯ СИЛОВЫМ КЛЮЧОМ НА ОСНОВЕ БТИЗ ИЛИ МДП-ТРАНЗИСТОРОВ | 2023 |

|

RU2806902C1 |

| Квазирезонансный преобразователь напряжения с улучшенной электромагнитной совместимостью | 2019 |

|

RU2727622C1 |

| УСТРОЙСТВО ЗАЩИТЫ ВЫВОДОВ ИНТЕГРАЛЬНЫХ СХЕМ СО СТРУКТУРОЙ МДП ОТ ЭЛЕКТРОСТАТИЧЕСКИХ РАЗРЯДОВ | 2005 |

|

RU2308146C2 |

| ЭЛЕКТРОННЫЙ КЛЮЧ С ТРАНСФОРМАТОРНОЙ РАЗВЯЗКОЙ | 2004 |

|

RU2257007C1 |

| МУЛЬТИВИ'БРАТОР НА МДП ТРАНЗИСТОРАХ | 1973 |

|

SU387502A1 |

| Способ быстрого включения силового транзистора с изолированным затвором и устройства с его использованием | 2018 |

|

RU2713559C2 |

ffQ

ЛЯ

ЛКГ

Р«г /

Даты

1971-01-01—Публикация