Изобретение относится к элементам цифровой вычислительной техники и быть использовано в интегральных схемах для широкого класса ЦВМ малого и среднего быстродействия для реализации функции «Время, «И, «ИЛИ, а также для построения динамических сдвиговых регистров.

Известны динамические повторители, содержащие входной МДП-транзистор, исток которого через диод соединен с общей щиной нитания, и занолняющий элемент.

Предлагаемое устройство отличается от известных тем, что содержит соединенные последовательно активный и нагрузочные МДПтранзисторы, а в качестве запоминающего элемента используется емкость исток-сток входного транзистора, сток которого подключен к источнику импульсного питания, а исток соединен с затвором активного транзистора. Такое выполнение устройства позволяет новысить его техн ологичность.

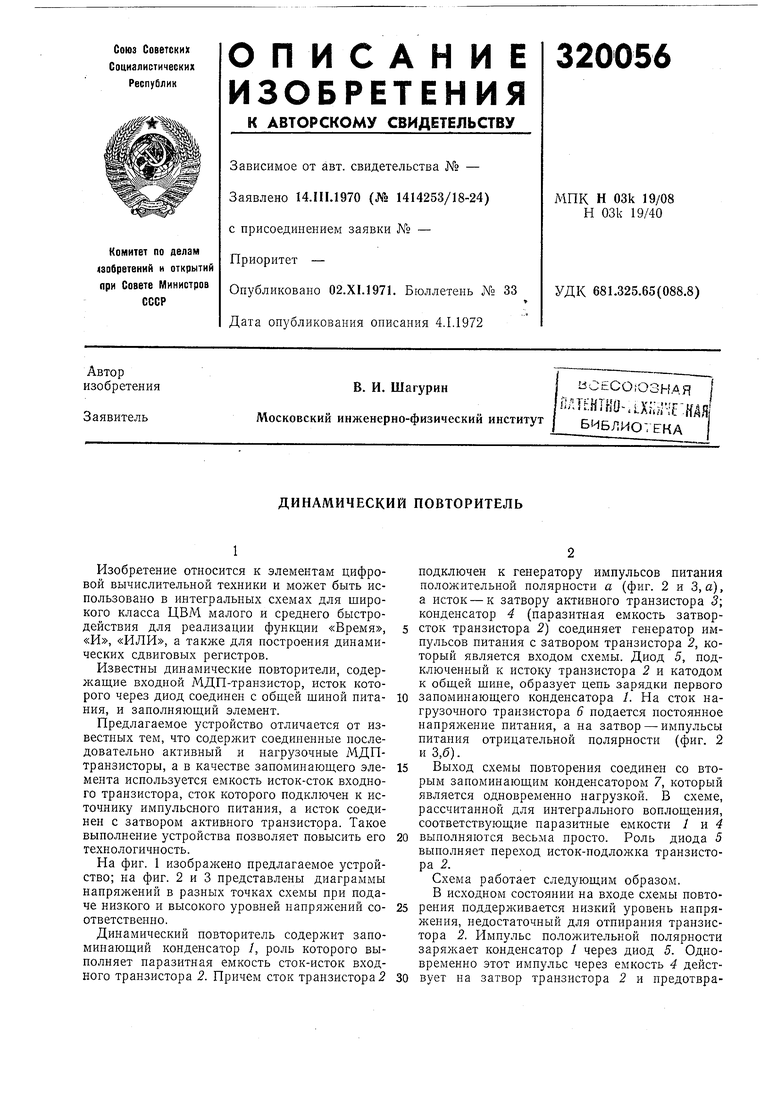

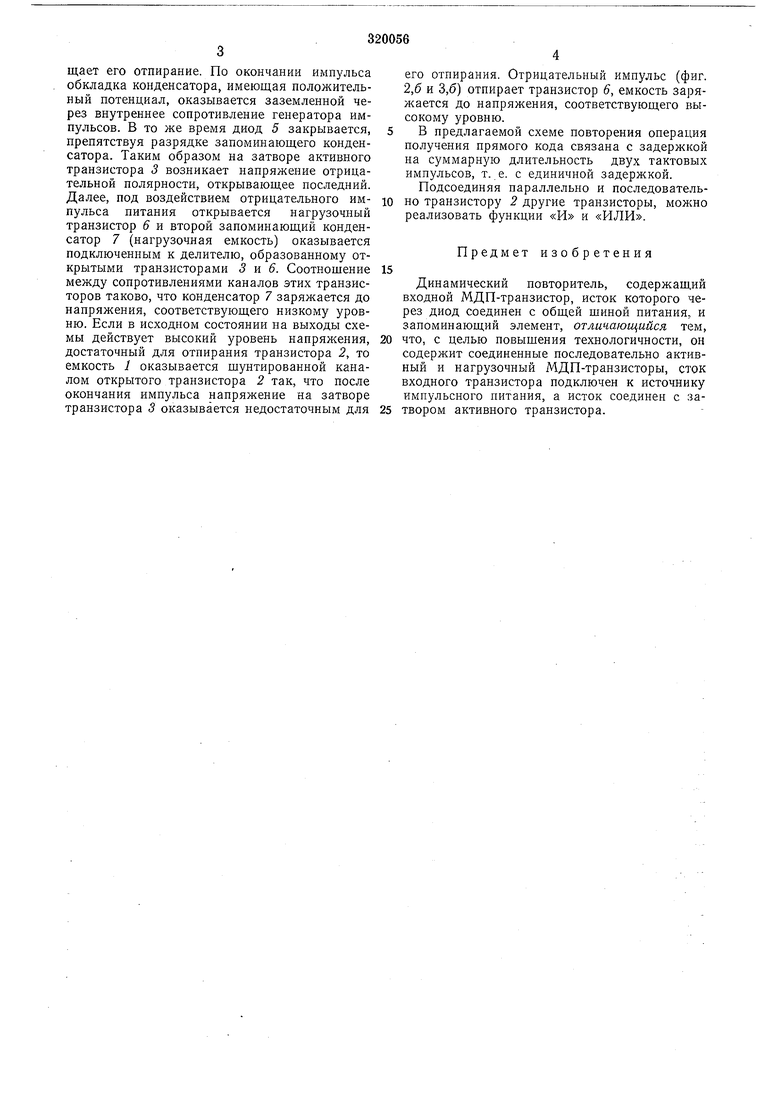

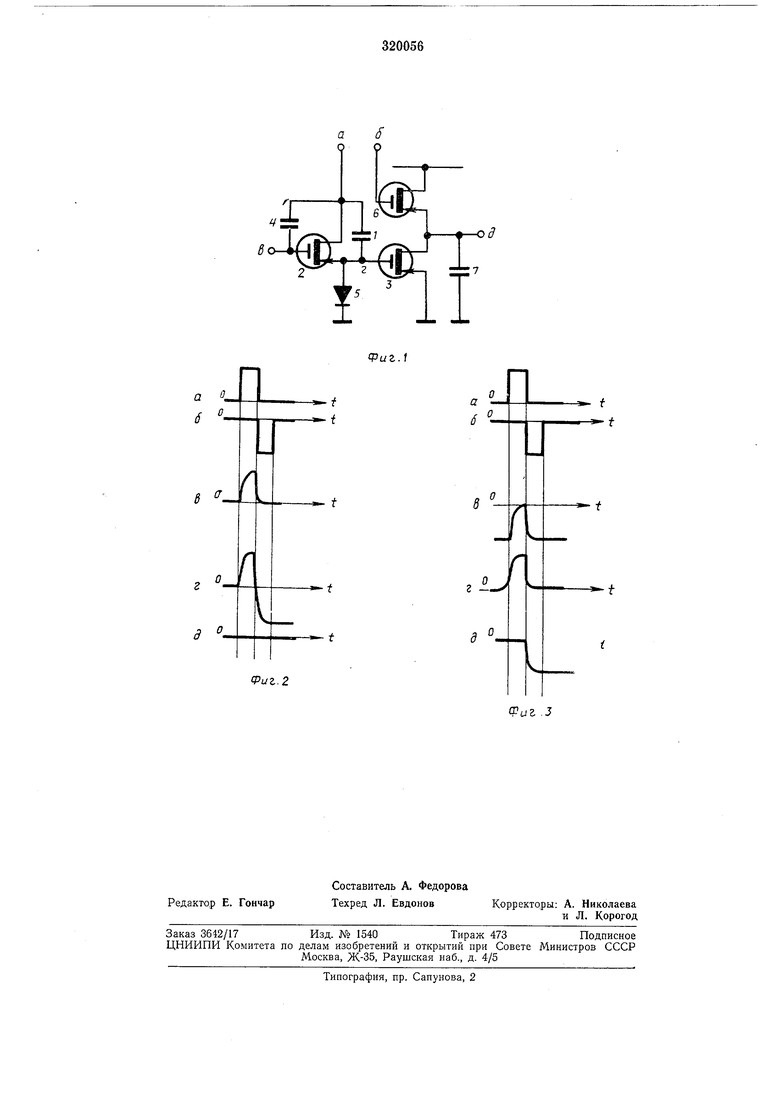

Па фиг. 1 изображено предлагаемое устройство; на фиг. 2 и 3 представлены диаграммы напряжений в разных точках схемы при нодаче низкого и высокого уровней напряжений соответственно.

Динамический повторитель содержит запоминающий конденсатор /, роль которого выполняет наразитная емкость сток-исток входного транзистора 2. Причем сток транзистора.

подключен к генератору импульсов питания положительной полярности а (фиг. 2 и 3, а), а исток - к затвору активного транзистора 3; конденсатор 4 (паразитная емкость затворсток транзистора 2) соединяет генератор импульсов питания с затвором транзистора 2, который является входом схемы. Диод 5, подключенный к истоку транзистора 2 и катодом к общей шине, образует цепь зарядки первого

запоминающего конденсатора /. На сток нагрузочного транзистора 6 подается постоянное напряжение питания, а на затвор - импульсы питания отрицательной полярности (фиг. 2 и 3,6).

Выход схемы повторения соединен со вторым заноминающим конденсатором 7, который является одновременно нагрузкой. В схеме, рассчитанной для интегрального воплощения, соответствующие паразитные емкости 1 и 4

выполняются весьма просто. Роль диода 5 выполняет переход исток-подложка транзистора 2.

Схема работает следующим образом. В исходном состоянии на входе схемы повторения поддерживается низкий уровень напряжения, недостаточный для отнирания транзистора 2. Импульс положительной полярности заряжает конденсатор / через диод 5. Одновременно этот имнульс через емкость 4 дейстщает его отпирание. По окончании импульса обкладка конденсатора, имеющая положительный потенциал, оказывается заземленной через внутреннее сопротивление генератора импульсов. В то же время диод 5 закрывается, препятствуя разрядке запоминающего конденсатора. Таким образом на затворе активного транзистора 3 возникает напряжение отрицательной полярности, открывающее последний. Далее, под воздействием отрицательного импульса питания открывается нагрузочный транзистор 6 и второй запоминающий конденсатор 7 (нагрузочная емкость) оказывается подключенным к делителю, образованному открытыми транзисторами 5 и 5. Соотношение между сопротивлениями каналов этих транзисторов таково, что конденсатор 7 заряжается до напряжения, соответствующего низкому уровню. Если в исходном состоянии на выходы схемы действует высокий уровень напряжения, достаточный для отпирания транзистора 2, то емкость 1 оказывается шунтированной каналом открытого транзистора 2 так, что после окончания импульса напряжение на затворе транзистора 3 оказывается недостаточным для

его отпирания. Отрицательный импульс (фиг. 2,6 и 3,6) отпирает транзистор 6, емкость заряжается до напряжения, соответствующего высокому уровню.

В предлагаемой схеме повторения операция

получения прямого кода связана с задержкой

на суммарную длительность двух тактовых

импульсов, т. е. с единичной задержкой.

Подсоединяя параллельно и последовательно транзистору 2 другие транзисторы, можно реализовать функции «И и «ИЛИ.

Предмет изобретения

Динамический повторитель, содержаш,ий входной МДП-транзистор, исток которого через диод соединен с общей шиной питания, и запоминающий элемент, отличающийся тем,

что, с целью повышения технологичности, он содержит соединенные последовательно активный и нагрузочный МДП-транзисторы, сток входного транзистора подключен к источнику импульсного питания, а исток соединен с затвором активного транзистора.

| название | год | авторы | номер документа |

|---|---|---|---|

| ДИНАМИЧЕСКИЙ ЭЛЕМЕНТ «ИСКЛЮЧАЮЩЕЕ ИЛИ» НА МДП-ТРАНЗИСТОРАХ | 1971 |

|

SU307518A1 |

| Адресный усилитель | 1982 |

|

SU1062786A1 |

| Формирователь сигналов выборки адресов | 1981 |

|

SU1003141A1 |

| Логический элемент "не" | 1976 |

|

SU573884A1 |

| Элемент памяти | 1984 |

|

SU1274000A1 |

| Способ быстрого включения силового транзистора с изолированным затвором и устройства с его использованием | 2018 |

|

RU2713559C2 |

| Формирователь двухполярных сигналов | 1988 |

|

SU1582372A1 |

| Схема управления силовым ключом на основе БТИЗ или МДП-транзисторов | 2022 |

|

RU2785321C1 |

| МУЛЬТИВИ'БРАТОР НА МДП ТРАНЗИСТОРАХ | 1973 |

|

SU387502A1 |

| Четырехтактный динамический регистр на мдп-транзисторах | 1973 |

|

SU438106A1 |

а о, f о

/

Фаг.2

Даты

1971-01-01—Публикация