Известны временные дискриминаторы сигнала с бинарной время-импульсной модуляцией, включающие в себя временные селекторы, интеграторы и вычитающее устройство.

Недостаток известных устройств состоит в том, что при определении величины временного рассогласования в случае сигнала с бинарной времяимпульсной модуляцией флюктуационная ошибка дискриминатора возрастает.

С целью уменьшения флюктуационной ошибки дискриминатора в предлагаемом устройстве параллельно вычитающему устройству Нодключен сумматор, а выходы вычитающего устройства и сумматора соединены с логической схемой, формирующей сигнал рассогласования.

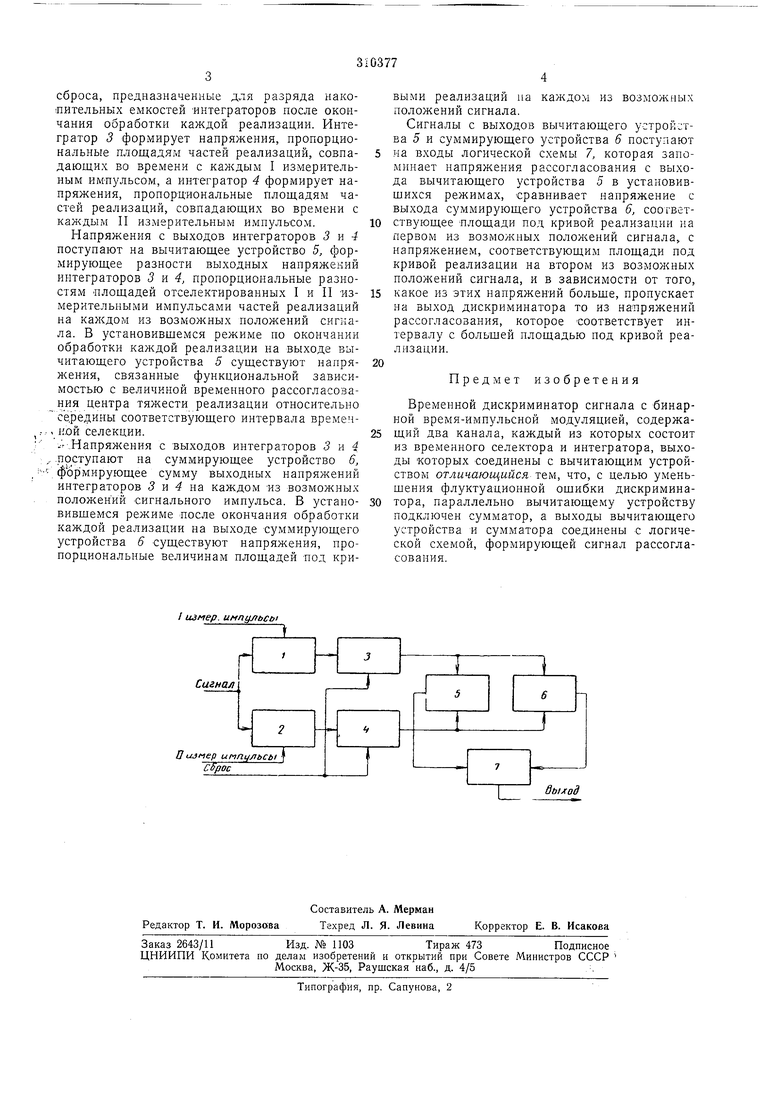

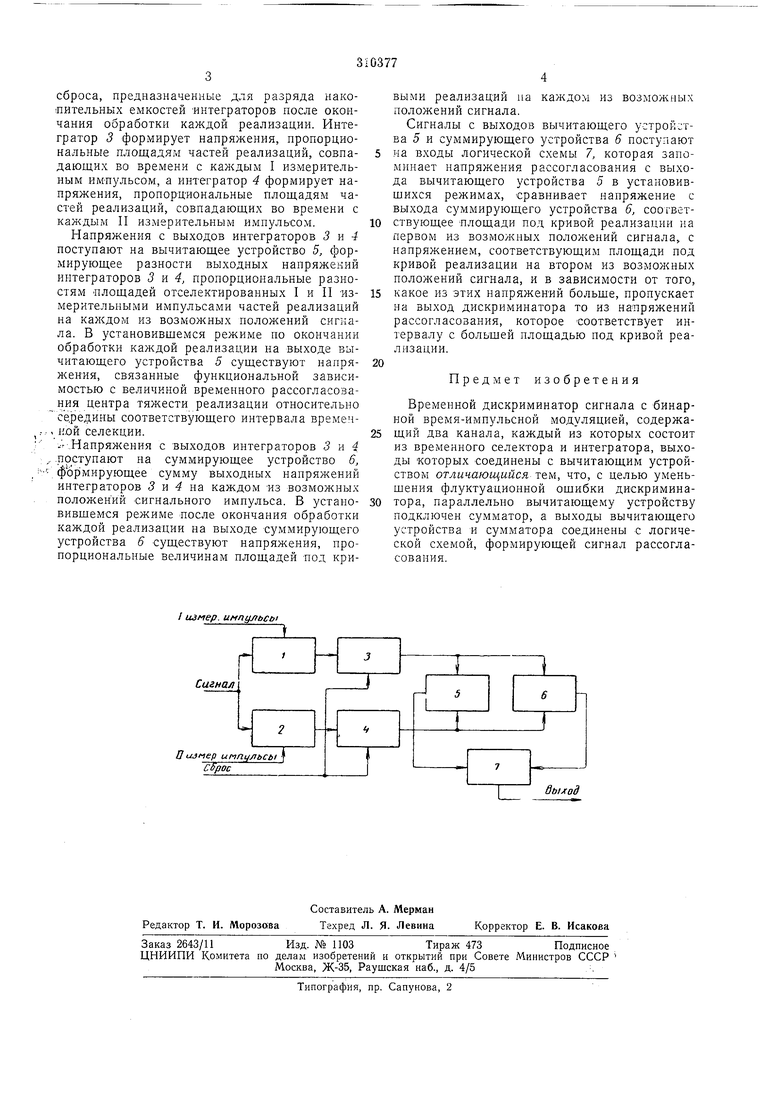

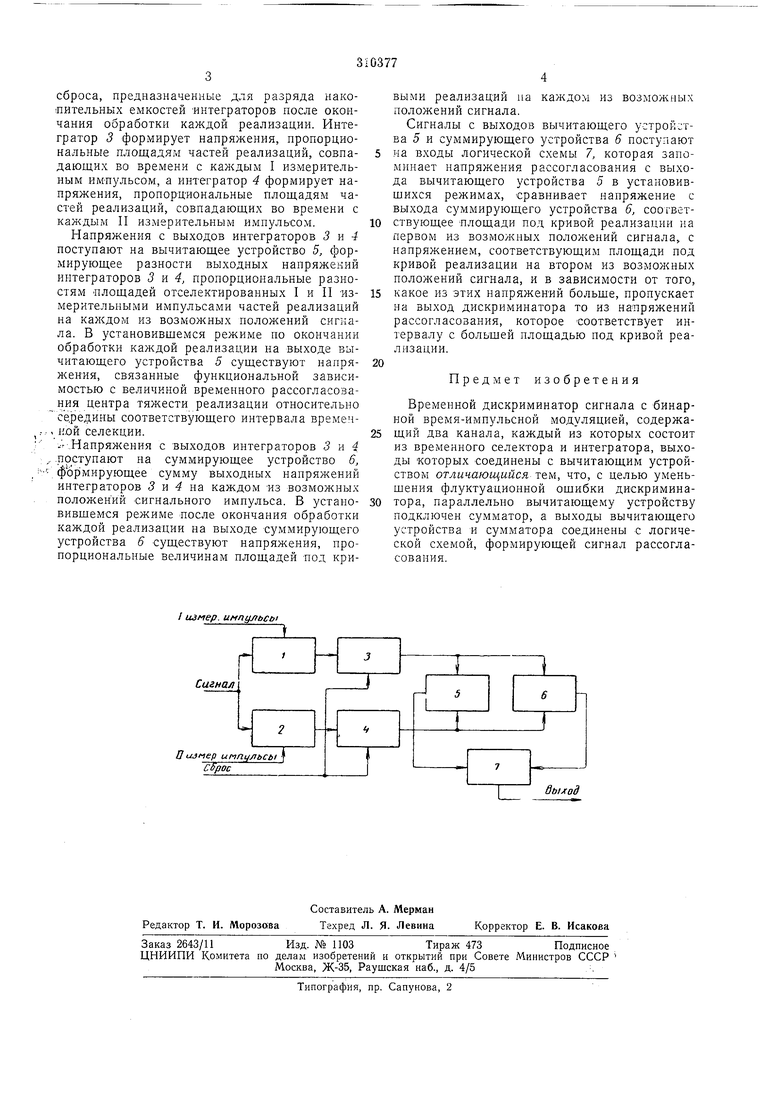

На чертеже приведена блок-схема предлагаемого устройства.

Устройство содержит временные селекторы / и 2, осуществляющие селекцию частей реализации, совпадающих во времени с I и II измерительными импульсами на каждом из возможных положений сигнального импульса, интеграторы 3 и 4, предназначенные для интегрирования отселектированных частей реализаций, вычитающее устройство 5, формирующее разность напряжений с выходов интеграторов 3 и 4, сумл1ирующее устройство 6, формирующее сумму напряжений с выходов интеграторов , логическую схему 7, которая

в зависимости от соотношения напряжений, поступающих на ее вход с выхода сум.мирующего устройства после интегрирования реализаций на каждом из возможных положений сигнала, выбирает отсчет временного рассогласования с выхода вычитающего устройства 5 на том из интервалов селекции, где, как показал анализ, присутствует сигнальный импульс.

Сигнал с бинарной времяимпульсной модуляцией, искаженный действием шумов, цоступает на временные селекторы / и 2. На временной селектор 1 также поступают два I измерительных импульса, разнесенных во времени на величину интервала ВИМ, а на временной селектор 2 - два II измерительных импульса, также разнесенных во времени на величину интервала ВИМ Каждый из II измерительных импульсов начинается сразу после

окончания соответствующего I измерительного импульса. Временные се.текторы / и 2 выделяют части реализаций, совпадающие во времени, соответственно, с каждым из I и с каждым из II измерительных импульсов.

Части реализаций, совпадающие во вре.мени с каждым из I измерительных импульсов, ноступают на интегратор 3, а части, совпадающие во времени с каждым из II измерительных импульсов - на интегратор 4. На инсброса, предназначенные для разряда накопительных емкостей интеграторов после окончания обработки каждой реализации. Интегратор 3 формирует наиряжения, иропорциональные площадям частей реализаций, совпадающих во времени с каждым I измерительным импульсом, а интегратор 4 формирует напряжения, пропорциональные площадям частей реализаций, совпадающих во времени с каждым II измерительным импульсом.

Напряжения с выходов интеграторов 5 и 4 поступают на вычитающее устройство 5, формирующее разности выходных напряжений интеграторов 3 н 4, пропорциональные разностям площадей отселектированных I и II измерительными импульсами частей реализаций на каждом из возможных положений сигнала. В установившемся режиме по окончании обработки каждой реализации на выходе вычитающего устройства 5 существуют напряжения, связанные функциональной зависимостью с величиной временного рассогласования центра тяжести реализации относительно середины соответствующего интервала времеч. н,ой селекции.

..- .Напряжения с выходов интеграторов 3 и 4 .поступают на суммирующее устройство 6, формирующее сумму выходных напряжений интеграторов 3 и 4 на каждом из возможных положений сигнального импульса. В установившемся режиме после окончания обработки каждой реализации на выходе суммирующего устройства 6 существуют напряжения, пропорциональные величинам площадей под кривыми реализации на каждом из возможных положений сигнала.

Сигналы с выходов вычитающего устройства 5 и суммирующего устройства 6 поступают

.ча входы логической схемы 7, которая запоминает напряжения рассогласования с выхода вычитающего устройства 5 в установившихся режимах, сравнивает напряжение с выхода суммирующего устройства 6, соогветствующее площади под кривой реализации на первом из возможных полол ений сигнала, с напряжением, соответствующим площади под кривой реализации на втором из возможных полон ений сигнала, и в зависимости от того,

какое из этих напряжений больше, пропускает на выход дискриминатора то из на пряжений рассогласования, которое -соответствует интервалу с большей площадью под кривой реализации.

Предмет изобретения

Временной дискриминатор сигнала с бинарной время-импульсной модуляцией, содержащий два канала, каждый из которых состоит из временного селектора и интегратора, выходы которых соединены с вычитающим устройством отличающийся тем, что, с целью уменьшения флуктуационной ошибки дискриминатора, параллельно вычитающему устройству подключен су.мматор, а выходы вычитающего устройства и сумматора соединены с логической схемой, формирующей сигнал рассогласования.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство обнаружения сигнала | 1975 |

|

SU566219A1 |

| ПАССИВНЫЙ КВАНТОВЫЙ СТАНДАРТ ЧАСТОТЫ | 1984 |

|

SU1241959A1 |

| Устройство для определения временного положения импульсных сигналов | 1984 |

|

SU1226507A2 |

| ПРИЕМНОЕ УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯХАРАКТЕРИСТИКИ ГРУППОВОГО ВРЕМЕНИЗАПАЗДЫВАНИЯ | 1972 |

|

SU428309A1 |

| УСТРОЙСТВО ОБНАРУЖЕНИЯ СИГНАЛА | 1972 |

|

SU336600A1 |

| Цифровой временной дискриминатор | 1978 |

|

SU744913A1 |

| Способ формирования частотно-модулированного сигнала и преобразования его параметров в код и устройство для его осуществления | 1989 |

|

SU1721533A1 |

| СПОСОБ И УСТРОЙСТВО ДЕМОДУЛЯЦИИ СИГНАЛОВ ГАЛИЛЕЯ С ПЕРЕМЕННОЙ БИНАРНОЙ СМЕЩЕННОЙ НЕСУЩЕЙ (ALTBOC) | 2004 |

|

RU2349049C2 |

| Следящий электропривод с компенсацией люфта | 1985 |

|

SU1273875A1 |

| Ультразвуковой измеритель скорости потока | 1985 |

|

SU1296942A1 |

/ ujfiep. импульсы

Сигнал

П ujnep иппульсь т С5рос

Даты

1971-01-01—Публикация