Изобретение относится к области измерительной техники и может быть использовано для измерения и документальной записи относительной частотной характеристики группового времени запаздывания в каналах связи на фиксированных частотах.

Известно приемное устройство для измерения характеристики групнового времени запаздывания, основанное на измерении разности фаз между огибающими сигналов, чередующимися во времепи, содержащее пепь из последовательно соединенных согласующего каскада, узла выделения измерительного сигнала и узла задержки, узел формирования синхросигналов, кварцевый генератор импульсов с делителем частоты, генератор имнульса сброса, триггер, интегратор, ключ и узел индикации с узлом документирования.

Однако известное устройство имеет недостаточную точность измерения, кроме того, нельзя обеспечить оперативную оценку и запоминание фазового сдвига.

С целью повышения точности измерения и обеспечения возможности оперативной оценки и запоминания фазового сдвига в предлагаемое устройство введены два блока фазирования, к измерительным входам которых подключен выход узла задержки, к синхронизирующим входам Первого блока непосредственно, а второго через инвертор подключен выход узла формирования синхросигналов, причем измерительные выходы обоих блоков, первого непосредственно, а второго через инвертор, а также их занрещающие выходы присоединены к введенной четырехвходовой вычитающей схеме совпадения, выход которой связан с узлом индикации непосредственно, а узлом документирования через последовательно соединенные интегратор и ключ, управляемый триггером, один из входов которого подключен к шине сброса, а другой - к запрещающему выходу второго блока фазирования, при этом к стартовому входу узла индикации через введенный узел выделения стартового сигнала

присоединен выход согласующего каскада, а его счетный вход соединен с синхронизирующим входом второго блока фазирования, к фазирующему опорному и сбросовому входам обоих блоков фазирования подключены соответственпо делитель частоты, кварцевый генератор импульсов и генератор импульса сброса, вход которого связан со вторым входом узла задержки и выходом узла выделения синхросигнала; каждый из блоков фазирования

содержит делитель частоты, ко входу которого через схему «ИЛИ подключены два временных селектора, сигнальные входы которых образуют фазирующий и опорный входы блока, к запрещающим входам первого селектора непосредственно, а второго через инвертор присоединен выход фазирующей схемы совпадения, к разрешающему входу второго селектора подключен выход запоминающего триггера, один из входов которого образует сбросовы вход блока, а другой связан с запускающей схемой совпадения, входы которой являются измерительным и синхронизирующим входами блока, при этом к входам фазирующей схемы совпадения подключены соответственно инвертированный выход делителя частоты, измерительный вход блока и фазирующий триггер, один из входов которого связан со сбросовым входом блока, а другой, являющийся запрещающим выходом блока, - с одноименным входом второго селектора, измерительным же выходом блока служит выход делителя частоты.

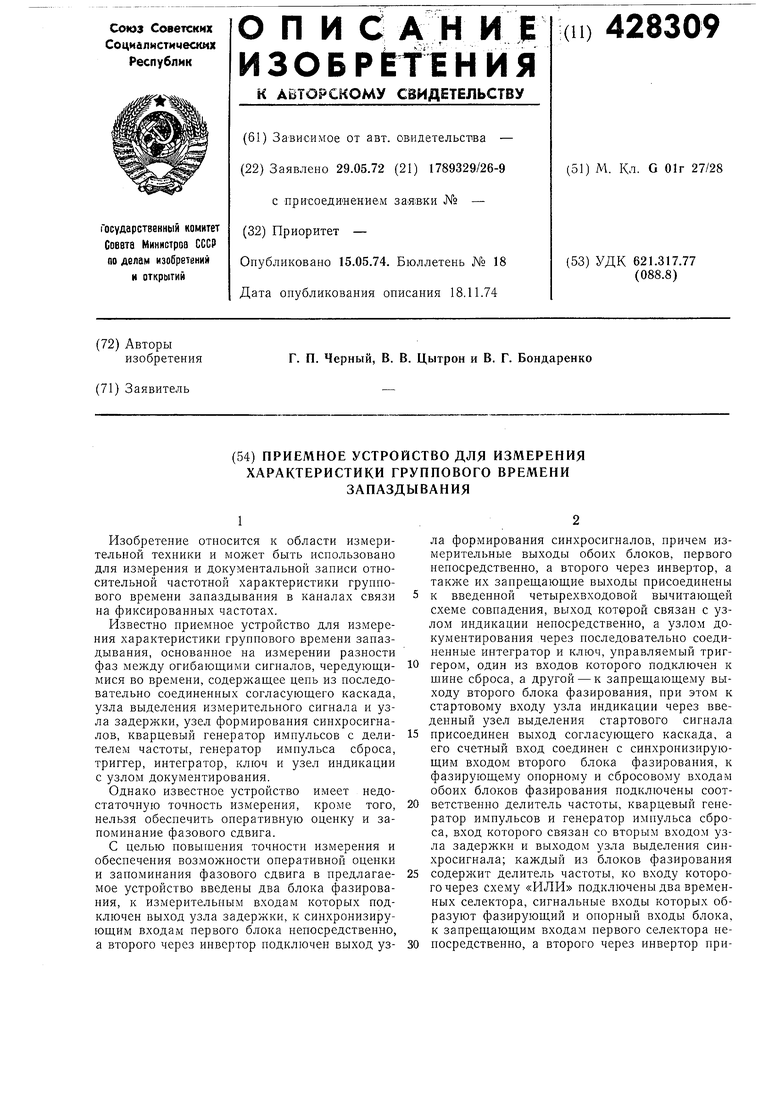

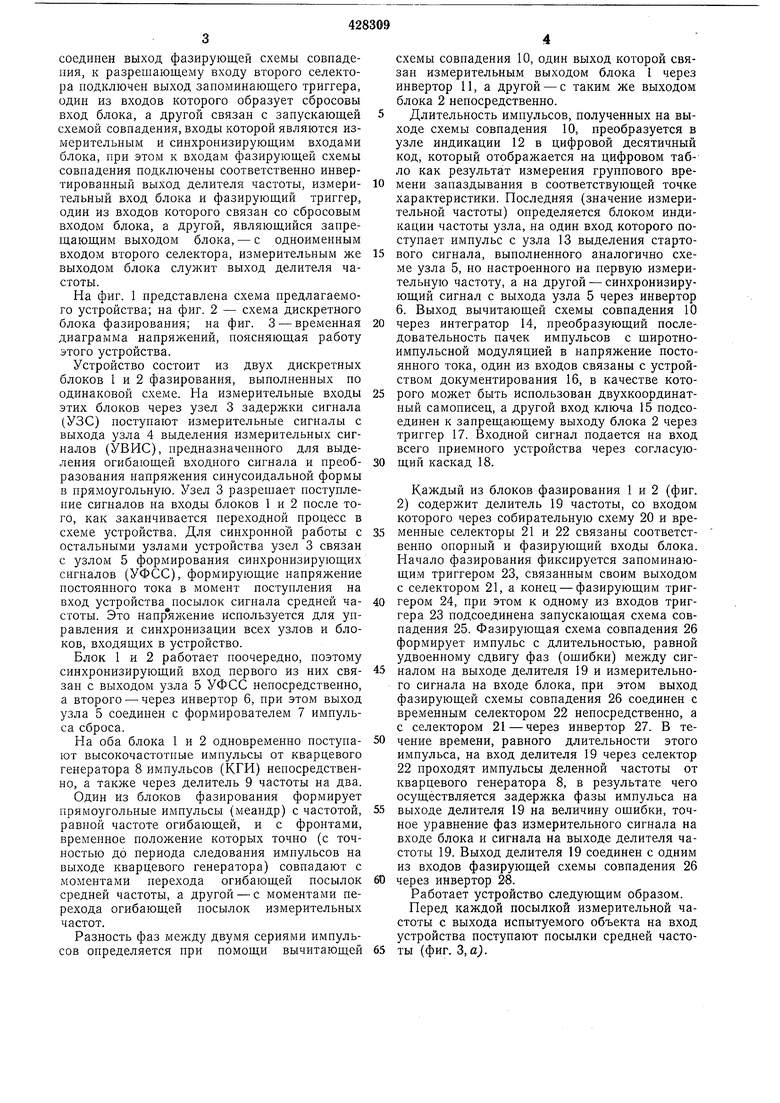

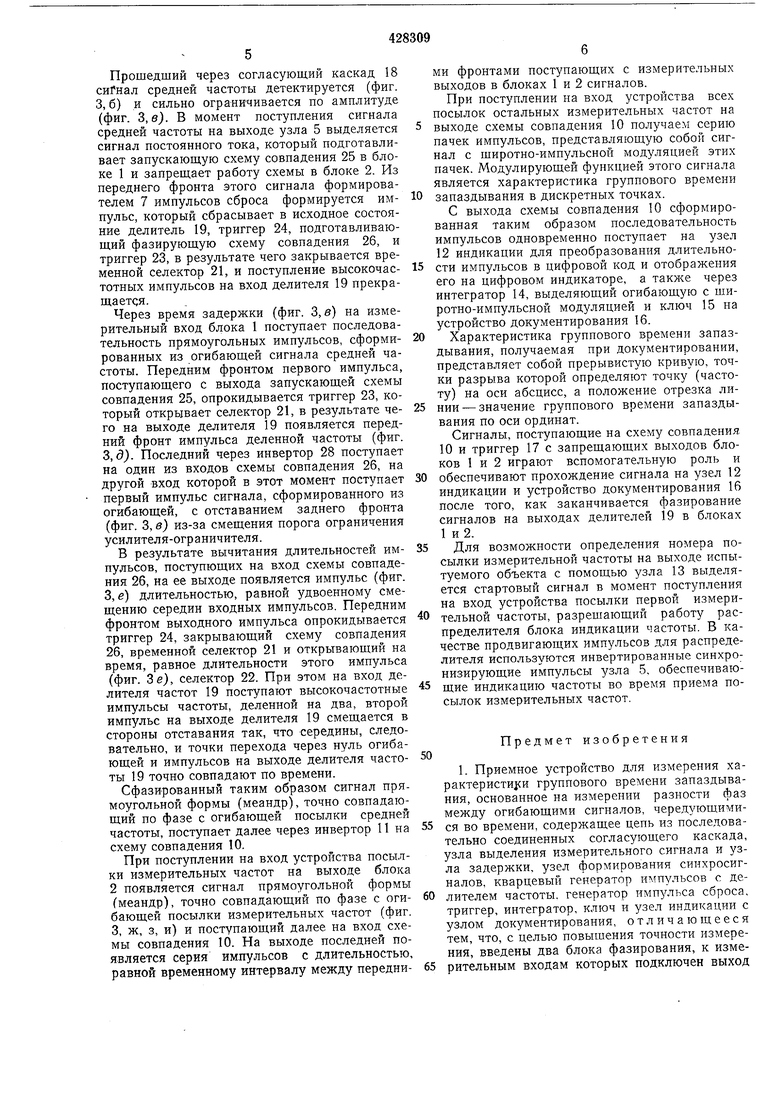

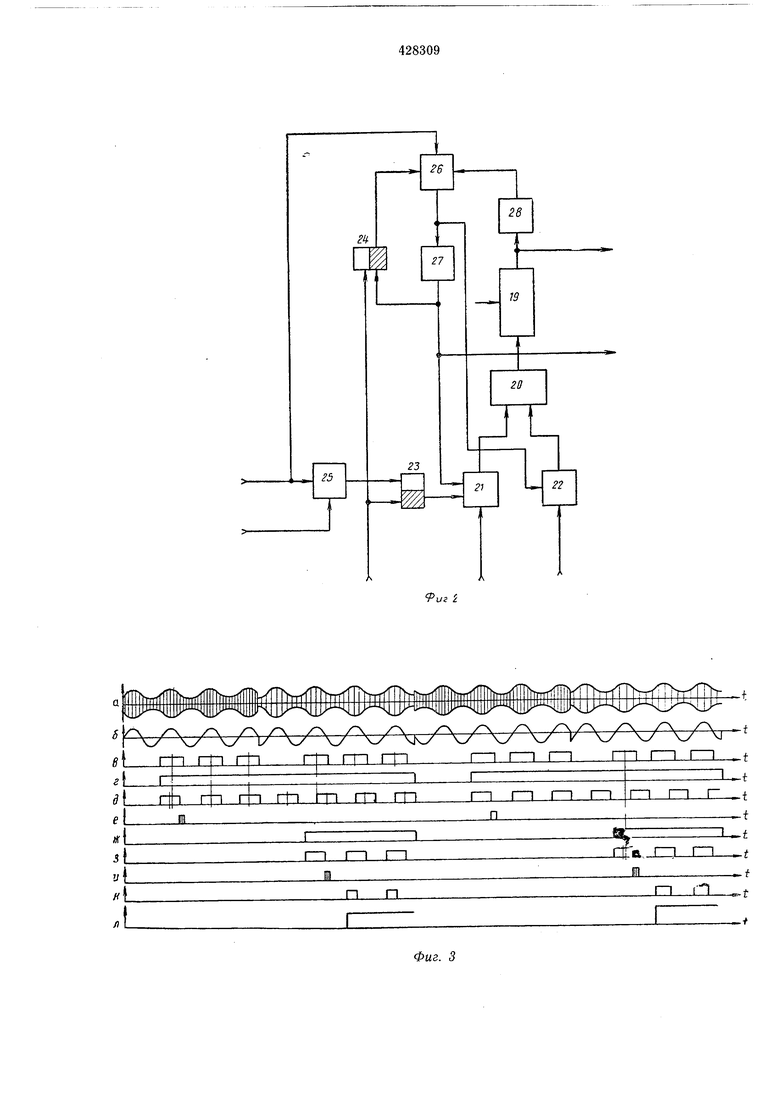

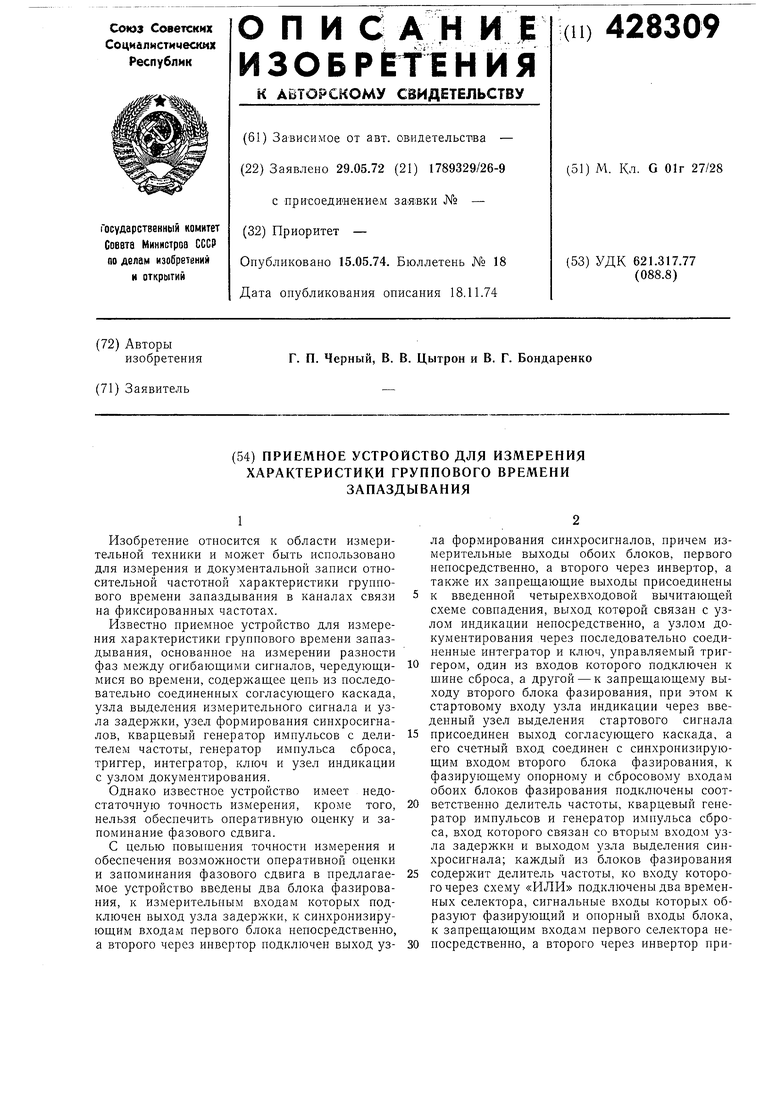

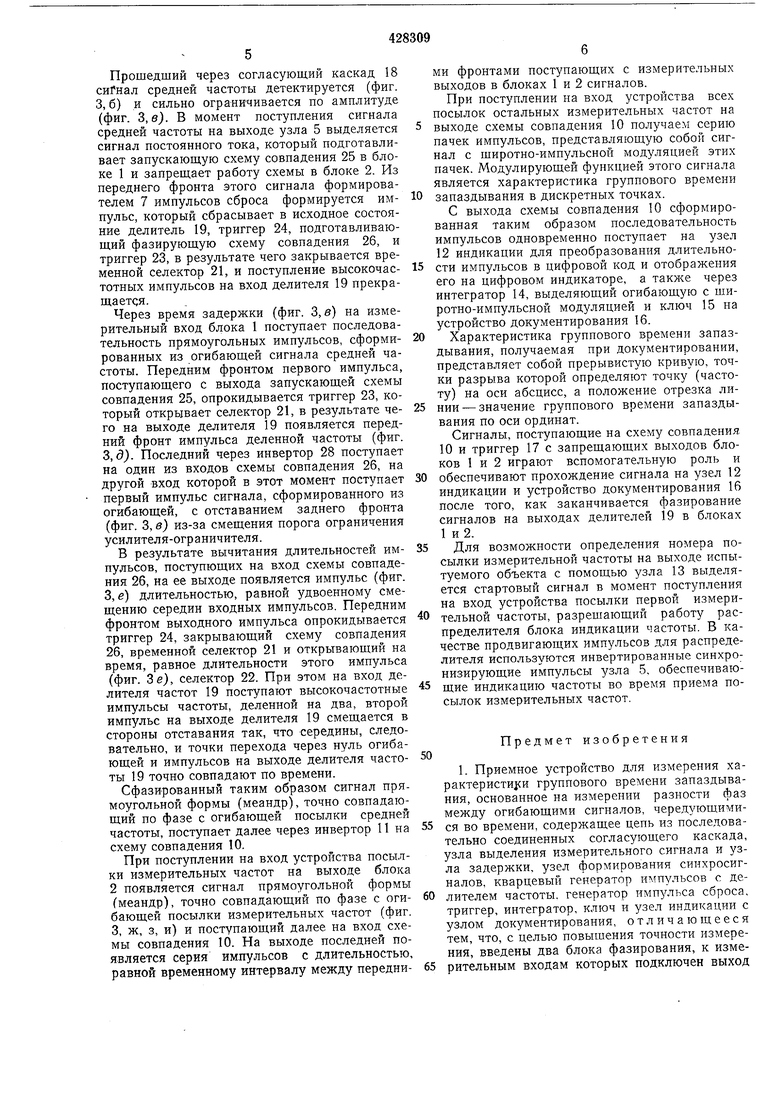

На фиг. 1 представлена схема нредлагаемого устройства; на фиг. 2 - схема дискретного блока фазирования; на фиг. 3 - временная диаграмма напряжений, поясняющая работу этого устройства.

Устройство состоит из двух дискретных блоков I и 2 фазирования, выполненных по одинаковой схеме. На измерительные входы этих блоков через узел 3 задержки сигнала (УЗС) поступают измерительные сигналы с выхода узла 4 выделения измерительных сигналов (УВИС), предназначенного для выделения огибающей входного сигнала и преобразования напряжения синусоидальной формы в прямоугольную. Узел 3 разрешает поступление сигналов на входы блоков 1 и 2 после того, как заканчивается переходной процесс в схеме устройства. Для синхронной работы с остальными узлами устройства узел 3 связан с узлом 5 формирования синхронизирующих сигналов (УФСС), формирующие напряжение постоянного тока в момент поступления на вход устройства посылок сигнала средней частоты. Это напряжение используется для управления и синхронизации всех узлов и блоков, входящих в устройство.

Блок 1 и 2 работает поочередно, поэтому синхронизирующий вход первого из них связан с выходом узла 5 УФСС непосредственно, а второго - через инвертор 6, при этом выход узла 5 соединен с формирователем 7 импульса сброса.

На оба блока 1 и 2 одновременно поступают высокочастотные импульсы от кварцевого генератора 8 импульсов (КГИ) непосредственно, а также через делитель 9 частоты на два.

Один из блоков фазирования формирует прямоугольные импульсы (меандр) с частотой, равной частоте огибающей, и с фронтами, временное положение которых точно (с точностью до периода следования импульсов на выходе кварцевого генератора) совпадают с моментами перехода огибающей посылок средней частоты, а другой - с моментами перехода огибающей посылок измерительных частот.

Разность фаз между двумя сериями импульсов определяется при помощи вычитающей

схемы совпадения 10, один выход которой связан измерительным выходом блока 1 через инвертор 11, а другой - с таким же выходом блока 2 неносредственно.

Длительность импульсов, полученных на выходе схемы совпадения 10, преобразуется в узле индикации 12 в цифровой десятичный код, который отображается на цифровом табло как результат измерения группового времени запаздывания в соответствующей точке характеристики. Последняя (значение измерительной частоты) определяется блоком индикации частоты узла, на один вход которого поступает импульс с узла 13 выделения стартового сигнала, выполненного аналогично схеме узла 5, но настроенного на первую измерительную частоту, а на другой - синхронизирующий сигнал с выхода узла 5 через инвертор 6. Выход вычитающей схемы совпадения 10 через интегратор 14, преобразующий последовательность пачек импульсов с широтноимпульсной модуляцией в напряжение постоянного тока, один из входов связаны с устройством документирования 16, в качестве которого может быть иснользован двухкоординатный самописец, а другой вход ключа 15 подсоединен к запрещающему выходу блока 2 через триггер 17. Входной сигнал подается на вход всего приемного устройства через согласующий каскад 18.

Каждый из блоков фазирования 1 и 2 (фиг. 2) содержит делитель 19 частоты, со входом которого через собирательную схему 20 и временные селекторы 21 и 22 связаны соответственно опорный и фазирующий входы блока. Начало фазирования фиксируется запоминающим триггером 23, связанным своим выходом с селектором 21, а конец - фазирующим триггером 24, при этом к одному из входов триггера 23 подсоединена запускающая схема совпадения 25. Фазирующая схема совпадения 26 формирует импульс с длительностью, равной удвоенному сдвигу фаз (ошибки) между сигналом на выходе делителя 19 и измерительного сигнала на входе блока, при этом выход фазирующей схемы совпадения 26 соединен с временным селектором 22 непосредственно, а с селектором 21-через инвертор 27. В течение времени, равного длительности этого импульса, на вход делителя 19 через селектор 22 проходят импульсы деленной частоты от кварцевого генератора 8, в результате чего осуществляется задержка фазы импульса на выходе делителя 19 на величину ошибки, точное уравнение фаз измерительного сигнала на входе блока и сигнала на выходе делителя частоты 19. Выход делителя 19 соединен с одним из входов фазирующей схемы совпадения 26 через инвертор 28.

Работает устройство следующим образом.

Неред каждой посылкой измерительной частоты с выхода испытуемого объекта на вход устройства поступают посылки средней частоты (фиг. 3,а).

Прошедший через согласуюший каскад 18 сигнал средней частоты детектируется (фиг. 3, б) и сильно ограничивается по амплитуде (фиг. 3, б). В момент поступления сигнала средней частоты на выходе узла 5 выделяется сигнал постоянного тока, который подготавливает запускающую схему совпадения 25 в блоке 1 и запрещает работу схемы в блоке 2. Из переднего фронта этого сигнала формирователем 7 импульсов сброса формируется импульс, который сбрасывает в исходное состояние делитель 19, триггер 24, подготавливающий фазирующую схему совпадения 26, и триггер 23, в результате чего закрывается временной селектор 21, и поступление высокочастотных импульсов на вход делителя 19 прекращается.

Через время задержки (фиг. 3, в) на измерительный вход блока 1 поступает последовательность прямоугольных импульсов, сформированных из огибающей сигнала средней частоты. Передним фронтом первого импульса, поступающего с выхода запускающей схемы совпадения 25, опрокидывается триггер 23, который открывает селектор 21, в результате чего на выходе делителя 19 появляется передний фронт импульса деленной частоты (фиг. 3,д). Последний через инвертор 28 поступает на один из входов схемы совпадения 26, на другой вход которой в этот момент поступает первый импульс сигнала, сформированного из огибающей, с отставанием заднего фронта (фиг. 3,0) из-за смещения порога ограничения усилителя-ограничителя.

В результате вычитания длительностей импульсов, поступющих на вход схемы совпадения 26, на ее выходе появляется импульс (фиг. 3, е) длительностью, равной удвоенному смещению середин входных импульсов. Передним фронтом выходного импульса опрокидывается триггер 24, закрывающий схему совпадения 26, временной селектор 21 и открывающий на время, равное длительности этого импульса (фиг. Зе), селектор 22. При этом на вход делителя частот 19 поступают высокочастотные импульсы частоты, деленной на два, второй импульс на выходе делителя 19 смещается в стороны отставания так, что середины, следовательно, и точки перехода через нуль огибающей и импульсов на выходе делителя частоты 19 точно совпадают по времени.

Сфазированный таким образом сигнал прямоугольной формы (меандр), точно совпадающий по фазе с огибающей посылки средней частоты, поступает далее через инвертор 11 на схему совпадения 10.

При поступлении на вход устройства посылки измерительных частот на выходе блока 2 появляется сигнал прямоугольной формы (меандр), точно совпадающий по фазе с огибающей посылки измерительных частот (фиг. 3, ж, 3, и) и поступающий далее на вход схемы совпадения 10. На выходе последней появляется серия импульсов с длительностью, равной временному интервалу между передними фронтами поступающих с измерительных выходов в блоках 1 и 2 сигналов.

При поступлении на вход устройства всех посылок остальных измерительных частот на выходе схемы совпадения 10 получаем серию пачек импульсов, представляющую собой сигнал с широтно-импульсной модуляцией этих пачек. Модулирующей функцией этого сигнала является характеристика группового времени

запаздывания в дискретных точках.

С выхода схемы совпадения 10 сформированная таким образом последовательность импульсов одновременно поступает на узел 12 индикации для преобразования длительности импульсов в цифровой код и отображения его на цифровом индикаторе, а также через интегратор 14, выделяющий огибающую с широтно-импульсной модуляцией и ключ 15 на устройство документирования 16.

Характеристика группового времени запаздывания, получаемая при документировании, представляет собой прерывистую кривую, точки разрыва которой определяют точку (частоту) на оси абсцисс, а положение отрезка лнНИИ- значение группового времени запаздывания по оси ординат.

Сигналы, поступающие на схему совпадения 10 и триггер 17 с запрещающих выходов блоков 1 и 2 играют вспомогательную роль и

обеспечивают прохождение сигнала на узел 12 индикации и устройство документирования 16 после того, как заканчивается фазирование сигналов на выходах делителей 19 в блоках 1 и 2.

Для возможности определения номера посылки измерительной частоты на выходе испытуемого объекта с помощью узла 13 выделяется стартовый сигнал в момент поступления на вход устройства посылки первой измерительной частоты, разрешающий работу распределителя блока индикации частоты. В качестве продвигающих импульсов для распределителя используются инвертированные синхронизирующие импульсы узла 5. обеспечивающие индикацию частоты во время приема посылок измерительных частот.

Предмет изобретения

50

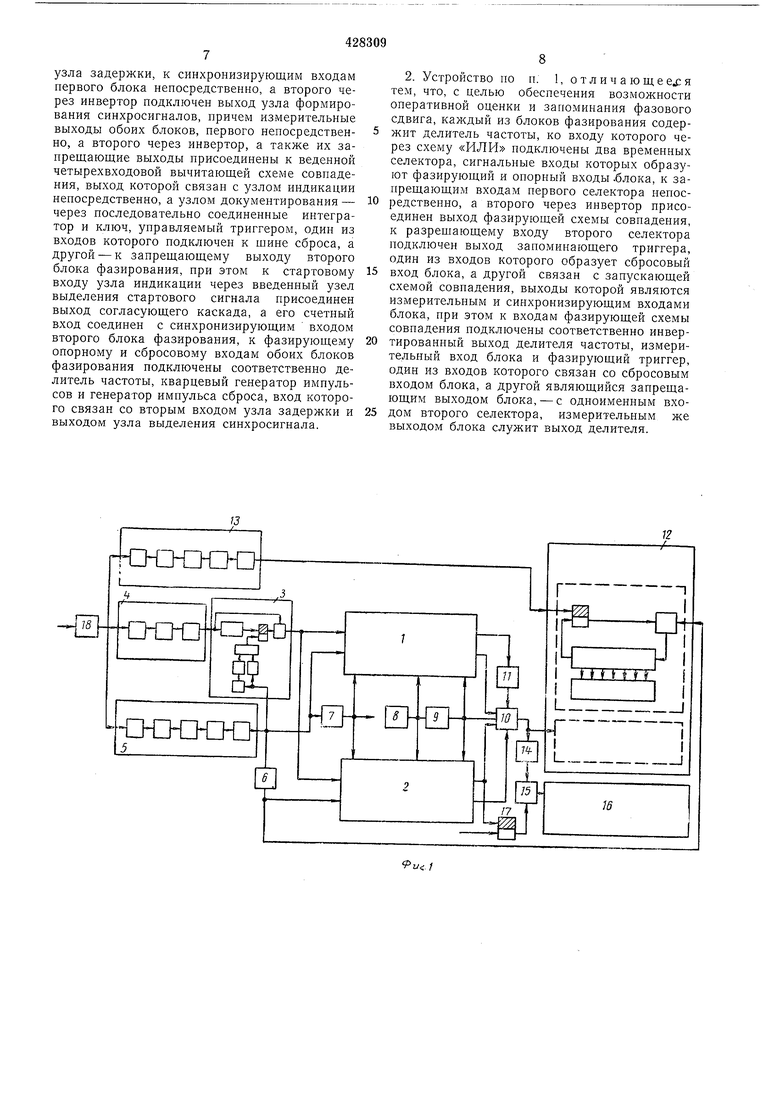

1. Приемное устройство для измерения характеристи си группового вреА1ени запаздывания, основанное на измерении разности фаз между огибающими сигналов, чередующимися во времени, содержащее цепь из последовательно соединенных согласующего каскада, узла выделения измерительного сигнала и узла задержки, узел формирования синхросигналов, кварцевый генератор импульсов с делителем частоты, генератор импульса сброса, триггер, интегратор, ключ и узел индикации с узлом документирования, отличающееся тем, что, с целью повышения точности измерения, введены два блока фазирования, к измерительным входам которых подключен выход узла задержки, к синхронизирующим входам первого блока непосредственно, а второго через инвертор подключен выход узла формирования синхросигналов, причем измерительные выходы обоих блоков, первого непосредственно, а второго через инвертор, а также их запрещающие выходы присоединены к веденной четырехвходовой вычитающей схеме совпадения, выход которой связан с узлом индикации непосредственно, а узлом документирования - через последовательно соединенные интегратор и ключ, управляемый триггером, один из входов которого подключен к шине сброса, а другой - к запрещающему выходу второго блока фазирования, при этом к стартовому входу узла индикации через введенный узел выделения стартового сигнала присоединен выход согласующего каскада, а его счетный вход соединен с синхронизирующим входом второго блока фазирования, к фазирующему опорному и сбросовому входам обоих блоков фазирования подключены соответственно делитель частоты, кварцевый генератор импульсов и генератор импульса сброса, вход которого связан со вторым входом узла задержки и выходом узла выделения синхросигнала. 2. Устройство по п. 1, о т л ич а ю щее я тем, что, с целью обеспечения возможности оперативной оценки и запоминания фазового сдвига, каждый из блоков фазирования содержит делитель частоты, ко входу которого через схему «ИЛИ подключены два временных селектора, сигнальные входы которых образуют фазирующий и опорный входы .блока, к запрещающим входам первого селектора пепосредственно, а второго через инвертор присоединен выход фазирующей схемы совпадения, к разрешающему входу второго селектора подключен выход запоминающего триггера, один из входов которого образует сбросовый вход блока, а другой связан с запускающей схемой совпадения, выходы которой являются измерительным и синхронизирующим входами блока, при этом к входам фазирующей схемы совпадения подключены соответственно инвертированный выход делителя частоты, измерительный вход блока и фазирующий триггер, один из входов которого связан со сбросовым входом блока, а другой являющийся запрещающим выходом блока, - с одноименным входом второго селектора, измерительным же выходом блока служит выход делителя.

| название | год | авторы | номер документа |

|---|---|---|---|

| Приемное устройство для измерения характеристик группового времени запаздывания в каналах связи | 1975 |

|

SU597992A1 |

| УСТРОЙСТВО для ФАЗИРОВАНИЯ ПО РАБОЧИЛ\ ПОСЫЛКАМ | 1969 |

|

SU254558A1 |

| Устройство для цикловой синхронизации | 1981 |

|

SU1107317A1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ДОСТОВ^ЕЦ.ОСТИ ПЕРЕДАЧИ ДВОИЧНОЙ ИНФОРМАЦИИ | 1970 |

|

SU274152A1 |

| Стартстопное передающее устройство | 1976 |

|

SU566387A1 |

| Устройство поэлементной синхронизации | 1985 |

|

SU1319301A1 |

| Устройство поэлементного фазирования приемников дискретных сигналов | 1972 |

|

SU450377A2 |

| УСТРОЙСТВО ШИРОКОПОЛОСНОЙ РАДИОСВЯЗИ ШУМОПОДОБНЫМИ СИГНАЛАМИ | 1982 |

|

SU1840540A1 |

| Устройство для измерения абсолютного времени распространения сигналов | 1972 |

|

SU446018A1 |

| УСТРОЙСТВО ДЛЯ ОЦЕНКИ КАЧЕСТВА СВОБОДНОГО КАНАЛА ПЕРЕДАЧИ ДИСКРЕТНОЙ ИНФОРМАЦИИ | 1968 |

|

SU217437A1 |

rfCKHDO ЧЗ--ООС D

гз

L- гг

г / / / r / / / / л / /л / / r /

VT чу v 17 y 7 v7 ч:ку vy ХУ vy к vy V/ y M

Даты

1974-05-15—Публикация

1972-05-29—Подача