(54) ЦИФРОВОЙ ВРЕМЕННОЙ ДИСКРИМИНАТОР

| название | год | авторы | номер документа |

|---|---|---|---|

| Задающее устройство следящего электропривода | 1982 |

|

SU1056129A1 |

| УСТРОЙСТВО АВТОМАТИЧЕСКОГО УПРАВЛЕНИЯ НАГРУЖЕНИЕМ ПРИ ПРОГРАММНЫХ ИСПЫТАНИЯХ МЕХАНИЧЕСКИХ КОНСТРУКЦИЙ НА УСТАЛОСТНУЮ ПРОЧНОСТЬ | 2007 |

|

RU2365965C2 |

| Датчик электростатического поля | 1981 |

|

SU1022077A1 |

| ТЕЛЕВИЗИОННОЕ СЛЕДЯЩЕЕ УСТРОЙСТВО | 1988 |

|

SU1574152A1 |

| Устройство для регистрации значений контролируемых параметров | 1982 |

|

SU1065689A2 |

| Устройство для измерения синусоидального напряжения | 1982 |

|

SU1104428A1 |

| Устройство для регистрации значений контролируемых параметров | 1981 |

|

SU958857A1 |

| УСТРОЙСТВО АВТОМАТИЧЕСКОГО УПРАВЛЕНИЯ НАГРУЖЕНИЕМ ПРИ ПРОГРАММНЫХ ИСПЫТАНИЯХ МЕХАНИЧЕСКИХ КОНСТРУКЦИЙ НА УСТАЛОСТНУЮ ПРОЧНОСТЬ | 2007 |

|

RU2365963C2 |

| ПРИЕМНИК СПУТНИКОВЫХ РАДИОНАВИГАЦИОННЫХ СИСТЕМ | 1997 |

|

RU2118054C1 |

| МОНОИМПУЛЬСНАЯ РАДИОЛОКАЦИОННАЯ СИСТЕМА | 2000 |

|

RU2178896C1 |

Изобретение относится к автоматике, в частности, к следящим измерителям задержки. Изобретение может быть использовано в измерительных комплексах, автодапьномерах, цифровых автоматических приборах. Известны временные дискриминаторы, выполненные на аналоговых элементах, состоящие из двух ключевых схем, открываемых передним и задним стробами слежения Соответственно, двух зарядных емкостей интегратора, запоминающего сигнал ошибки, и схемы обнуления i, Для этих устройств характерно влияние параметров входящих элементов на точность работы дискриминатора, а также малая надежность, влияние внешних условий необходимость регулировок. Известен также дискриминатор, содержащий формирователь видеосигна-ла, формирователь следящего строба, два ключа, открываемых передним и задним полустробами соответственно, два RC-фильтра, входы которых соединены с выходами ключей, а выходы соединены с прямым и инвертирующим входами УПТ, выход которого соединен с первым входом двухпозиционного переключателя, второй вход подключен к источнику рпсфного напряжения, а выход соединен с генератором управляющего напряжения, выход которого соединен с ре- sepciffiHbiM счетчиком, выходы которого соединены с регистром ощибки, причем управление двухпозщионным переключателем и реверсивным счетчиком осуществляется меандром . Недостатком этого устройства является наличие многих аналоговых элементов: ключи, ЕС-филыры, УПТ, переключатель, генератор, управляемый напряжением. Это приводит к I нестабильности характеристик дискриминатора и требует специальных регулировок для компенсации смещения. Целью изобретения является повышенве стабильности и упрощения процесса регулирования устройства. Для этого в дискриминатор, содержащий формирователь входного сигнала, формирователь следящего строба и реверсивный счетчик импульсов, введены дешифратор, ;цифро вналоговый преобразователь импульсов элемент задержки и два блока, каждый из которых содержит первый элемент задержкй отводы которого соединены со входами коммутатора управляющие входы которого соединены с выходами дешиф;раго ра, а выход с первым входом вентиля и через второй элемент задержки и нвертор со вторым входом вентйля, третий кжод которого подключен к выходу компаратора, первый ЕКОД которого соединен с выходом цифро-аналогового преобразователяв а второй вход - с вькодом формирователя входного сигнала, причем входы дешифраторов ,и цифро-аналоговых преобразователей импульсов соединены с выходами сдвигового регистра, управляющий нход которого через элемент задержки подключен к выходу формирователя следящего строба и входу первого элемента задержки первого блока, выход которого соединен со входом первого элемента задержки второго блока, а выходы вентилей первого и второго блока соединены с суммирующим и вычитающим входами реверсивного счетчика импульсов.

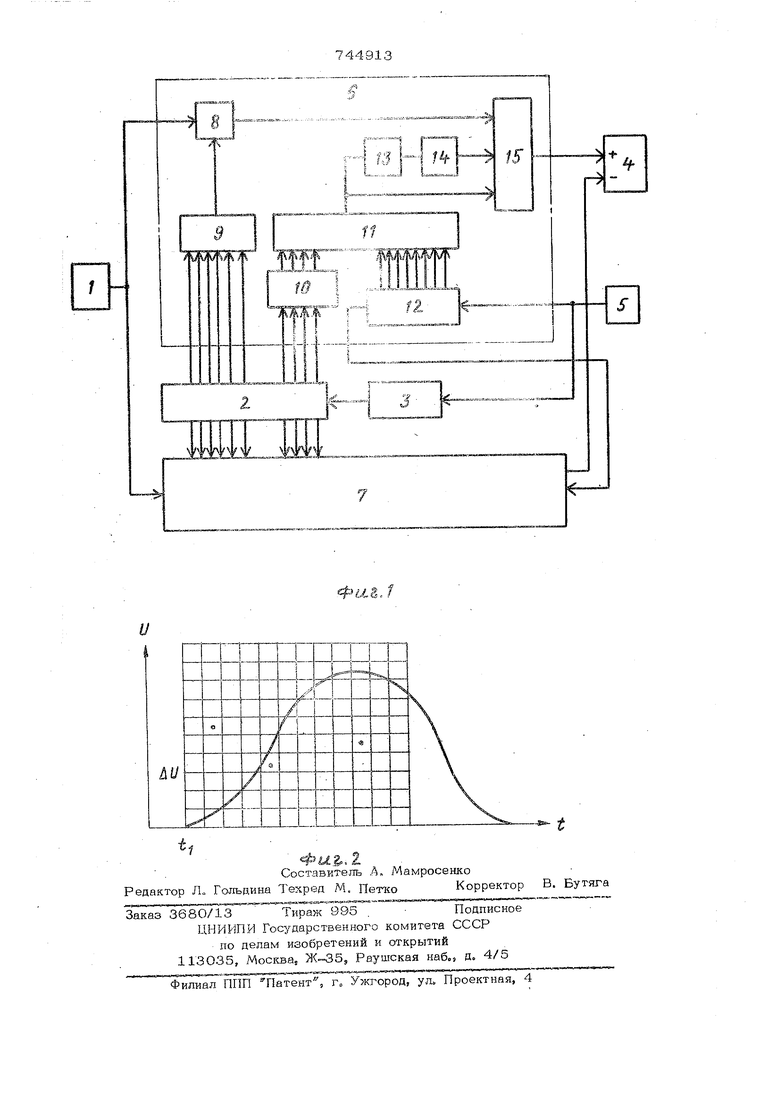

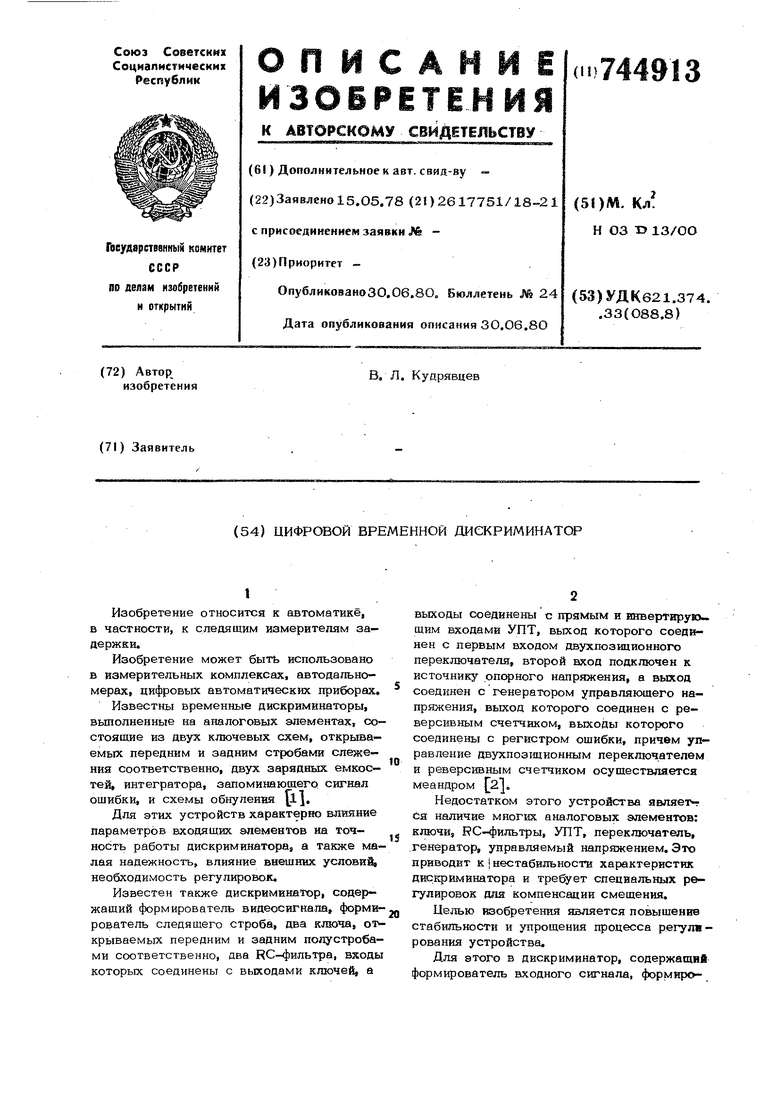

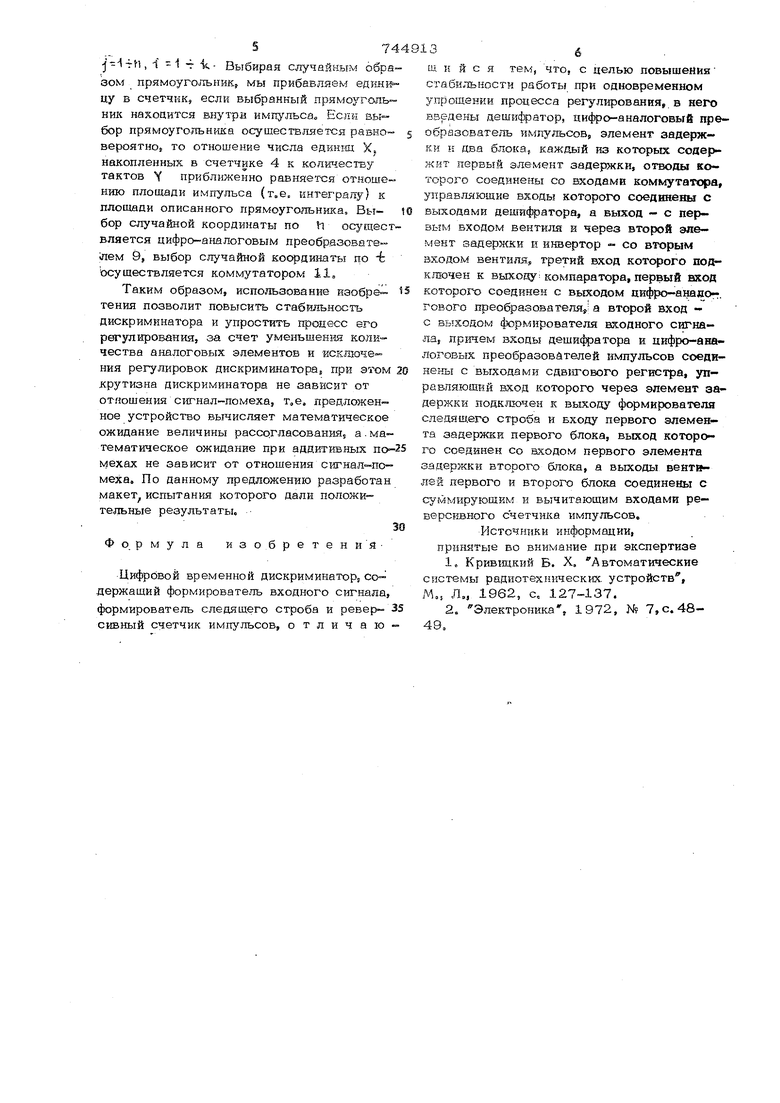

На фиг 1 изображена структурная :электрическая схема устройства| на фиг. 2диаграмма, поясняющая его ра&эту,

Цифровой временнг и дискриминатор содержит формирователь 1 входного сигнала, регистр 2 сдвиговый, элемент 3 задержки, счетчик 4 импульсов реверсивный, формирователь 5 следящего строба.; блоки 6, 7, каждый из которых содержит компаратор 8 (например, а}илоговый)9 преобразователь 9 импульсов цифро--аналогоБыЙ8 дешифратор 1О, коммутатор 11, элементы 12, 13 задержки, инвертор 14, вентиль

Формирователь 1 входного сигнала соединен с входом компаратора 8 каждого из блоков 6 и 7 другой вход которого подключен через преобразователь 9 к выходам сдвигового регистра 2, а выход - к первому входу вентиля 15, второй вход которого соединен с его третьим входом и выходом коммутатора 11 через инвертор 14 и второй элемент задержки 13, а вы- ходы вентилей 15 каждого блока 6 и 7 подключены к суммирующему и вычитающему входам счетчика 4, Выход формирователя следящего строба 5 соединен с входами элемента задержки 3 и первого элемента задержкй12 блокаб, первый выход которого соединен с входом первого элемента задержки 12 блока 7, отводы первого элемента

задержки 12 подключены к входам коммутатора llj, управляющие входы которого через дешифратор 10 соединены с выходами сдвигового регистра 2 вход которого соединен с выходом апемента задержки 3.

Устройство работает следующим образом.

Строб слежения с выхода формирователя 5 через элемент задержки 3 производит сдвиг регистра с обратной связью 2, на выходах которого формируются псевдослучайные сигналы. Эти сигналы в цифроаналоговых преобразовател$1х 9 преобразуются в псевдослучайное напряжение, которое сравнивается в компараторе 8 с входным, сигналом с выхода формирователя входного сигна ла 1. Компаратор 8 формирует на выходе логическую единицу в моменты превыщения мгновенного значения входного сигнала уровня псевдослучайного напряжения. Другие псевдослучайные сигналы подаются на дешифратор 10, который йодключает коммутатор 11 к какому-либо отводу элемента задержки 12, При прохождении сигнала через элемент задержки 13, инвертор 14 и вентиль iS формируется сигнал опроса состояния компаратора 8, Если входной сигнал в момент опроса превышал уровень псевдослучайного напряжения, то в реверсивный счетчик 4 .прибавляется (для первого блока), или вычитается (для второго блока) единица. Число, на1сапливаемое в реверсивном счетчике 4, представляет ошибку рассогласования. Сигнал ощибки выражается разностью интегралов от напряжения входного сигнала

fc.- -r-c-i-vZT

Iu(tMi:-f L4t-)d-t ;

tn

t,-r

где и(4:)- напряжение входного сигнала; t, - временное положение переднего фронта строба слежения; - величина задержки элемента

задержки 12.

Вычисление интегралов производится методом Монте арло. Суть его заключается в следующем Двумерная область, в которой требуется вычислить интеграл, разбивается сеткой, нанесенной по U и , на прямоугольники, с координатами U - tiНапример, суть видеосигнал имеет вид колокола с шириной импульса Т и амплитудой и . Опшлем вокруг импульса прямоугольник и разобьем его стороны на И частей по и и 1 частей по Полученные разбиением -V прямоугольников будут иметь координаты - ; л -,гае

j-i-rh, i -1 -f -k- Выбирая случайным образом прямоугольник, мы прибавляем в C4eT4 -iKj если выбранный прямоугольник находится БЩтри импульса Если аьгбор прямоугольника осушествляется равновероятноа го отношение члспа едит-щ X. накопленных в счетчике 4 к количеству тактов У приближенно равняется отношению площади импульса (т,е, интеграяу) к площади описанного прямоугольника. Вы- бор случайной координаты по i осуществляется цифро-аналоговым преобразовате-лем 9, выбор случайной коо{эдинаты по 4; осуществляется коммутатором 11,

Таким образом, использование ваобретения позволит повысить стабильность дискриминатора и упростить процесс его регулирования, за счет уменъшетш количества а1шлоговых элементов и исключения регулировок дискриминаторвв при этом крутизна дискриминатора не зависит от отяощения сигнал-помеха, т,е, предложенное устройство вычисляет математическое ожидание величины рассргласован га, а . математическое ожидание при аддитивных по- мехах не зависит от отношения сигнал-помеха. По данному предложению разработан макет испытания которого дали положительные результаты. Формула изобретенияЦифровой временной дискриминаторг содержащий формирователь входного сигнала, формирователь следящего строба и ревер- сивный счетчик импульсов, отличаю

щ и и с я тем, что, с целью повышения сгабильности работы при одновременном упрошении процесса регулирования, в него взедены дешифратор, цифро-аналоговый преобразователь HiVfjiyabcoB, элемент задержки -: два блокВ} каждый из которых соде{ жит первый элемент задержки, отводы которого соединены со входами коммутатора, управляющие входы которого соединены с выходами дешифратора, а выход - с перBbJM входом вентиля и через второй элемент задержки Е инвертор - со вторым входом вентиля, третий вход которого подключен к выходу: компаратора, первый вход которого соединен с выходом цифро-анадо-:. гового преобразователя,; а второй вход с выходом формирователя входного сигнала, npirasM входы дещи4ратора и цифро-аналоговых преобразователей импульсов соединены с выходами caBin oBoro регистра, управляющий аход которого через элемент задержки подключен к выходу формирователя следящего строба и входу первого элемента задержки первого блока, выход которого соединен со входом первого элемента задержки второго блока, а выходы вентилей первого и второго блока соединены с сугС1мирующим и вычитающим входами реверсивного счетчика импульсов. Источники информации, прирштые Бо внимание при экспертизе

2, Электроника, 1972, № 7,с. 4849,

-i Л

/шл7У А

y..L

10 I

A

V

Авторы

Даты

1980-06-30—Публикация

1978-05-15—Подача