Изобретение относится к области преобразования и .кодирования информации.

Известны преобразователи активной мощности в код, построенные по принципу управляемого делителя, на вход которого подают входное напряжение, а соотношение ллеч устанавливают пропорционально входному току. Выходное .напряжение делителя преобразуют с помощью аналого-цифрового преобразователя.

Недостатками указанного преобразователя являются узкий динамический диапазон, зависимость частоты тактового генератора от частоты измеряемого процесса, большой объем оборудования.

Цель изобретения - расширение динамического диапазона, обеспечение независимости работы и точности преобразователя от частоты измеряемого процесса, упрош,ение конструкции и повышение .надежности преобразователя активной мопдности в код. Для этого предлагаемый преобразователь содержит парафазные усилители напряжения, источник опорного .напряжения, аналоговые ключи, множительное устройство с частотным выходом и реверсивный счетчик, лричем источники опорното напряжения и входных сигналов по.дключены к входам парафазных усилителей, выходы которых через аналоговые ключи, переключаемые триггерами управления, связаны с входами множительного устройства; выход последнего соединен с счетным входом реверсивного счетчика, шины реверса которого соединены посредством инвертора с выходом

одного из нуль-органов; выход второго нульоргала соединен посредством другого инвертора с счетными входами триггеров управления, а входы нуль-органов соединены с источниками входных ситналов.

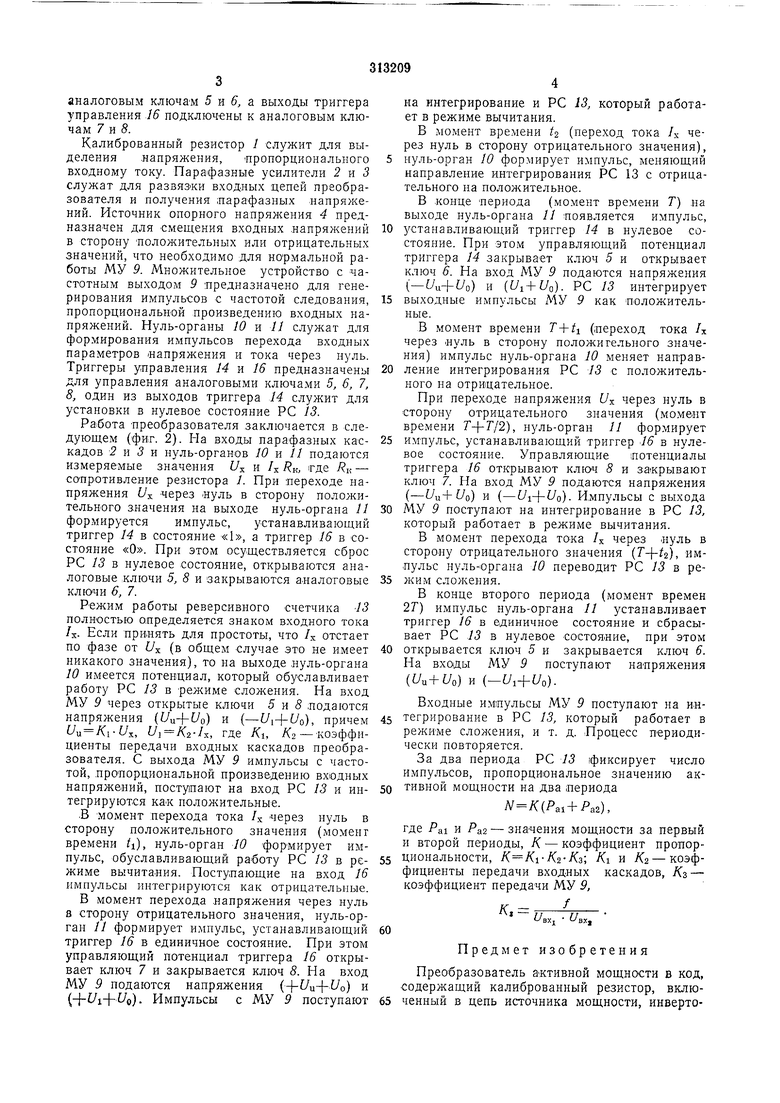

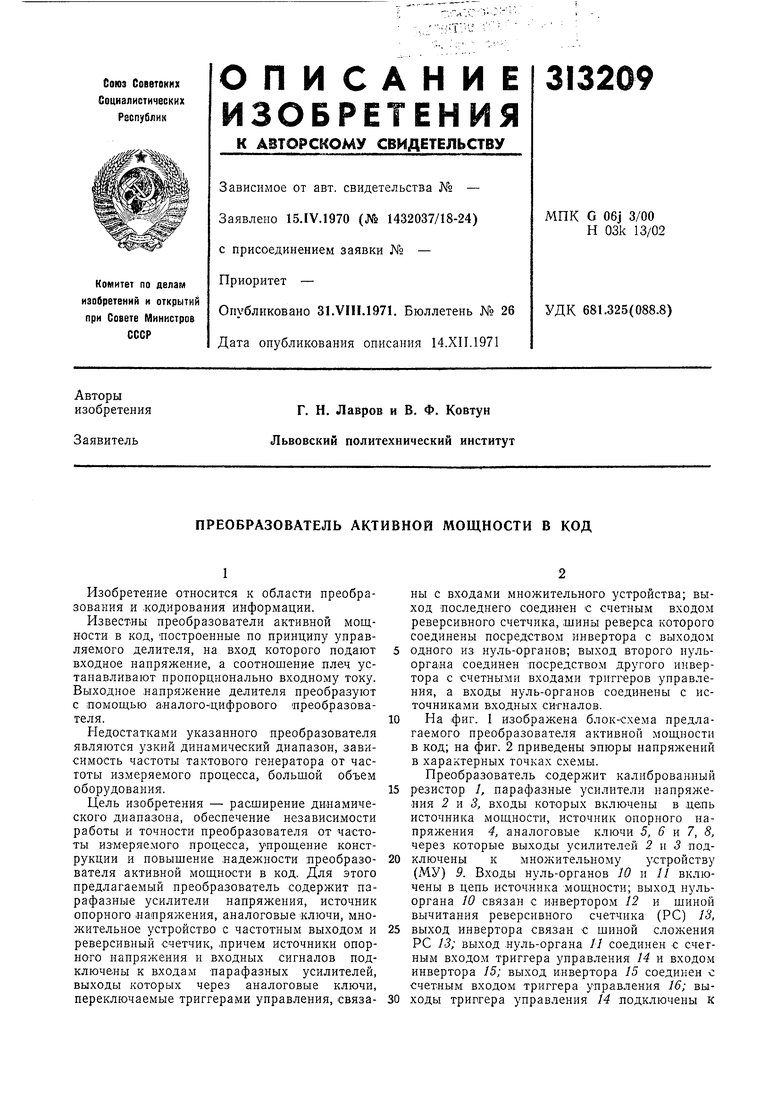

На фиг. 1 изображена блок-схема предлагаемого преобразователя активной мощности в код; на фиг. 2 приведены эпюры напряжений в характерных точках схемы. Преобразователь содержит калиброванный

резистор 1, парафазные усилители напряже.ния 2 и 3, входы которых включены в цень источника мощности, источник опорного напряжения 4, аналоговые ключи 5, 6 и 7, 8, через которые выходы усилителей 2 и 3 подключены к множительному устройству (МУ) 9. Входы нуль-органов 10 и // включены в цепь источника мощности; выход нульоргана 10 связан с и.нвертором 12 и шиной вычитания реверсивного счетчика (PC) 13,

выход инвертора связан с шиной сложения PC 13; выход .нуль-органа 11 соединен .с счетным входом триггера управления 14 и входом инвертора 15; выход инвертора 15 соединен с счетным входом триггера управления 16; выаналоговым ключам 5 Е 6, а выходы триггера управления 16 подключены к аналоговым ключам 7 и S.

Калиброванный резистор 1 служит для выделения .напряжения, пропорционального входному току. Парафазные усилители 2 и 3 служат для развязки входных цепей преобразователя и получения ларафазных напряжений. Источник опорного напряжения 4 предназначен для смещения входных ,напрял ений в сторону полол ительных или отрицательных значений, что необходимо для нормальной работы МУ 9. Множительное устройство с частотным выходом 9 предназначено для генерирования импульсов с частотой следования, пропорциональной произведению входных напряжений. Нуль-органы 10 и // служат для формирования импульсов перехода входных параметров напряжения и тока через нуль. Триггеры управления М и 16 предназначены для управления аналоговыми ключами 5, 6, 7, 8, один из выходов триггера 14 служит для установки в нулевое состояние PC 13.

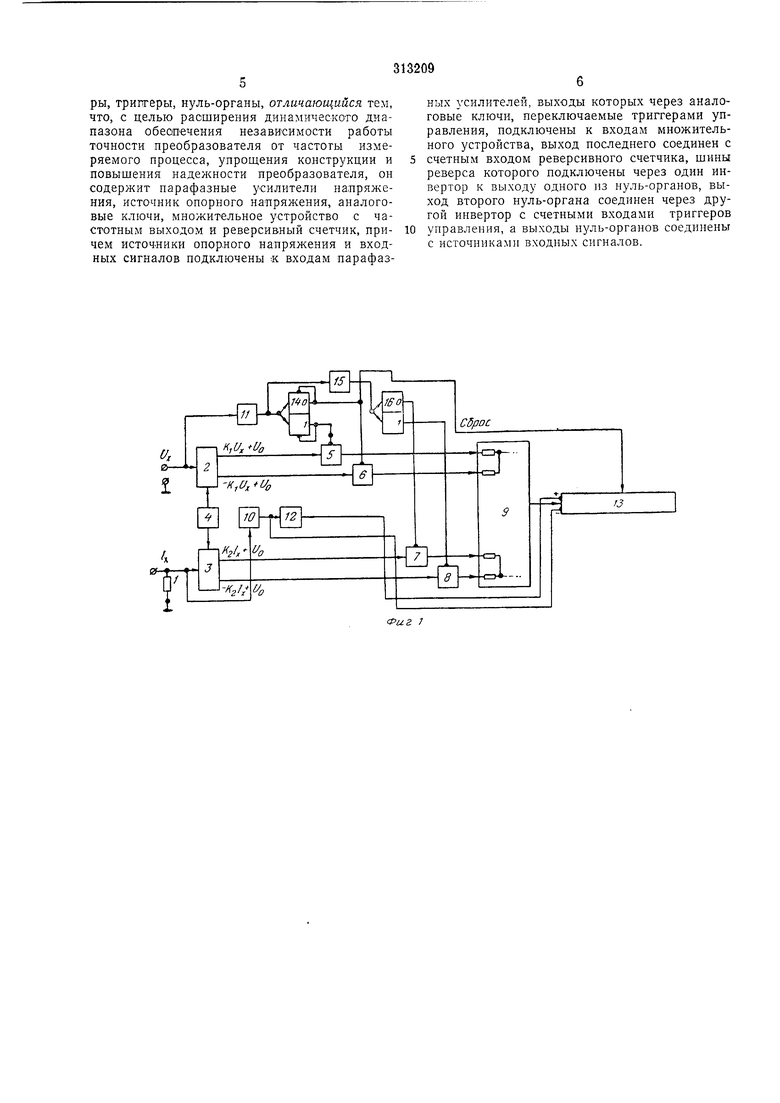

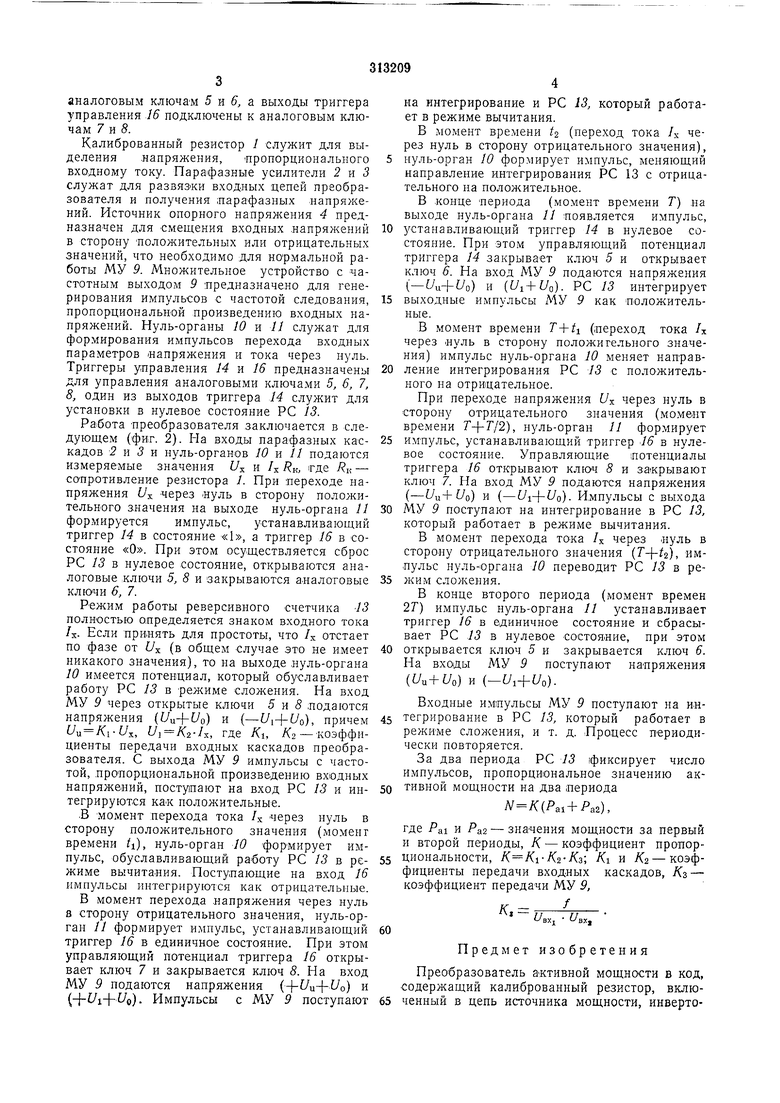

Ра:бота -преобразователя заключается в следующем (фиг. 2). На входы парафазных каскадов 2 и 5 и нуль-органов 10 и // подаются измеряемые значения t/x и /х , где Яи - сопротивление резистора /. При переходе напряжения t/x через Нуль в сторону положительного злачения на выходе нуль-органа 11 формируется импульс, устанавливающий триггер 14 в состояние «1, а триггер 16 в состояние «О. При этом осуществляется сброс PC 13 в нулевое состояние, открываются аналоговые :Ключи 5, 8 Е закрываются аналоговые ключи 6, 7.

Р-ежим работы реверсивного счетчика -13 полностью определяется знаком входного тока /X. Если принять для простоты, что /X отстает по фазе от U (в общем случае это не имеет никакого значения), то на выходе .нуль-органа 10 имеется потенциал, который обуславливает работу PC 13 в режиме сложения. На вход МУ 9 через открытые ключи 5 и 5 .подаются напряжения (бц+С/о) и (-Ui-i-Uo), причем Lu /Ci-f x, /C2-/x, где /Сь К2-Коэффициенты передачи входных каскадов преобразователя. С выхода МУ 9 импульсы с частотой, .пропорциональной произведению входных напряжений, поступают на вход PC 13 и интегрируются как положительные.

.В момент перехода тока /х через нуль в сторону положительного значения (момент времени ti), нуль-орган 10 формирует импульс, обуславливающий работу PC 13 в режиме вычитания. Поступающие на вход 16 импульсы интегрируются как отрицательные.

В момент перехода .напряжения через нуль в сторону отрицательного значения, нуль-орган // формирует импульс, устанавливающий триггер 16 в единичное состояние. При этом управляющий потенциал триггера 16 открывает ключ 7 и закрывается ключ S. На вход МУ 9 подаются напряжения (-j-f/u+ o) и (-J-t/1-f-f/o)- Импульсы с МУ 9 поступают

на интегрирование и PC 13, который работает в режиме вычитания.

В момент времени tz (переход тока /х через нуль в сторону отрицательного значения),

нуль-орган 10 формирует импульс, меняющий направление интегрирования PC 13 с отрицательного на положительное.

В .конце периода (момент времени Г) .на выходе нуль-органа 11 появляется импульс,

устанавливающий триггер 14 в нулевое состояние. При это.м управляющий потенциал триггера 14 закрывает ключ 5 и открывает ключ 6. На вход МУ 9 подаются напряжения (-L/u+ o) и (Ui+Uo). PC 13 интегрирует

выходные импульсы МУ 9 как положительные.

В момент времени T + ti (переход тока /х через нуль в сторону положительного значения) импульс нуль-органа 10 меняет направление интегрирования PC 13 с положительного на отрицательное.

При переходе напряжения U через нуль в сторону отрицательного значения (момент времени Г-}-Г/2), нуль-орган // формирует

импульс, устанавливающий триггер 75 в нулевое состояние. Управляющие потенциалы триггера 16 открывают ключ 8 и закрывают ключ 7. На вход МУ 9 подаются напряжения (-Uu+l o) и (). Импульсы с выхода

МУ 9 поступают на интегрирование в PC 13, который работает в режиме вычитания.

В момент перехода то-ка /х через «уль в сторону отрицательного значения (), импульс нуль-органа 10 переводит PC 13 в режим сложения.

В конце второго периода (момент времен 2Т) импульс нуль-органа 11 устанавливает триггер 16 в единичное состояние и сбрасывает PC 13 в нулевое состояние, при этом

открывается ключ 5 и закрывается ключ 6. На входы МУ 9 поступают напряжения (Un+Uo) и (-t/1+f/o).

Входные импульсы МУ 9 поступают на интегрирование в PC 13, который работает в режиме сложения, и т. д. Процесс периодически повторяется.

За два периода PC 13 фиксирует число импульсов, пропорциональное значению активной мощности на два периода

(P,+ P,2),

где Pal и Раз - значения мощности за первый и второй периоды, К - коэффициент пропорциональности, K Ki-К -Кз-, Ki и Kz - коэффициенты передачи входных каскадов, /Сз - коэффициент передачи МУ 9,

к - f

вх, f/B.,

ры, триггеры, нуль-органы, отличающийся тем, что, с целью расширения динамическото диапазона обеспечения независимости работы точности преобразователя от частоты измеряемого процесса, упрощения конструкции и повышения надежности преобразователя, он содержит парафазные усилители напряжения, источник опорного на пряжения, аналоговые ключи, множительное устройство с частотным выходом и реверсивный счетчик, причем источники опорного напряжения и входных сигналов подключены -к входам царафазных усилителей, выходы которых через анало говые ключи, переключаемые триггерами управления, подключены к входам множительного устройства, выход последнего соединен с счетным входом реверсивного счетчика, шины реверса которого подключены через один инвертор к выходу одного пз нуль-органов, выход второго нуль-органа соединен через другой инвертор с счетными входами триггеров управления, а выходы нуль-органов соединены с источниками входных сигналов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Дискретно-аналоговый интегратор | 1986 |

|

SU1372337A1 |

| Устройство для считывания гра-фичЕСКОй иНфОРМАции | 1978 |

|

SU805368A1 |

| Цифровой измеритель температуры | 1986 |

|

SU1364910A1 |

| Цифровой измеритель составляющих комплексных сопротивлений | 1987 |

|

SU1456907A1 |

| Интегратор | 1988 |

|

SU1728871A1 |

| Множительно-делительное устройство | 1977 |

|

SU696444A1 |

| Дискретно-аналоговый интегратор | 1976 |

|

SU611218A1 |

| Цифровой измеритель температуры | 1988 |

|

SU1583757A1 |

| Устройство для считывания графической информации | 1980 |

|

SU883937A1 |

| Множительно-делительное устройство | 1979 |

|

SU1023344A1 |

Даты

1971-01-01—Публикация