Изобретение относится к области авто.матш и и вычислительной техники.

Известны элементы с програм.мируемон структурой, содержащие схе.мы «PI выбора направлений передачи возбуждения, регистр сдвига, устройство хранения информации и логический эле.мент.

При фиксированном числе утравляюндих (адресных) каналов у однородного устройства (клеточного авто.мата), построенного на базе известного элемента, однородное устройство (на.прИ1Мбр, запоминающее), обладает недостаточ.ны.м быстродействием. Это обусловлено те.м, что выборка эле-ментов в тако.м устройстве осуществляется последовательно с помощью схемы с неременной структурой настройки.

Цель изобретения - повышение быстродействия однородного устройства с фнксироisaHHbiM числом адресных каналов, количество KOTOipbix ,не зависит от емкости (числа элементов) устройства и определяется числом управляющих входов у одного элемента с программируе.мой структурой.

Это достигается тем, что нредлагаемый элемент содержнт схему совпадения и группу схем «Логическая равнозначность, первые и вторые входы которых подключены соответственно к части ВХОДОВ и выходов устройства хранепия ипформацин, выходы схем «Логичеекая равнозначносгь подключены ко входам схемы сонпадення, нодсоединенпой своим выходом ко входу трнггера активности, выход которого Подключен к унравляющему входу логнческого элемента, унравляющий вход схемы совнадепия подключен к источнику управляющих сигналов.

В результате 1еньшается время выборки элементов однородного устройства, имеющего столько управляющих каналов, С1:олько i у одного элемента. Это дает возможность эффективно использовать однородное устройство в качестве быстродействующего запоминаюHiero, в котором выборка элементов (ячеек намятн) осун1,ествляется за один такт с помощью небольшого числа адресных каналов. Количество этнх каналов не зависит от емкости запоминающего устройства и определяется чнслом разрядов устройства хранения ннформанпп одного элемента.

В предлагаемом элементе возбуждение триггера актнвности может осун,ествляться как сигналамн с выходов элементов, так и сигналами, вырабатываемыми самим элементом. Для чего предлагаемый элемент содержит сравнения, выходным сигналом которой осуществляется возбужденне трнггера активности.

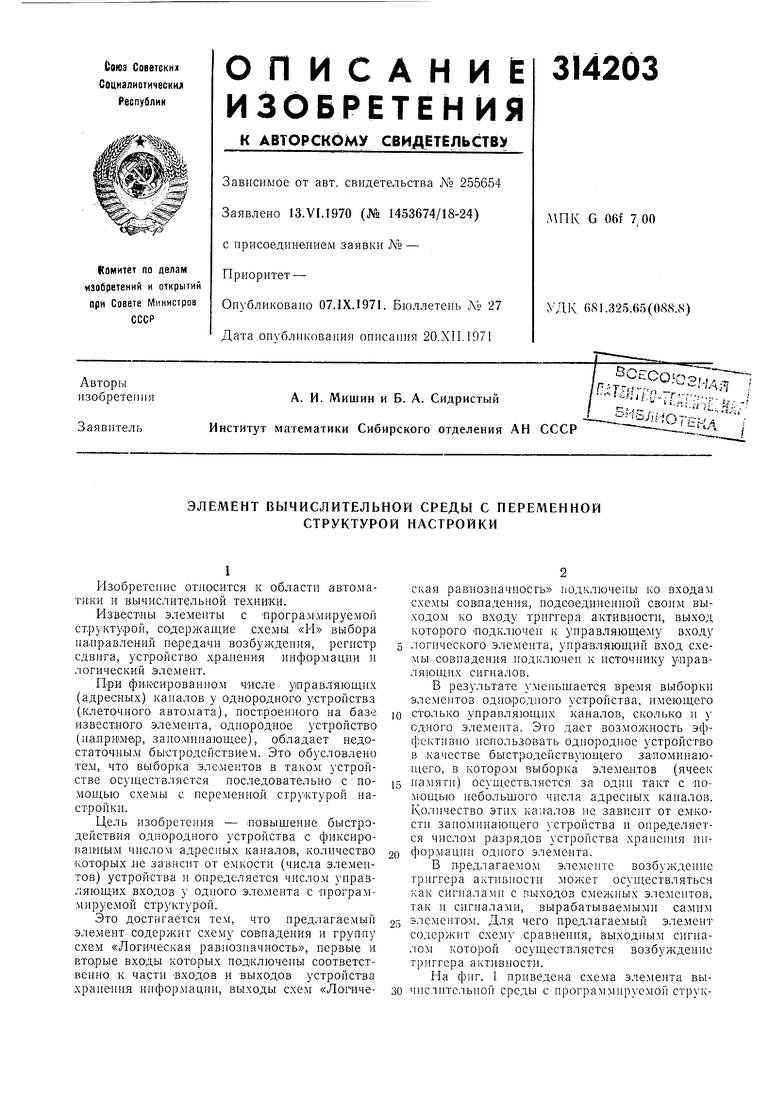

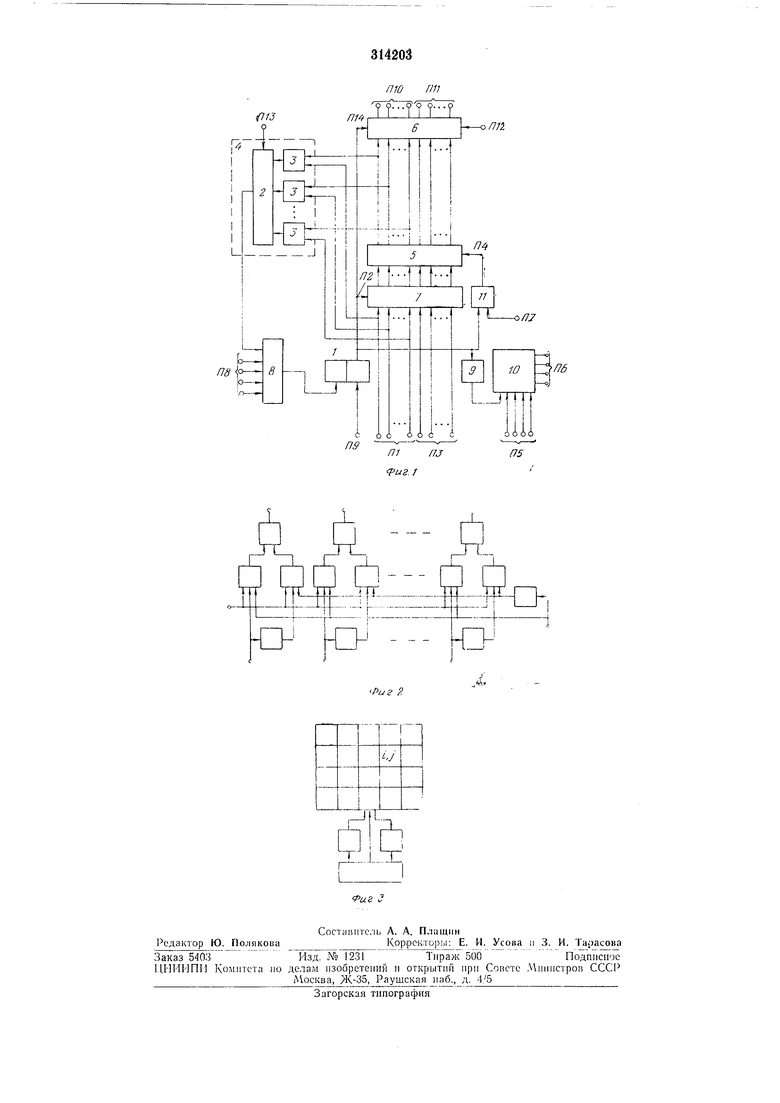

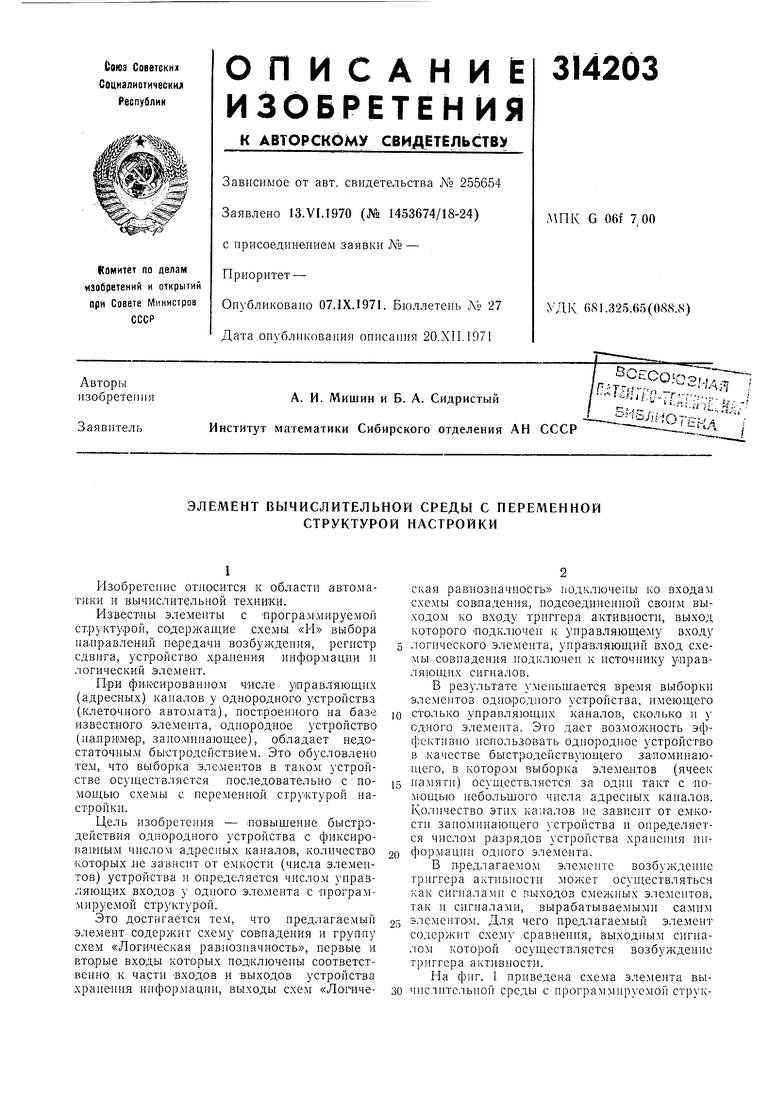

турой; на фиг. 2 - функциональная схема логического эл-емента; на фиг. 3 - блок-схема машины, выполненной па базе однородного устройства с программируемой ст1рукту.рой.

В состав предлагаемого элемента (-ом. фиг. 1) входят триггер / активности; схема 2 совпадения (схема «И), реализующая логическую операцию «Конъюнкция ; схемы 3, реализующие онерацию «Логическая равнозначкость (т. е. логическую функцию f(x, у)

x-yvx-y); схема 4 сравнения, которая вырабатывает сигнал «единица, тогда как код, поступающий на полюсы П, совпадает с коДО|М, храняп-,имся в за1номинающих ячейках (триггерах) устройства 5 хранения (своими выходами ячейки подключены ко вторым входам схем .3); логический элемент 6, схема 7 записи, содержащая группу схем «И на два входа каждая (первые входы этих схем объединены и подключены к полюсу П2, вторые входы подключены к полюсам П1, ПЗ, а выходы - к единичным входам триггеров устройства 5, нулевые входы триггеров объединены и подключены к нолюсу П4); схема 8 объединения (схема «ИЛИ), реализующая логическую операцию «Дизъюнкция ; линия задержки 9, которая совместно с триггером глстивности образует разряд регистра сдвига; схе.ма 10 выбора направления передачи возбуждения (содержит четыре схемы «И на два входа (Каждая, первые -входы схем «И объе динены и нодключепы к выходу линии задержки, вторые входы подключены к полюcaiM П5, а выходы - к полюсам П6); схема «И 11 ycTaiHOBKH в пуль триггеров устройства хранения информации (установка в «О триггеров осуществляется по входу Я7 при условии, что на второй вход схемы 11 с выхода триггера активности ноступает сигнал «1).

Входные Возбуждающие полюсы П8 предназначены для приема сигналов с выходных возбуждающих полюсов соседних элементов, полюс П9 - хТ,ля подачИ управляющих сдвигающих импульсов в регистр сдвига. Полюсы /7/, ПЗ - входные полюсы устройства хранения информации; полюсы П1 служат также 1{ля подачи сигналов в схему сравнения (показана на фиг. 1 пунктирной линией). Полюсы П5 предназначены для приема сигналов о выборе направления передачи возбуждения в соседние элементы, выходные возбуждающие полюсы П6 - для передачи возбуждения на входные возбуждающие полюсы соседних элементов. Полюсы П10, ПИ - выходные логические полюсы элемента, предназначены для считывания информации с триггеров устройства хранения информации. Эти полюсы в однородном устройстве, выполняющем функцию быстродействующего запоминающего, подключаются к общпм шинам считывания. При помощи полюса П12 производится задание режима работы логического элемента; при поступлении на этот нолюс сигнала «Ь логический элемент пропускает сигналы с выходов триггеров устройства хранения информации на нолюсы П10, П11 без инверсии (когда триггер активности находится в состоянии «1); нри поступлении на полюс П9 сигнала «О логический элемент пропускает сигналы

с выходов триггеров устройства хранения информации на полюсы П10, П11 с инверсией (когда триггер активности находится в состоянии «1). Полюс П4 - вход установки в «О триггеров устройства храпения информации;

полюс П7 предназначен для установки в «О триггеров устройства хранения информации |при условни, что триггер активности находится в состоянии «1. Полюс П13 - управляющий вход схемы совпадения, предназначен

для задания режима работы элемента; при подаче на этот полюс снгнала «1 на выходе схемы совпадения установится сигнал «1 (нрн условии, что код, поступающий на полюсы Я/, совпадает с кодом, хранящимся в

трех триггерах устройства храпения информации, которые подключены ко входам схем 2); при подаче на полюс П13 сигнала «О на выходе схемы совпадения будет сигнал «О. Полюс П14 - управляющий вход

логического эле|Мепта; еслн на этот вход с выхода триггера aiRTHBHocTH ностунает сигнал «I, то разрешается нередача (считывание) сигналов с триггеров устройства храпения информации на логические выходы П10, П11

(сигналы передаются с инверсией или без инверсии в зависимости от значения сигнала на полюсе П12). Полюс П12 - вход управления приемом инфорМации в триггеры устройства 5; если на этот вход с выхода трнггера активности поступает сигнал «1, то сигналы с входных полюсов П1, ПЗ проходят через схему 7 па входы устройства 5 и устанавливают триггеры в нужное состояние.

Полюсы П5 быть объединены, например, с полюсами ПЗ.

В режиме «Настройка осуществляется ввод ИСХОДНЫХ данных в запомннающие ячейки элементов однородного устройства. Для зада.ния этого режн:ма нужно на полюс Я/о

подать сигнал «О, после чего 1астройка элементов осун1ествляется известным способом.

Для задания режима «Вычисление нуж|Но на полюс Я/5 подать сигнал «1, что разрешает прохождение сигналов с выходов схем 3

через схему совпадения 2 па вход триггера активности (см. фiir. 1). В это-м режиме на управляющие входы Я/, ПЗ подается информация, подлежандая обработке, а с полюсо; ПЮ, ПИ снимается результат обработки.

Рассмотрим работу элемента на следуюHICM примере.

Допустим, все триггеры активности всех элементов решетки находятся в состоянии «О, и требуется установить в «1 (возбудить)

триггер активности элемента с коордииатамн i, j (см. фиг. 3). Для этого нужно на полюсы Я/ подать тайкой код, который был записан в этот элемент в режиме «Пастройка. Зто приведет к тому, что на выходе схемы

сигнал «1, который н установит его триггер активности в состояние «I. После возбуждения триггера актив-ности может быть произведепа или выдача (считывание) информации, храиящейся в триггерах устройства хранения информация выбранного элемента, или - зались новой информации в запомииающие ячейки этого элемента. Считывание информации осунгествляться как с разрушением, так и без разрушения. Если требуется записать новую информацию в запоминающие ячейки выбранного эле меита, то это можно осуш,ествить путем подачи нового кода иа полюсы ЯУ, ПЗ (см. фиг. 1). Таким образом, выборка любого элемента (незавнсимо от его место1положения в решетке) может осуществляться за один такт. Это достигается тем, что каждому элементу или групле элементов (массиву) в процессе настройки решетки может быть присвоен свой адрес, который, если требуется, может быть изменеп в .процессе вычисления или в процессе повторной настройки.

Если в процессе настройки (вычисления) одно и то же имя (адрес) присвоить груп-пе элементов, то при подаче этого адреса иа полюсы П1 возбудятся триггеры активности одиоименных элементов, т. е. за один такт можно считать информацию с ячеек памяти нескольких элементов.

Передачу возбуждения ino принципу близкодействия, т. е. от элемента к элементу выгодно И:0нользовать, когда команды следуют одна за другой по порядку (iroMep команды соответствует порядковому номеру запоминаюц,1,ей ячейки рещетки, где хранится содержание данной ко1манды). Такими обычно являются команды, реализуюнию программу. В случае команд условного н безусловного переходов, которые вызывают изменение нормального 1порядка следОВания , выборку элементов -решетки выгодно производить путем Возбуждения триггера активности по нгинам П1 (см. фиг. 1).

Предлагаемый элемент с нрограммируемой структурой суп1.ественио новышает быстродействие однородного }стр.ойства (но быстродействию такое устройство не уступает устройствам с коордпнатной выборкой элементов) и увеличивает его логические возможности, так как можно за один такт реализовать логические функции многих переменных.

Предлагаемое однородное устройство осоQ бенно выгодно реализовать в интегральном иополненни, так как к числу выводов интегральны.х схем предъявляются весьма жесткие требоваиия.

В место устройства храпения информации - с параллельпым способом записи можно использовать устройство 1последовательиого типа - регистр сдвига, часть выходов которого нужно подключить к первым входам схем «Логическая равпозиачность, а вторые входы этих схем нужно подключить к выходам донолнительпого регистра сдвига, предназначенного для хранения адреса (имени) элемента. В этом случае число выводов сокращается до минимума, однако быстродействие устройства снижается в раз, где п - количество разрядов в регистре сдвига.

Предмет изобретения Элемент вычислительной среды с переменной структурой настройки ио авт. св.

0 N° 255654, отличающийся тем, что, с целью повышення быстродействия однородного устройства, оп содержит схему совладения и ррупи - схем «Логическая равнозначность, первые и вторые входы которых цодключены

1 соответственно к частн входов и выходов устройства храиеиия информации, а выходы-ко пходам схемы совпадения, иодсоединенной своШ выходом ко входу триггера активност 1, выход оторого :ПОдключен к управляютему входу лог:1чес1(ого элемента, управляющий вход схемы сов1;аде;1ия нодк.иочен к нсточ 1их v:iniii..)Hi,nx сигпа.юв.

пю пп

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ ОПРЕДЕЛЕНИЯ МЕСТА ОБРЫВА НА ВОЗДУШНОЙ ЛИНИИ ЭЛЕКТРОПЕРЕДАЧИ | 2013 |

|

RU2540443C1 |

| ЭЛЕМЕНТ ВЫЧИСЛИТЕЛЬНОЙ СРЕДЫ | 1972 |

|

SU355611A1 |

| Устройство анализа и замены числовых полей | 1985 |

|

SU1280606A1 |

| УСТРОЙСТВО ДЛЯ ЗАЩИТЫ ЧЕТЫРЕХ ПАРАЛЛЕЛЬНЫХ ЛИНИЙ | 2016 |

|

RU2636801C1 |

| ПОЕЗДНАЯ МОДУЛЬНАЯ ПЕРЕДАЮЩАЯ ФАЗИРОВАННАЯ АНТЕННАЯ РЕШЕТКА | 2017 |

|

RU2683592C1 |

| ЭЛЕМЕНТ ВЫЧИСЛИТЕЛЬНОЙ СРЕДЫ С ПЕРЕМЕННОЙ СТРУКТУРОЙ НАСТРОЙКИ | 1970 |

|

SU267183A1 |

| Устройство анализа и перестановки числовых полей | 1985 |

|

SU1317429A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1987 |

|

SU1444958A1 |

| Устройство контроля количества чугуна в миксере | 1979 |

|

SU908833A1 |

| Микропрограммный процессор | 1985 |

|

SU1275457A1 |

iSNEEEEl

i I

ттг

Даты

1971-01-01—Публикация