«

:&

;о ел

00

Изобретение относится к вычислительной технике, предназначено для преобразования разноформатных двоичных кодов в двоично-десятичные с не- посредственной вьщачей их параллель- но-последовательным кодом, и может быть использовано при построении устройства отображения информации (УОИ) сложной информационной системы типа метеорадиолокатора (МРЛ).

Цель изобретения - повьшение быстродействия при одновременном сокращении объема памяти.

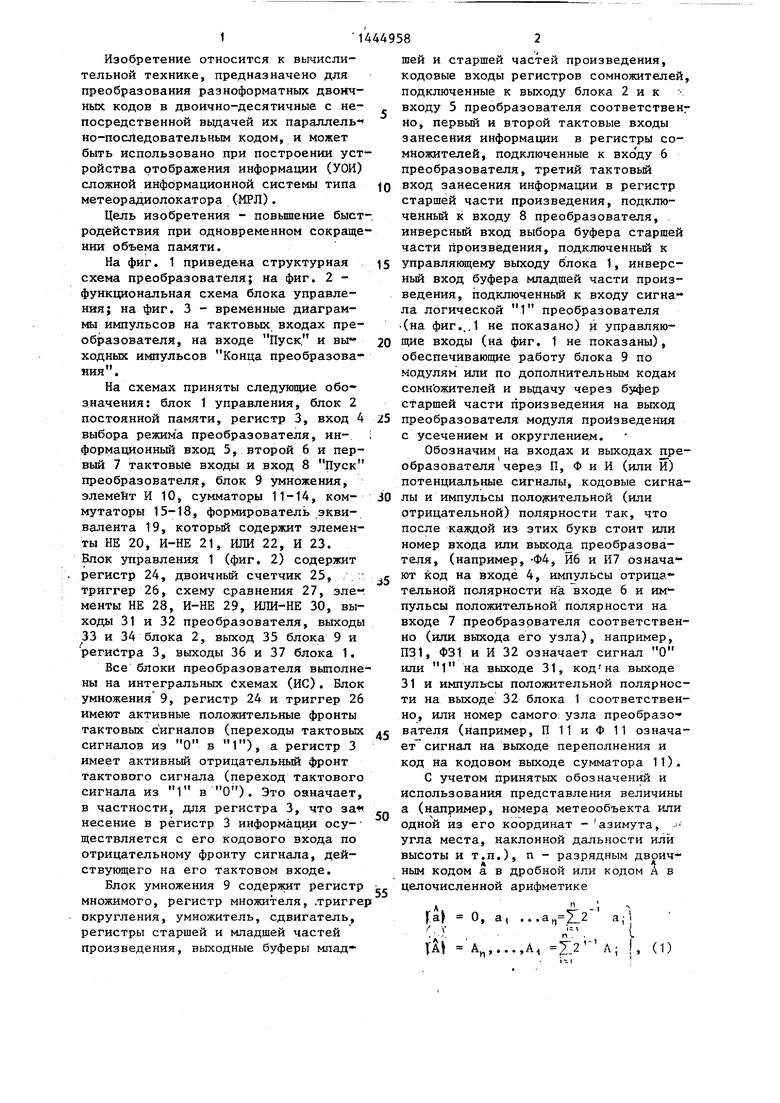

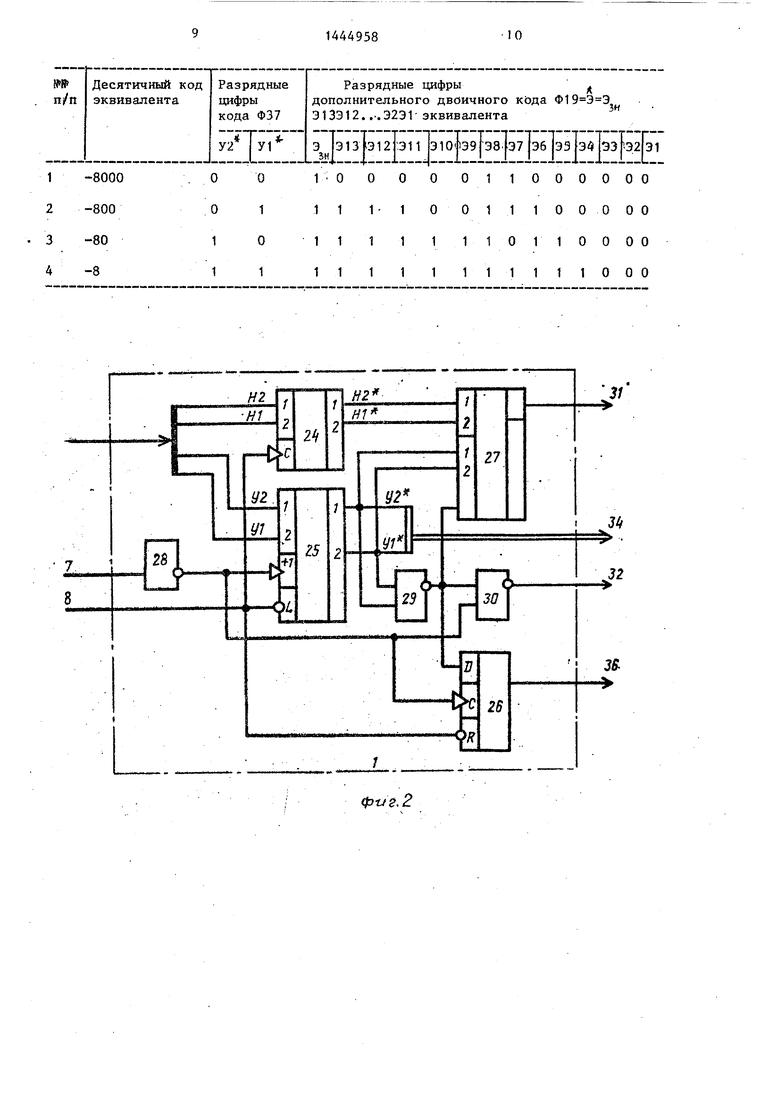

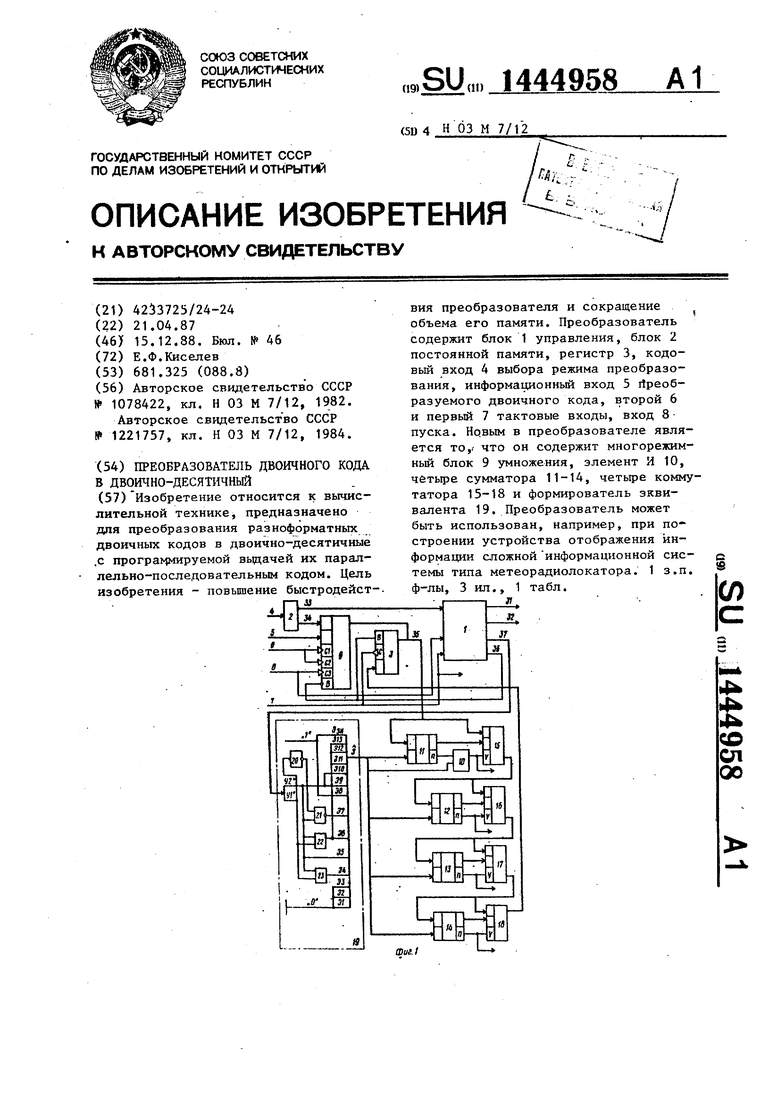

На фиг. 1 приведена структурная схема преобразователя; на фиг. 2 - функциональная схема блока управления; на фиг. 3 - временные диаграммы импульсов на тактовых входах преобразователя, на входе Пуск. и вы ходных импульсов Конца преобразования.

На схемах приняты следующие обозначения: блок 1 управления, блок 2 постоянной памяти, регистр 3, вход 4 выбора режим а преобразователя, ин-. формационный вход 5, второй 6 и первый 7 тактовые входы и вход 8 Пуск преобразователя, блок 9 умножения, элемейт И 10, сумматоры 11-14, ком- мутаторы 15-18, формирователь эквивалента 19, который содержит элементы НЕ 20, И-НЕ 21, ИЛИ 22, И 23. Блок управления 1 (фиг. 2) содержит регистр 24, двоичный счетчик 25, :: триггер 26, схему сравнения 27, элег менты НЕ 28, И-НЕ 29, ИЛИ-НЕ 30, выходы 31 и 32 преобразователя, выходы 33 и 34 блока 2, выход 35 блока 9 и регистра 3, выходы 36 и 37 блока 1.

Все блоки преобразователя вьшолне ны на интегральных Схемах (ИС). Блок умножения 9, регистр 24 и триггер 26 имеют активные положительные фронты тактовых сигналов (переходы тактовых сигналов иэ О в 1), а регистр 3 имеет активный отрицательный фронт тактового сигнала (переход тактового сигнала из 1 в О). Это означает, в частности, для регистра 3, что за несение в регистр 3 информации осу- ществляется с его кодового входа по отрицательному фронту сигнала, действующего на его тактовом входе.

Блок умножения 9 содержит регистр

множимого, регистр множителя, .триггер округления, умножитель, сдвигатель, регистры старшей и младшей частей произведения, выходные буферы

5 0

5 0 е

с

0

5

шей и старшей частей произведения, кодовые входы регистров сомножителей, подключенные к выходу блока 2 и к :: входу 5 преобразователя соответствен но, первый и второй тактовые входы занесения информации в регистры сомножителей, подключенные к вхо ду 6 преобразователя, третий тактовьй вход занесения информации в регистр старшей части произведения, подклю- ченньй к входу 8 преобразователя, инверсный вход выбора буфера старшей части произведения, подключенньй к управляннцему выходу блока 1, инверс- ньй вход буфера младшей части произведения, подключенньй к входу сигнала логической 1 преобразователя (на фиг..,1 не показано) и управляющие входы (на фиг. 1 не показаны), обеспечивающие работу блока 9 по модулям или по дополнительным кодам сомн ожителей и вьщачу через буфер старшей части произведения на выход преобразователя модуля произведения с усечением и округлением.

Обозначим на входах и выходах преобразователя через П, Ф и И (или И) потенциальные сигналы, кодовые сигналы и импульсы положительной (или отрицательной) полярности так, что после каждой из этих букв стоит или номер входа или выхода преобразователя, (например, Ф4, И6 и И7 означа ют код на входе 4, импульсы отрицательной полярности на входе 6 и импульсы положительной полярности на входе 7 преобразователя соответственно (или выхода его узла), например, П31, Ф31 и И 32 означает сигнал О или 1 на выходе 31, код на выходе 31 и импульсы положительной полярности на выходе 32 блока 1 соответственно, или номер самого; узла преобразователя (например, П 11 и Ф 11 означает сигнал на выходе переполнения и код на кодовом выходе сумматора 11).

С учетом принятых обозначений и использования представления величины а (например, номера метеообъекта или одной из его координат - азимута, угла места, наклонной дальности или высоты и т.п.), П - разрядным двоичным кодом а в дробной или кодом А в целочисленной арифметике

О, а, ...а,.2

п .

а,-

Ш А.,,...,А, 1.2- Л; 1, (1)

Ц 2

fal

где а акс

«1

значение

максимальное величины а.

Работу предлагаемого преобразователя можно описать следующим образом

Преобразователь выполнен для М 1,4, где П - разрядность входного кода, М - число тетрад выходного кода.

На устройство поступают сигналы кода Ф4 выбора режима преобразования и преобразуемого двоичного кода Ф5, тактовые импульсы И 6 и И 7 и импульсы запуска И 8, по которьм оно работ тает циклически так, что в казкдом цикле осуществляет подготовку к следующему циклу и вырабатывает последовательно М тетрад двоично-десятичного кода.

Каждый цикл преобразования выпол няется за М тактов, первый из которых начинается по И 8, а заканчивается по следующему за И 8 первому И 7, после окончания которого, при , начинается второй такт и т.п., а по М-ному импульсу и 7, следующему за И 8,формируется импульс И 32 конца цикл преобразования. Это поясняется фиг. для четырех циклов преобразования пр М 1, М 2, М 3, М 4.

В конце каждого j-ro такта ( на информационных выходах преобразовтеля устанавливаются .сигналы кода Tj 1110П12П13П14 j-той тетрады двоично-десятичного кода и сигнал II31 признака запятой.

Информация о количестве М тетрад и положения запятой в двоично-десяя тичном коде содержится в формируемом блоком 2 коде

Ф 33 Н2Н1У2У1 так, что : М 4 - 4 -2. У2 - 1 У1, (2) а Код Н Н2Н1 программирует положение запятой следующим образом, НЭ - пример, для М 4

00, запятая после первой тетрады

01, запята:я после второй тетрады. ,

10,запятая после третей тетрады

11,запятая остутствует (3) В каждом такте каждого цикла преобразования в установившемся режиме на выходе 35 формируется код

А

Н

Ф 35 П 36

П36ФЗ

по содержимым репистра 24 (.коду Ф Н ) и счетчика 25 (коду

(коду Ф24 Ф37) и сигналу У1 схемы

) и счетчика 25 (коду Ф25 У1 с сравнения 27 вырабатывает сигнал

1 при и . Ф

О при П или (5) по коду Ф 32 формирователь 19 вырабатывает дополнительный двоичный код 4, эквивалента в соответствии с таблицей истинности на входах второг го слагаемого каждого q-ro сумматора (где , , , и для сумматоров 11, 12, 13, и 14 соответствен но) устанавливаются сигналы значащих цифр дополнительного двоичного кода , образованного из кода Э так, чТо

5

0

А 3q

-8000 -8бо-2 -80-2

при

10

при при при (6) вырабатывает сигнал П10

(7)

злемент

П11 Э,з,

на выходах переполнений сумматоров

11 - 14 вырабатьшаются сигналы П11,

П12, П13 и П14 соответственно, со

гласно выражениям

5

0

5

П11

0

П12

П13

f

при при

при при

при

при

л Э.

з;

t:

к

I:

Ф35гО

Ф16гО

ЮО при 34 -ь Ф17.€0 П14 р при + Ф17ЭГО (8) а на выходах коммутаторов 15 - 18 вырабатываются коды Ф15, Ф16, Ф17, и Ф18 соответственно и согласно выражениям

П10 Ф35 П12 Ф15 П13 Ф16

Ф15 Ф16 Ф17 Ф18

V V V V

5

П10 Ф11 П12 Ф12 П13 Ф13

П14 Ф17 V П14 Ф14 (9J где - код, содержащийся в регистт ре старшей части произведения блока умножения 9; ФЗ - код, содержащийся в памяти регистра 3;

51444958

Число - обозначает дополнительный двоичный код отрицательного десятичного числа, например, - 8000 обозначает Э 10000011000000 числа -8000 первая строка таблицы.

Формирование кода Ф35 согласно (4) осуществляется за счет того, что при (или ) выходы блока 9 разрешены (или находятся в третьем состоянии), а выходы регистра 3 находятся 6 третьем состоянии (или разрешены) .

По окончанию каждого И7 счетчика 25 увеличивается на 1, в память регистра 3 заносится код Ф18 (9), а триггер 26 устанавливается в

f:

6

24

заносится код

в регистр

, определяющий положение

10

30

нала П28 в момент действия И7. В последнем такте каждого цикла , по И7 формируется импульс П 29, по окончании И7 счетчик 25 уста навливается в состояние 00, а триггер 26 - в состояние и вырабатывает управляющий сигнал .

Перед началом каждого цикла преобразования на входах преобразователя установлены коды Ф4 и Ф5, блок 2 по Ф4 вырабатывает коды ФЗЗ и Ф34, а в памяти преобразователя содержатся результаты предыдущего цикла преобразования: содержимое регистра 3 и 24, и регистра старшей части произведе.ния умножителя 9 соответствует информа ции, занесенной в эти регистры по И8 предыдущего цикла, счетчик 25 находит ся в состоянии 00, триггер 26 находится в состоянии О, в регистрах сомножителей умножителя 9 содержатся 40 коды Ф34 -Ф34, и (эти коды поданы также на кодовые входы блока 9) , а йа входе регистра старшей части произведения умножителя 9 новлен двоичный код

ния

Ф24

запятой в двоично-десятичном коде

согласно (3), а в регистр старшей

части произведения блока 9 заносится

код , т.е. код (10).

После этого начинается переходный процесс формирования сигналов на выходах узлов преобразователя согласно законам их функционирования (-4), (5), (6), (7), (8) и (9).

После окончания переходного процесса в первом такте производится, содержимое 15 считывание первой (старшей) тетрады двоично-десятичного кода по первому И7 цикла (фиг. 3), по окончанию которого содержимое счетчика 26 увеличивается ца 1, в память регистра 3 20 заносится код Ф18 (четвертая формула выражений (9)), являющийся остатком от кода Ф9 , а триггер 26 переключа- %тся в 1 (или О), если сформиро ванная тетрада не последняя (или 25 последняя). Остаток (т.е. код Ф18, занесенный в память регистра 3) cor держит информацию об оставшихся тетрадах формируемого двоично-десятичного кода.

Второй такт протекает при Ф35 ФЗ аналогично первому и заканчивается по второму И7, по окончанию которого в память регистра 3 заносится код Ф18 остатка от кода ФЗ, соответствующего моменту действия И7 и т.д.

В последнем такте каждого цикла вь5 абатывается сигнал и по последнему И7 цикла формируется импульс И32 конца цикла, после окончания которого счетчик 26 и триггер 27 переходит в нулевые состоАния.

35

45

Формула изобретения

1. Преобразователь двоичного кода в двоично-десятичный, содержащий регистр, блок постоянной памяти, блок управления, тактовый вход которого соединен с первым тактовым входом и тактовым выходом преобразователя, вход пуска которого подключен к входу пуска блока управления, отличающийся тем, что, с целью повьщ1е- ния быстродействия при одновременном сокращении объема памяти, он содержит

Ф9 Фщ (1Ф34, Ф5,), кр0(10)

где оператор операции усечения 2п-разрядного двоичного кода, заключенного в круг- - Лые скобки.

Каждый цикл преобразования начина ется по И8, непосредственно по кото- рому подтверждается нулевое состояние триггера .26 и производится занесение в счетчик 25 начального кода У Ф37, несущего информацию о количестве тетрад двоично-десятичного кода, согласно (2), а после оконча

6

24

заносится код

регистр

, определяющий положение

Формула изобретения

1. Преобразователь двоичного кода в двоично-десятичный, содержащий регистр, блок постоянной памяти, блок управления, тактовый вход которого соединен с первым тактовым входом и тактовым выходом преобразователя, вход пуска которого подключен к входу пуска блока управления, отличающийся тем, что, с целью повьщ1е- ния быстродействия при одновременном сокращении объема памяти, он содержит

блок умножения, формирователь экви

валента, с первого по чвтвертьй

комбинаци онные сумматоры, элемент И, с первого по четвертый коммутаторы.

причем вход команд блока управления соединен с первьм выходом блока постоянной памяти, ВТО1ЭОЙ выход и адресный вход которого соедине.ны

соответственно с входом первого операнда блока умножения и входом выбора режима пр еобразователя, информационный вход которого подключен к входу второго операнда блока умножения, первый и второй тактовые входы которого соединены с вторым тактовым входом преобразователя, вход пуска которого соединен с третьим тактовым входом блока умножения, инверсный вход выбора которого подключен к управляющему выходу блока управления и входу выбора регистра, тактовый вход которого подключен к первому тактовому входу преобразователя, а выход объединен с выходом блока умножения и соединен с первыми информационными входами первого сумматора и первого коммутатора, вьпсод которого подключен к первым информационным входам второго сумматора и второго коммутатора, выход которого соединен с первыми информационными входами третьего сумматора и.третьего коммутатора, выход которого подключен к первым информационным входам четвертого сумматора и четвертог коммутатора, выход которого соединен с информационным входом регистра, выходы суммы всех сумматоров соединены с вторыми информационными входами соответствующих коммутаторов, а выходы переполнения, кроме первого сумматора, подключены к управляющим входам соответствующих коммутаторов и являйтся информационными выходами соответственно третьего, второго и первого разрядов тетрады выходного кода, выход переполнения первого сумматора подключен к первому входу

.элемента И, выход которого подключен к управляющему входу первого коммутатора и является информационным выходом четвертого (старшего) разряда тетрады выходного кода, второй вход .элемента И соединен с выходом старшего значащего разряда формирователя эквивалентов,- вторые информа ционные входы первого, второго и

5

0

5

0

5

0

5

0

третьего сумматоров соединены соответственно с выходами п младших разрядов (п-разрядность входного кода), с выходами разрядов с (п+1)-го (старшего) по второй и с выходами разрядов со знакового по третий формирователя эквивалента, выход знакового разряда и выходы разрядов с (п+1)-го по четвертый которого подключен соответственно к входам двух старших раз-, рядов и входам младшего разрядов второго информационного входа четвертого сумматора, вход формирователя эквивалента подключен к информационному выходу блока управления, импульсный и кодовьм выходы которого являются соответственно выходом Конец преобразования и выходом Признак запятой тетрады выходного кода .преобразователя.

2. Преобразователь по п. 1, о т- личающийся тем, что блок управления содержит регистр, двоичный счетчик, триггер, схему сравнения и элементы НЕ, И-НЕ и ШШ-НЕ, причем разрядные выходы регистра соединены с первой группой информационных входов схемы сравнения, вторая группа информационных входов которой coe-i динена с выходами двоичного счетчика и входами элемента И-НЕ, выход которого соединен с управляющим входом схемы сравнения, с первым входом элемента ИЛИ-НЕ и с информационным входом триггера, тактовый вход которого, второй вход элемекте1 ИЛИ-НЕ и счетный вход двоичного счетчика объединены и подключены к выходу элемента НЕ, вход которого является тактовым входом блока, вход пуска которого подключен к тактовому входу регистра, к входу начальной установки счетчика и входу установки в О триггера, выход элемента ИЛИ-НЕ и выход схемы сравнения подключены соответственно к импульсному и кодовому выходам блока, а выходы двоичного счетчика и триггера соединены соответственно, с информационным и управляюш 1м . вьпсодами блока, разрядные входы двоичного счетчика и регистра подключены к входу команд блока.

И6

Ш

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоичного кода в двоично-десятичный | 1984 |

|

SU1221757A1 |

| Преобразователь двоичных чисел в двоично-десятичные числа | 1980 |

|

SU941990A1 |

| ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНО-ДЕСЯТИЧНОЙ ДРОБИ В ДВОИЧНУЮ ДРОБЬ | 1979 |

|

SU826335A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1981 |

|

SU1013942A1 |

| Преобразователь двоично-десятичной дроби в двоичную дробь | 1978 |

|

SU752323A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1988 |

|

SU1554143A1 |

| Преобразователь двоичных кодов угла и дальности в двоично-десятичные коды | 1987 |

|

SU1432782A1 |

| Преобразователь двоично-десятичногоКОдА B дВОичНый КОд | 1979 |

|

SU809151A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1985 |

|

SU1285604A1 |

| Преобразователь двоично-десятичной дроби в двоичную дробь | 1979 |

|

SU860053A1 |

Изобретение относится к вычислительной технике, предназначено для преобразования разноформатных двоичных кодов в двоично-десятичные ,с програг мируемой вьщачей их параллельно-последовательным кодом. Цель изобретения - повышение быстродействия преобразователя и сокращение объема его памяти. Преобразователь содержит блок 1 управления, блок 2 постоянной памяти, регистр 3, кодовый вход 4 выбора режима преобразования, информационный вход 5 г1реоб- разуемого двоичного кода, второй 6 и первый 7 тактовые входы, вход 8 пуска. Новым в преобразователе является то, что он содержит многорежим- ньй блок 9 умножения, элемент И 10, четьфе сумматора 11-14, четьфе коммутатора 15-18 и формирователь эквивалента 19. Преобразователь может быть использован, например, при построении устройства отображения информации сложной информационной системы типа метеорадиолокатора. 1 з.п. ф-лы, 3 ил., 1 табл. (Л с

И7 Ш

/fsrМ 2. Н З/Г««

Фиг.З

| Преобразователь двоичного кода в двоично-десятичный | 1982 |

|

SU1078422A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1984 |

|

SU1221757A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1988-12-15—Публикация

1987-04-21—Подача