Предлагаемое устройство относится к системам синхронизации и предназначено для формирования импульсных последовательностей, синхронных с внешним сигналом и сохраняющих синхронность с сигналом при кратковременных его пропаданиях.

Известны устройства формирования синхронизирующих последовательностей, содержащие блок фазовой автоподстройки частоты (ФАПЧ), блок стартстопной синхронизации, состоящий из дешифратора с п формирователями служебных импульсов, делителя частоты, выполненного па триггерах, и блока переключений.

Известные устройства обладают тем недостатком, что при первоначальном вхождении в связь или после длительного нарушения связи в силу своей инерционности требуют определенного времени вхождения в синхронизм.

С целью уменьшения времени вхождения в синхронизм в предлагаемом устройстве один из входов блока переключений через блок фазовой автоподстройки частоты подключен ко входу устройства, а другой вход блока переключений подключен ко входу устройства непосредственно, при этом один из выходов блока фазовой автоподстройки частоты подключен через блок переключений к делителю частоты блока стартстопной синхронизации, а

другой выход блока фазовой автонодстройки частоты - непосредственно к делителю частоты блока стартстопной синхронизации, выходы которого своими п формирователями служебпых импульсов подключены ко входу устройства обработки информации.

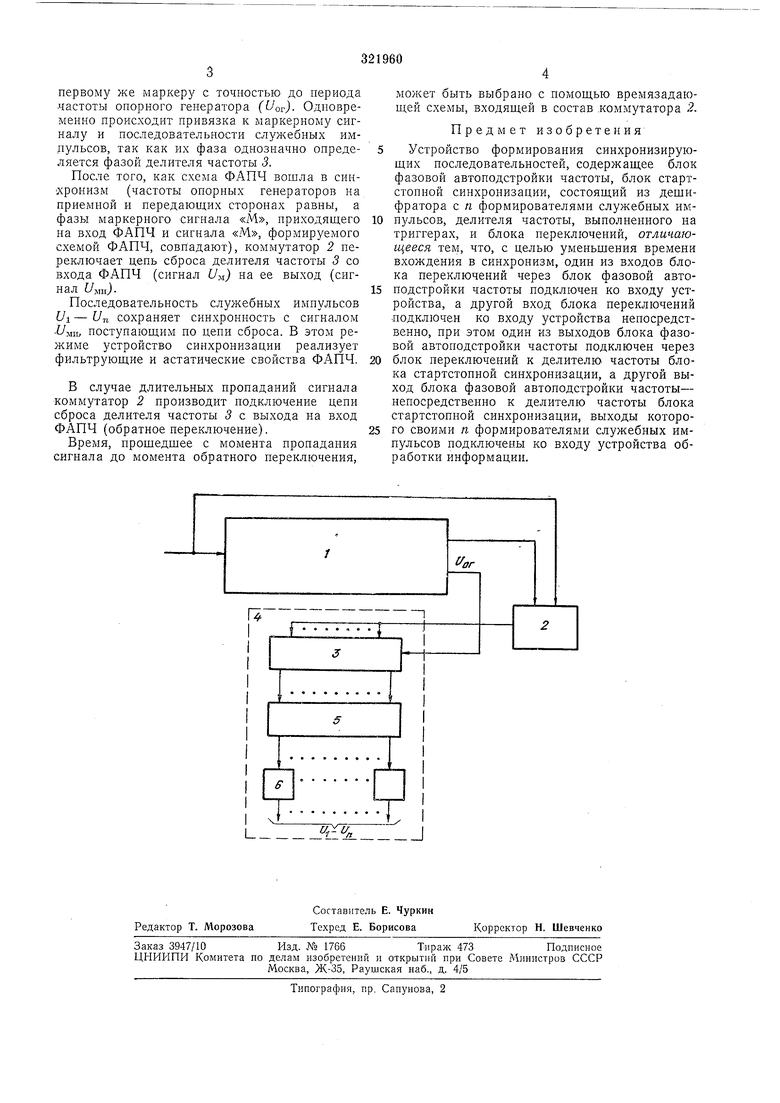

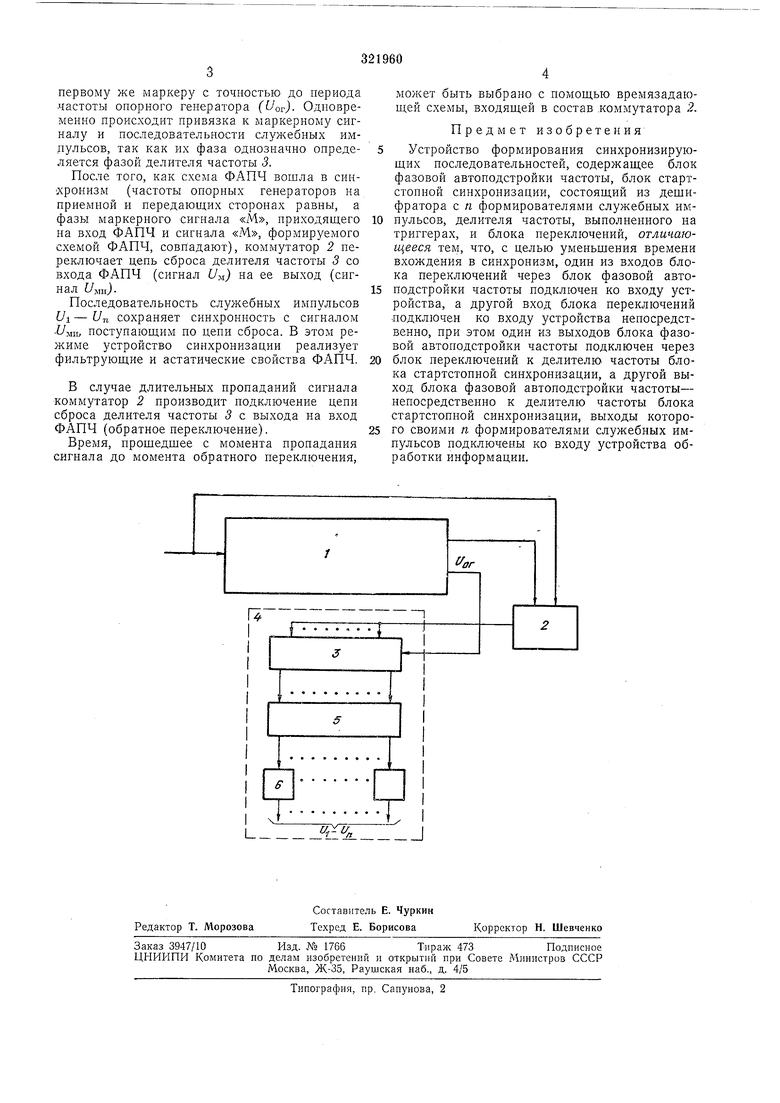

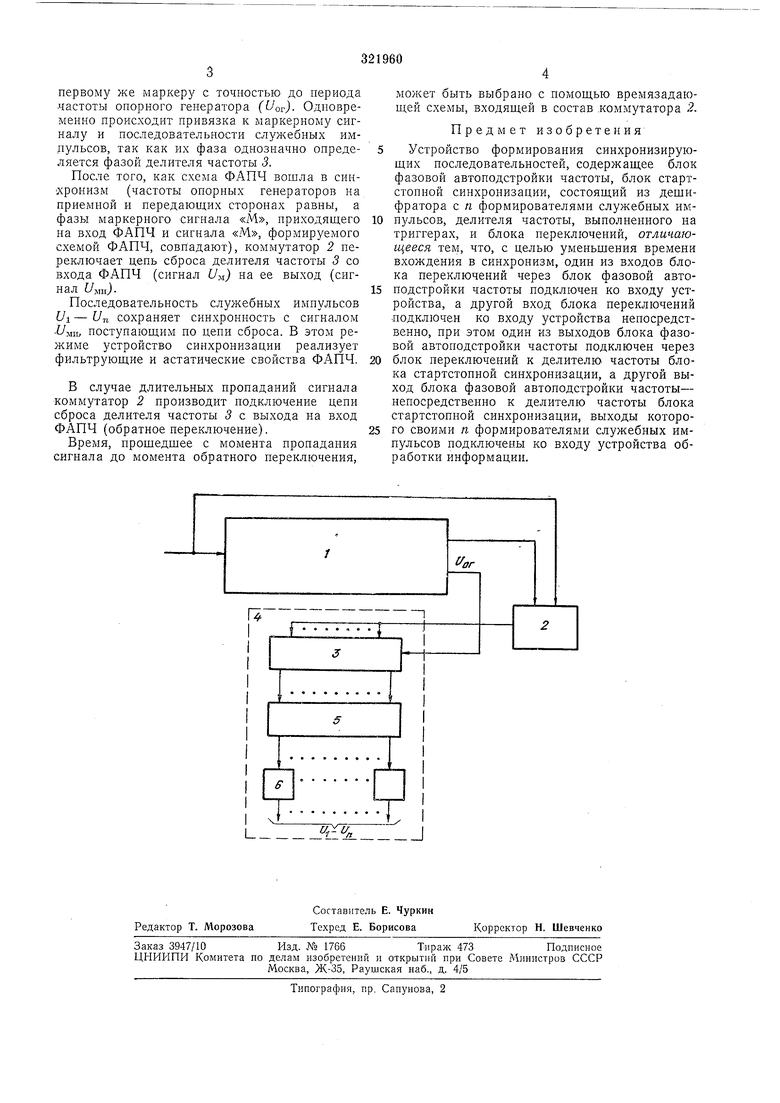

На чертеже показано предлагаемое устройство.

Устройство содержит схему 1 ФАПУ, выходы которой соединены с одним из входов коммутатора 2 и с делителем частоты 3 в блоке стартстопной синхронизации 4.

На второй вход коммутатора 2 сигнал поступает непосредственно со входа устройства.

Выход коммутатора 2 соединен со входом «сброс делителя частоты 3 в блоке стартстопной синхронизации, с вы.хода которого импульсы поступают на дешифратор 5 и затем на п формирователей служебных импульсов 6.

Принцип работы устройства состоит в следующем.

При отсутствии сигнала схема / ФАПЧ находится в асинхронном режиме, а цепь сброса

триггерпого делителя частоты 3 подключена ко входу схемы / ФАПЧ.

первому же маркеру с точностью до периода -частоты опорного генератора (. Одновременно происходит привязка к маркерному сигналу и последовательности служебных импульсов, так как их фаза однозначно определяется фазой делителя частоты 3.

После того, как схема ФАПЧ вошла в синХронизм (частоты опорных генераторов на приемной и передающих сторонах равны, а фазы маркерного сигнала «М, приходящего на вход ФАПЧ и сигнала «М, формируемого схемой ФАПЧ, совпадают), коммутатор 2 переключает цепь сброса делителя частоты 3 со входа ФАПЧ (сигнал t/м) на ее выход (сигнал бми).

Последовательность служебных импульсов - п сохраняет синхронность с сигналом поступающим по цепи сброса. В этом режиме устройство синхронизации реализует фильтрующие и астатические свойства ФАПЧ.

В случае длительных пропаданий сигнала коммутатор 2 производит подключение цепи сброса делителя частоты 3 с выхода на вход ФАПЧ (обратное переключение).

Время, прощедщее с момента пропадания сигнала до момента обратного переключения.

может быть выбрано с помощью времязадающей схемы, входящей в состав .коммутатора 2.

Предмет изобретения

Устройство формирования синхронизирующих последовательностей, содержащее блок фазовой автоподстройки частоты, блок стартстопной синхронизации, состоящий из дещифратора с п формирователями служебных импульсов, делителя частоты, выполненного на триггерах, и блока переключений, отличающееся тем, что, с целью уменьщения времени вхождения в синхронизм, один из входов блока переключений через блок фазовой автоподстройки частоты подключен ко входу устройства, а другой вход блока переключений подключен ко входу устройства непосредственно, при этом один из выходов блока фазовой автоподстройки частоты подключен через

блок переключений к делителю, частоты блока стартстопной синхронизации, а другой выход блока фазовой автоподстройки частоты- непосредственно к делителю частоты блока стартстопной синхронизации, выходы которого своими п формирователями служебных импульсов подключены ко входу устройства обработки информации.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство цикловой синхронизации последовательного модема | 1986 |

|

SU1450123A1 |

| Устройство синхронизации видеомагнитофона | 1982 |

|

SU1149434A1 |

| УСТРОЙСТВО КОНТРОЛЯ СИНХРОНИЗМА КОЛЬЦА ФАЗОВОЙ АВТОПОДСТРОЙКИ ЧАСТОТЫ | 1993 |

|

RU2057395C1 |

| Устройство фазовой автоподстройки частоты | 1981 |

|

SU1091354A1 |

| Устройство синхронизации по несущей частоте | 1983 |

|

SU1124440A1 |

| Цифровой когерентный частотно-фазовый демодулятор | 1979 |

|

SU873453A1 |

| Устройство синхронизации | 1983 |

|

SU1107314A1 |

| УСТРОЙСТВО ПОИСКА И СОПРОВОЖДЕНИЯ СИГНАЛА СИНХРОНИЗАЦИИ В СПУТНИКОВЫХ СИСТЕМАХ СВЯЗИ ПО ПРИЕМУ | 1995 |

|

RU2093964C1 |

| Устройство тактовой синхронизации многоканального сигнала | 1985 |

|

SU1352661A1 |

| УСТРОЙСТВО ВРЕМЕННОГО УПЛОТНЕНИЯ АСИНХРОННЫХ | 1973 |

|

SU385399A1 |

Даты

1971-01-01—Публикация