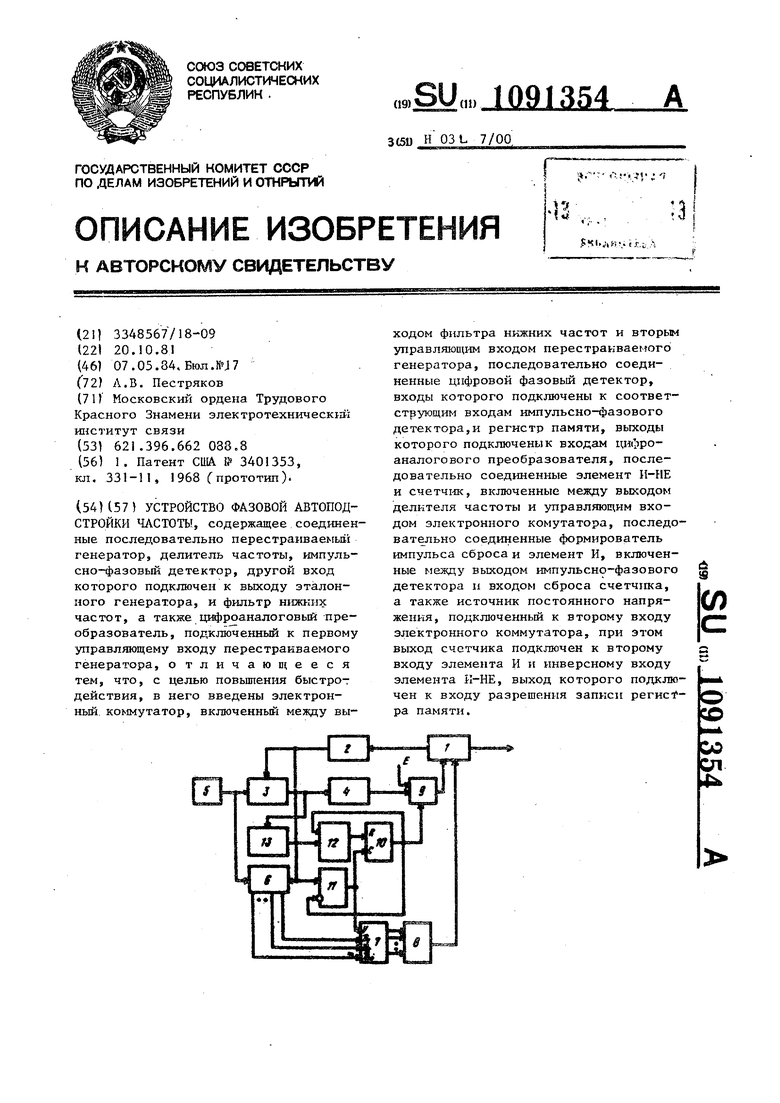

Изобретение относится к радиотехнике и может быть использовано в быстродействутощих системах синхронизации, с штезаторах частоты к радкоизмерительных устройствах. Наиболее близким к предлагаемому по технической сущности является устройство фазовой автоподстройки частоты (ФАПЧ), содержащее соединенные последовательно перестраиваемьй генератор, делитель частоты, импульсно-фазовый детектор, другой вход которого подключен к выходу эталонного генератора и ф1шьтр нижних частот , а также цифроаналогрвый преобразователь, подключенный к первому управляющему входу перестраиваемого генератора Cl J . Однако известное устройство обладает невысоким быстродействием, так как подстройка частоты nepecTpairaaeмого генератора известного устройства 1 в широком диапазоне частотных расстроек производится в основном по грубому каналу, содержащему, в частности, цифроаналоговьш преобразователь лутем изменения кода. Частота изменения кода равна разности час-. тот эталонного и перестраиваемого генераторов. Таким образом, по мере уменьшения частотной расстройки эффект1шность подстройки по грубому каналу уменьшается. Кроме того, в момент равенства частот рабочая точка обычно находится вблизи границ полосы захвата по точному кольцу под стройки, что снизсает помехоустойчивость устройства, Цель изобретения - повышение быст родействия устройства, Для достижения поставленной цели в устройство фазовой автоподстройки частоты, содержащее соединенные последовательно перестраиваемый генератор, делитель частоты, импульсно- фазовый детектор, другой вход которо го подключен к выходу эталонного генератора и Н1ЖНИХ частот, а также цифроаналоговьш преобразователь, подключенный к первому управля щему входу перестраиваемого генератора, введены электронный коммутатор включенный меящу выходом ф1шьтра ниж них частот и вторым управлякяцим входом перестраиваемого генератора, пос ледовательно соединенньш цифровой фа зовый детектор , входы которого подключены к соответствующим входам импульсно-фаэового детектора, и регистр памяти fвыходы которого подключены к входам ци(1роаналогового преобразователя, последовательно соединенные элемент И-НЕ и счетчик, включенные между выходом делителя частоты и управляющим входом электронного коммутатора, последовательно соединенные формирователь импульса сброса и элемент И, включенные между выходом импульснофа.эового детектора и входом сброса счетчика, а также источник постоянного напряжения, подключенный к входу электронного коммутатора, при этом выход счетчика подключен также к второму входу элемента И и 1шверсному входу элемента И-НЕ, выход которого подключен к входу разрешения записи регистра памяти. На чертеже представлена структурная электрическая схема ФАГ1Ч, Устройство ФЛПЧ содержит перестраиваемый генератор (ПГ) 1, делитель 2 частоты импульсно-фазовьш детектор (НФД) 3, фильтр нижних частот (ФНЧ)4, эталонньтй генератор (ЭГ) 5, цифровой фазовьш детектор (ЦФД) 6, регистр 7 памяти, цифроаналоговьш преобразователь (иДЛ) 8, электронный коммутатор 9, сче1чик 10, элемент Н-НЕ 11, элемент II 12 и формирователь 13 икпульса сброса, Устройство работает следующим образом, Подстройка частоты ПГ 1 производится по двум каналам: грубому и точному, причем эти каналы работают поочередно. Перестройка по грубому каналу осуг ествляется изменением напряжения на выходе ЦАП 8 в соответствии сизменением кодав регистре 7 памяти, который соответствует коду на выходе ЦФД 6 в момент прихода сигнала разрешения записи в регистр 7 намяти, В предлагаемом устройстве ЦФД 6 вырабатьшает цифровой код, вес которого пропорционален разности фаз сигналов5 поступающих на вход 6, ЦОД 6 может быть реализован например по известной схеме измерения фазового.сдвига (временного интервала) методом дискретного счета преобразования временного интервалу в код, Один раз за период регулирования (в момент прихода тЕМпульса с выхода делителя 2 частоты происходит перезапись кода с выхода ЦФД. 6 в реги-стр 7 памяти. На входе V регистра 7 памяти в момент перезаписи кода имеется сигнал 1 за счетпрохождения импульса с выхода делителя 2 частоты через логический элемент И-НЕ I1«На выходе ЦДЛ 8 формируется напряжение пропорциональное весу кода записанного в регистре 7 памяти, т.е. пропорциональное фазовому рассогласованию сигналов, поступающих на входы ЦФД 6. Известно, что длительность и характер переходного процесса дискретной системы ФАЛЧ существенно зависит от обобщенного параметра кольца автоподстройки 57уТ F( , где fly, - полоса удержания по грубому ка J „ . налу подстройки; Тр - период регулирования в системе, Р(%) крутизна характеристики эквивалентного фазового детектора. При этом для дискретных систем ФАЛЧ всегда можно подобрать параметры таким образом, что длительность переходного процес са всегда будет минимальной- в преде ле до одного периода регулирования при Й,,Тр К В предлагаемом устройстве это условие всегда вьшол нимо, так как путем отключение управ ления грубым каналом подстройки в стационарном режиме выбор параметров системы по грубому каналу не связан с необходимостью обеспечения других требований, таких как, например, фильтрация -побочных дискретных и флюктуационных помех. Таким образом удается реализовать быстродействие, близкое к предельно возможному для дискретньк систем с заданньм периодо дискретизации. Как бьто отмечено вьшш, в предлагаемом устройстве грубый и точный каналы подстройки работают поочередно. Выбором соотношений полос удержания по грубому и точному каналам обеспечивается как перекрытие необходимого диапазона частот, так и реализуется требуемая фильтрация , внепших возмущений, при этом переклю чение каналов производится таким образом, что в стационарном режиме положение рабочей точки на характеристике р}ФД 3 близко к середине рабочего участка. Это достигается тем, что во время работы грубого канала под-- 55 стройки на выходе точного канала (на первом управляюп1ем входе ПГ 1 )/ поддерживается постоянное напряжение Up $

ка 10 постзшает на управляющий вход электронного коммутатора, который при этом переключает первый управляющий вход ПГ I от источника напряжения к выходу ФНЧ 4. После этого производится точная подстройка частоты ПГ 1. Длительность переходного процесса по точному каналу также может быть соответствукяцее среднему значению напряжения с выхода ИФД 3. После за,верпения подстройки по грубому каналу на выходе ЦАП 8 вырабатьшается такое напряжение U, при котором синхронизм в системе с тдествует за счет действия суммы двух воздействий: f li U(. , При переключении на точный канал подстройки напряжение на выходе грубого канала сохраняется неизменным, при этом, очев1здно, что для поддержания синхронизма ИФД 3 должен вырабатывать напряжение, близкое к, т.е. в системе ФАПЧ всегда устанавливается такой режим работы, при котором рабочая точка находится в середине рабочего участка характеристики ИФД 3. Для поочередного подключения грубого и точного каналов подстройки используется счетчик 10 и электронньш комг утатор 9, Необходимое время работы грубого канала задается емкостью счетчика 10, который подсчитывает количество периодов регулирования, прошедших с момента начала переходного процесса. Для этого на счетный вход с счетчика 10 через логический элемент И-ПЕ J.1 поступают импульсы с выхода делителя 2 частоты, которые также подаются на вход регистра 7 памяти. По прошествии заданного числа периодов регулирования (за которое переходной процесс по грубому каналу должен заведомо завершиться ) на выходе счетчика 10 появляется сигнал Г% который препятствует прохождению импульсов с выхода делителя 2 частоты на вход со счетчкка iO и на вход регистра 7 памяти. Таким образомj перестройка частоты по грубому каналу прекращается . Во время работы грубогЪ канала, ак было отмечено выше, на первьш правляющий вход ПГ 1 через электрюный коммутатор 9 подается постоянное апряжение Е , соответствующее средему значению напряжения с выхода ФД 3. После завершения грубой под- тройки сигнал 1 с выхода счетчиMHHHMii3HpoBaHia соответствующим выбором параметров кольца импульсной ФАПЧ, Полное время переходного процесса по грубому и точному каналам при оптимальном выборе параметров не превьшает нескольких периодов регулированияДля автоматического переключения в режим грубой подстрО1ЖИ, что бьшае необходимо при срьше синхронизма под действием больших возмущений., например при смене коэффициента деления делителя 2 частоты или под действием помех, используется схема формирования сигнала сбррса 13. Схе ма формирования сигнала сброса 3 представляет собой компаратор напря жения с двумя парогамк срабатывания и и и, . В режиме синхронизма и, ифд-си |Где Ьф-Q- напряжение на выходе фазового детек-тора. Величина U2-U Ь образует зону нечувстви тельности. Величина ( выбирается из соображений обеспечения максимал ной помехозащищенности устройства с учетом характера всех возможных типов возмущений, действующих на устройство, Прк любом нарушении синхронного pejKiuxa разность фаз сигналов, поступающих на ИФД 3, начинает, возрастать Из соответственно, изменяется напряжение на выходе ИФД 3, Если зна чения напряжения на вьжоде ИФД 3 вы ходит за пределы зоны нечувствительности, схема формирования сигнала сброса 13 вырабатывает сигнал I, который через элемент И 12 производит сброс счетчика 10 в нулевое состояние. После установки счетчика 10 в О дальнейшее изменение состояния 10 возможно только по входу С, так как в этом случае элемент И 12 препятствует проникновению сиг-т нала со схемы 13 формирования сброса, что исключает ложное срабатывание всего звена, управляющего переключением каналов подстройки. По прошествии заданного числа периодов регулирования, необходимых для обеспечения надежного вхождения в синхронизм, ка выходе счетчика 10 появляется сигнал 1, который блокирует посредством элемента И-НЕ 11 дальнейшее поступление импульсов на вход С счетчика 10 и на вход V регистра 7 памяти, подстройка по грубому каналу заверпшется После этого второй счетчик 10 опять может быть установлен в О при появлении сигнала на выходе схемы 13 формирования сброса (при нарушении синхронизма), так как сигнал 1 с выхода счетчика 10 разрешает прохоиздение сигнала сброса через элемент И 12 на вход R счетчика 10. Таким образом,повьш ается быстродействие устройства, т.е. достигается быстродействие, близкое к предельйому для данного типа устройства при широкой полосе захвата (равной полосе удержания по грубому каналу подстройки) и эффективной фильтрации возмущений в стационарном режиме точным (узкополосным )кольцом подстройки ф

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство фазовой автоподстройки частоты | 1987 |

|

SU1478326A1 |

| Цифровой синтезатор частоты | 1984 |

|

SU1234966A1 |

| Устройство фазовой автоподстройки частоты | 1984 |

|

SU1352645A1 |

| УСТРОЙСТВО ПОИСКА И ОБНАРУЖЕНИЯ ШУМОПОДОБНОГО СИГНАЛА | 1979 |

|

SU1840447A1 |

| Устройство фазовой автоподстройки частоты | 1985 |

|

SU1338071A1 |

| Цифровой синтезатор частоты с частотной модуляцией | 1987 |

|

SU1543544A1 |

| Синтезатор частот | 1987 |

|

SU1543545A1 |

| Устройство для измерения скорости телеграфирования | 1974 |

|

SU547042A1 |

| УСТРОЙСТВО ПОИСКА ШИРОКОПОЛОСНОГО СИГНАЛА | 1980 |

|

SU1840288A1 |

| Синтезатор частот | 1985 |

|

SU1363457A1 |

УСТРОЙСТВО ФАЗОВОЙ АВТОПОДСТРОЙКИ ЧАСТОТЬ, содержащее соединен ные последовательно перестраиваемы генератор, делитель частоты, импульсно-фазовый детектор, другой вход которого подключен к выходу эталонного генератора, и фильтр нижних частот, а также цифр аналоговый преобразователь, подключенный к первому управляющему входу перестраиваемого генератора, о тличающееся тем, что, с целью повышения быстрот действия, в него введены электронный, коммутатор, включенный между выходом фильтра нижних частот и вторым управляющим входом перестраиваемого генератора, последовательно соединенные цифровой фазовый детектор, входы которого подключены к соответструющим входам нмпульсно-фазового детектора,и регистр памяти, выходы которого подключенык входам цифроаналогового преобразователя, последовательно соединенные элемент И-НЕ и счетчик, включенные между выходом делителя частоты и управляющим входом электронного комутатора, последовательно соединенные формирователь импульса сброса и элемент И, включенные между выходом импульсно-фазового детектора и входом сброса счетчика, а также источник постоянного напряжения, подключенньй к второму входу электронного коммутатора, при этом выход счетчика подключен к второму входу элемента И и инверсному входу элемента К-НЕ, выход которого подключен к входу разрешения записи регистра памяти.

Авторы

Даты

1984-05-07—Публикация

1981-10-20—Подача