Изобретение относится к области автоматики н вычислительной техннкн.

Известны формирователи нмнульеов на иотенциальиых логических элементах, вырабатывающие имиульсы от нереднего н заднего фронтов входного нмиульса.

Недостатками ПОДООНЕЯХ формирова гслои импульсов являются сложиость схемы 1 отсутствие возможности сиимать импульсы обеих полярностей с требуелюй задержкой входного импульса.

Целью изобретения

является у11р01ИСИ1 с схемы формирователя

нмнульсои при одноего функциональных временном раеширеппи возможиоетей.

Это достигается тем, что входпая пита формирователи соединена 1 еносредствеп1го со схемой «IIU,- П и через нлечо т|5нггера с цеH04KO i 1Г{ нечетного числа ннверторов, выход которой нодключен ко входу противоположного нлеча триггера, а выход этого плеча БЫведе) иа вие1ипюю игииу. Второй вход схемы «ML:-И соединен с одпо1г нз выходных ni.ini четных нпверторов, а выход - с соответствующей выходной П1ННОЙ. Выход четных н нечетных инверторов выведены на соответствующие выходиые нгпны.

н, кроме Toio, штзволяет злдержпиа гь иходпой 1ьм пульс.

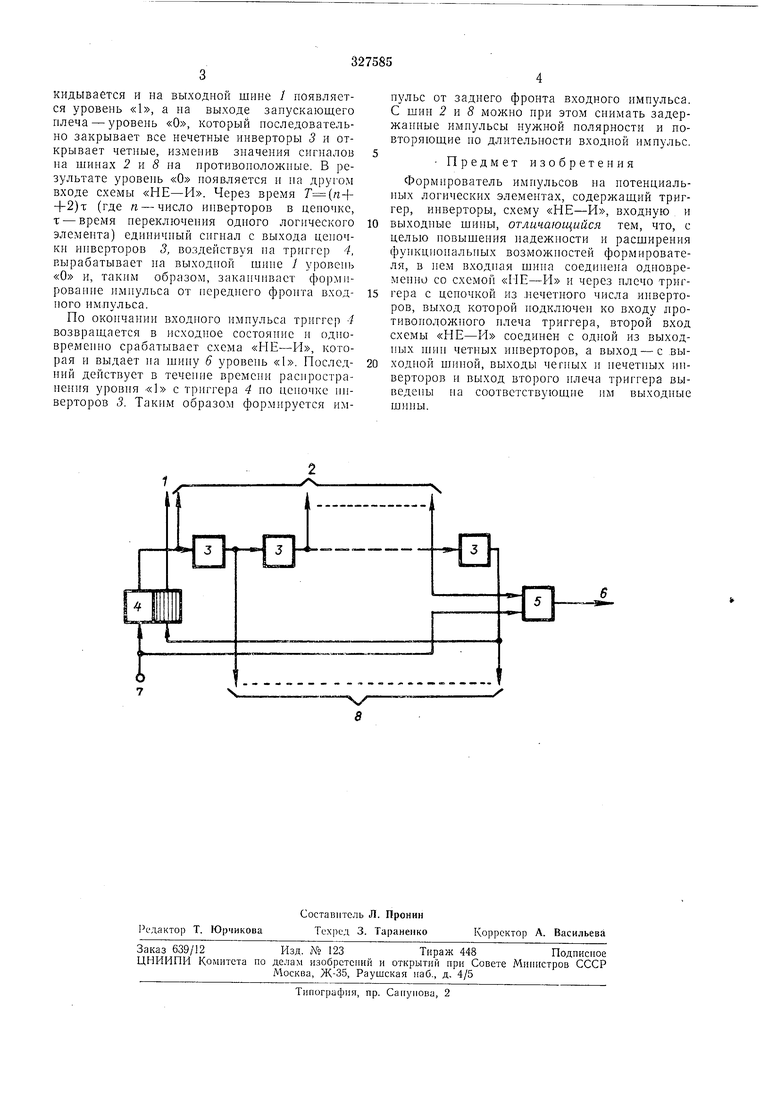

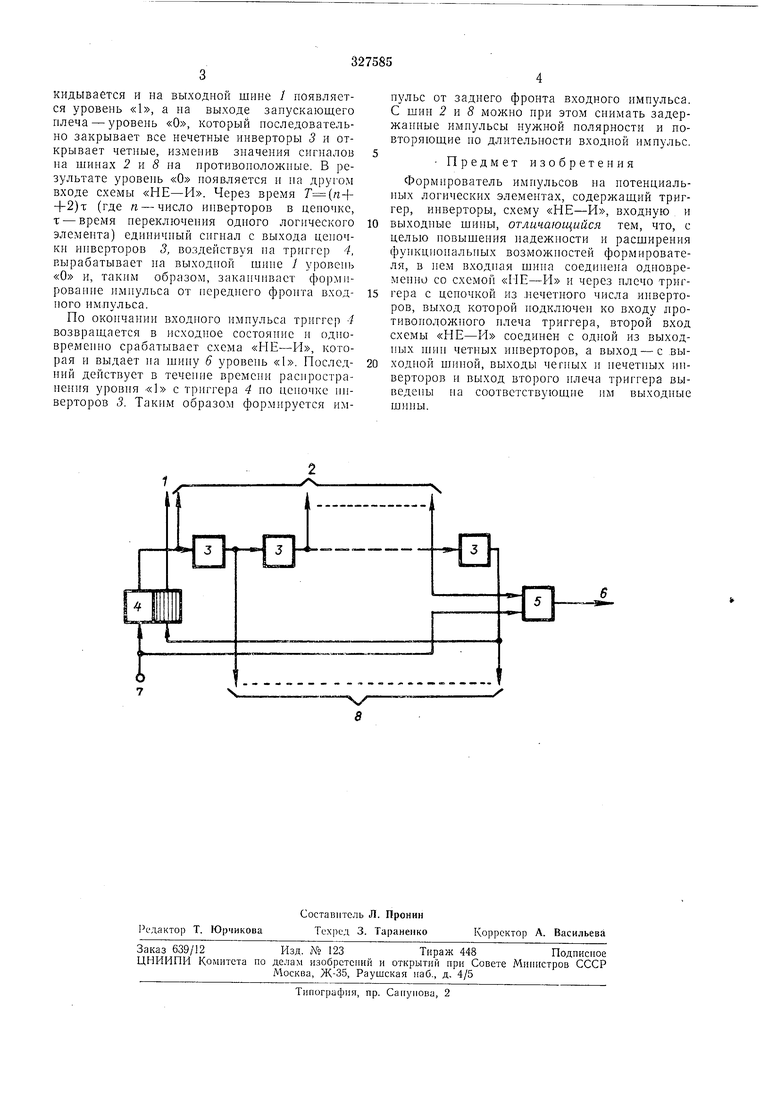

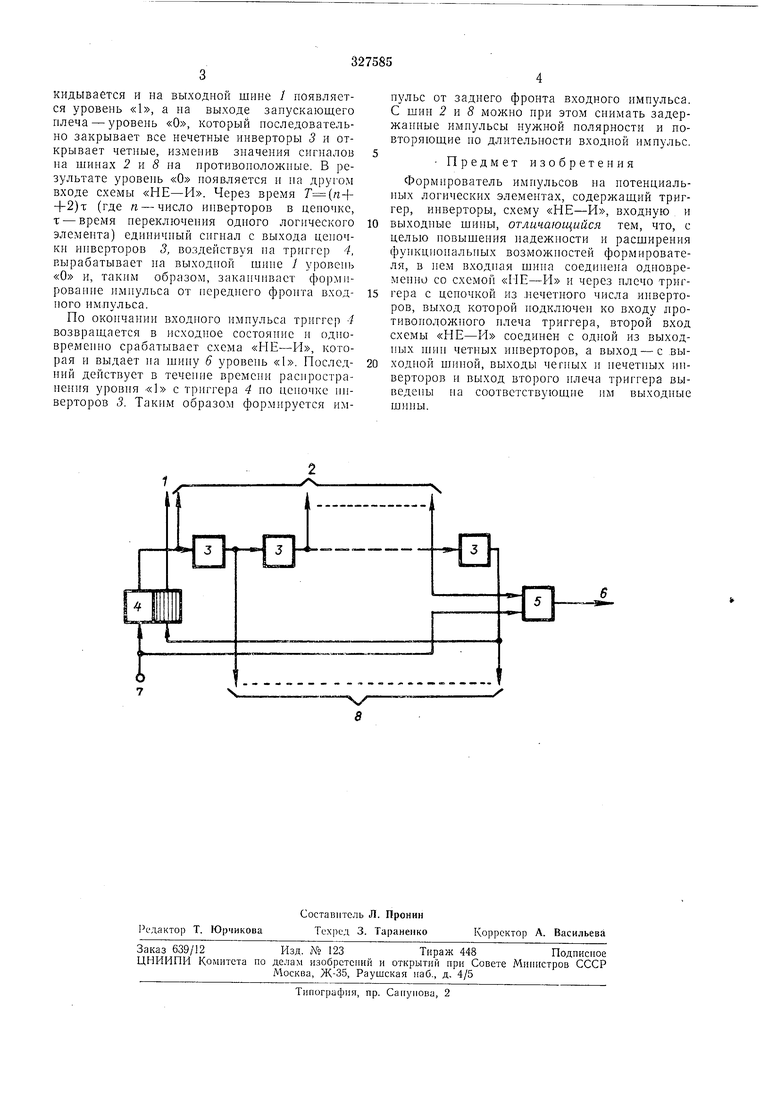

На чертеже изображена б.юк-схема оннсг.1liae.Moro (|н)рмир1)вателя.

Формирователь еол,ержнт вьгходную / д,1Я импульса, С())Ормпрс)ванн01Х) но ие|) ф)О11ту вход||1)1О iiMii .ibc;i; иг.гходпьк питы 2 четных HunepTOjuin для задерж ; H();,() нмнульса с 1гзмене|111ем его nvXJHjMiocrH ц для

регулировки длительности iiMH.ii,c;i, cijiopMiiрованного от задне1о ijp - входно1Ч) имнульса; инвертор), , статическш тр;11тер /, схему «i lv--n /J; г ыходну)о ншнх 6 для имнульса, с4)орМ11ро: а liiioro or .чад11е1(| ijijiOHTa

входного импульса; входнхю Hiiiiiy 7 ii .чодные ПП1ПЫ 8 печегных jiHiiepTopiiB задержки входного ьмну. с ci;)x ранением его полярности.

Формирователь р);|ботает следуIOIHIIM образом.

После подачи напряжения ппгаппя на схему формирователя иоследни са inyciапав.ч.чвается в исходиое состояние. При :-) на ныходе заиускаю1иего нлеча т|лиге)а / н n.j выходиых нишах J четных лнвергоро ycTaiiaiiлпвается уровень «1, а па выходных пшнах /, 6 и 8- уровеиь «О.

кидывается и на выходной шнне 1 появляется уровень «1, а на выходе запускающего плеча - уровень «О, который последовательно закрывает все нечетные инверторы 3 и открывает четные, изменнв значения сигналов на шинах 2 н 8 на противоноложные. В результате уровень «О ноявляется и на другом входе схемы «НЕ-И. Через время Т(п+ +2) т (где п - число инверторов в цепочке, т - время нереключения одного логического элемента) единичный сигнал с выхода цепочки инверторов 3, воздействуя на триггер /, вырабатывает на выходной шине / уровень «О и, таким образом, заканчивает формирование импульса от переднего фроита входпого имлульса.

По окончании входного импульса триггер -/ возвращается в исходное состояние и одновременно срабатывает схема «НЕ-И, которая н выдает на щииу 6 уровень «1. Последний действует в течение времени распространения уровня «1 с триггера 4 по цеиочке инверторов 3. Таким образом формируется импульс от заднего фронта входного импульса. С шин 2 и 8 можно при этом снимать задержанные имиульсы нужной полярности и повторяющие ио длительности входной импульс.

гт

предмет изобретения

Формирователь имиульсов на потенциальных логических элементах, содержащий триггер, инверторы, схему «НЕ-И, входную и

выходные шииы, отличающийся тем, что, с целью повышения надежности и расширения функциональных возможностей формирователя, в нем входная шииа соединена одновременно со схемой «ME-П и через плечо трнггера с цепочкой из .нечетного числа инверторов, выход которой подключен ко входу противоположного плеча триггера, второй вход схемы «НЕ-И соединен с одной из выходиых И1НН четных инверторов, а выход - с ,выходной шиной, выходы черных и нечетных инверторов н выход второго нлеча триггера выведены на соответствующие им выходные шины.

| название | год | авторы | номер документа |

|---|---|---|---|

| РЕГУЛЯТОР ЭЛЕКТРИЧЕСКИХ ВЕЛИЧИН ДИСКРЕТНОГО ДЕЙСТВИЯ | 1970 |

|

SU269259A1 |

| ЗНАЯ | 1973 |

|

SU363908A1 |

| Б | 1973 |

|

SU406312A1 |

| Формирователь последовательности кодов | 1974 |

|

SU526870A1 |

| Клавиатура для ввода данных | 1973 |

|

SU495784A1 |

| МНОГОУСТОЙЧИВЫЙ ЭЛЕМЕНТ С 2/V+1 УСТОЙЧИВЫМИСОСТОЯНИЯМИ | 1972 |

|

SU429537A1 |

| УСТРОЙСТВО для УПРАВЛЕНИЯ ЦИФРОВЫМИ ПРИБОРАМИ ПОРАЗРЯДНОГО УРАВНОВЕШИВАНИЯ | 1973 |

|

SU409230A1 |

| УНИВЕРСАЛЬНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ | 1964 |

|

SU164471A1 |

| УСТРОЙСТВО Для ОБНАРУЖЕНИЯ И ИЗМЕРЕНИ МАКСИМУМА СИГНАЛАВСЕСОЮЗНАЯ^йТ:НТШ'1:-п:^'^^ШйБ: 1Б л ПОТЕКА | 1971 |

|

SU308520A1 |

| ФОРМИРОВАТЕЛЬ ИМПУЛЬСОВ ПОСТОЯННОЙ ВОЛЬТ-СЕКУНДНОЙ ПЛОЩАДИ | 1971 |

|

SU320928A1 |

Авторы

Даты

1972-01-01—Публикация