1

Изобретение относится к построению узлов вычислительной техники и дискретной автоматики в микроэлектронном исполнении, .в частности в виде больших интегральных схем.

Известный многоустойчивый элемент с 2.V-j-l устойчивыми состояниями (где , 2, 3 ...) построен в логическом базисе «И- ИЛИ-НЕ на основе одного триггера памяти, имеющего 27V-|-1 устойчивых состояний, и одного коммутационного триггерного устройства, синхронизирующего переключение триггера.

Цель изобретения - упрощение схемы многоустойчивого элемента и уменьщение его потребляемой мощности.

Для этого многоустойчивый элемент с устойчивыми состояниями (где , 2, 3...) строится на основе соединения одного триггера памяти с 2:V+1 устойчивыми состояниями и одного коммутационного триггерного устройства, производящего пересчет 2N входных импульсов по модулю 2, регистрацию 2Л-го импульса и сбрасываемого в исходное состояние .задним фронтом ()-го импульса, и осуществляет пересчет входных импульсов по модулю 2/V-)-l в коде «1 из (2.V+1).

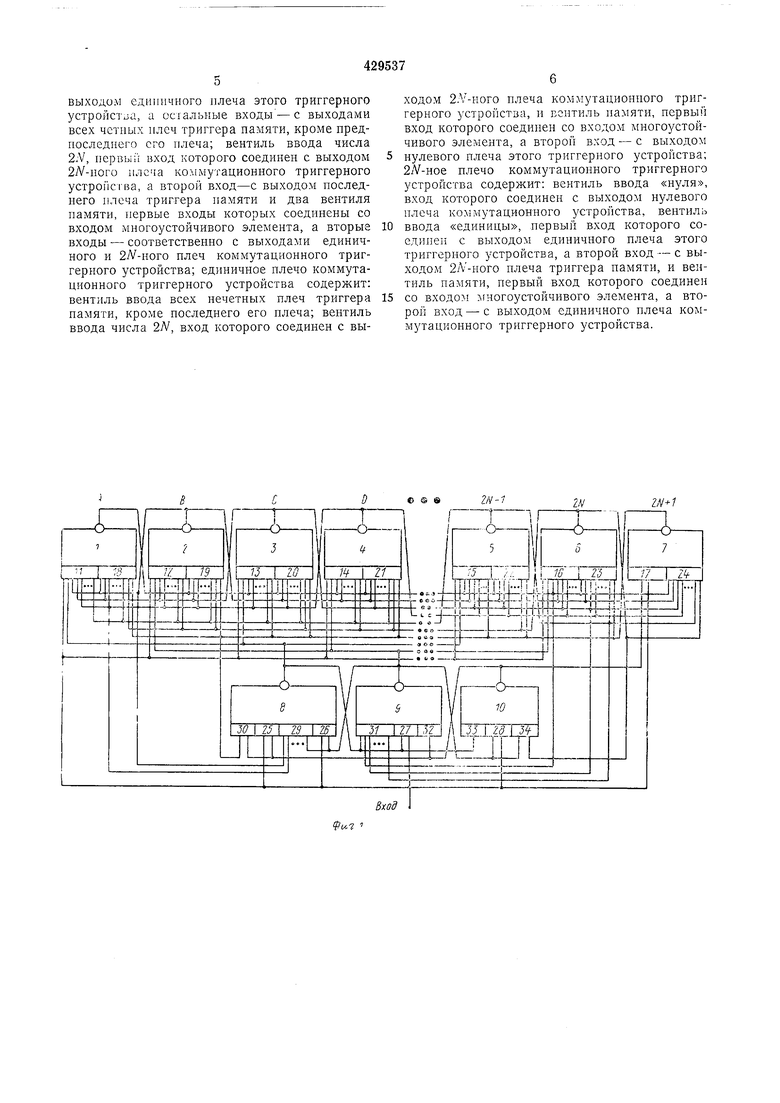

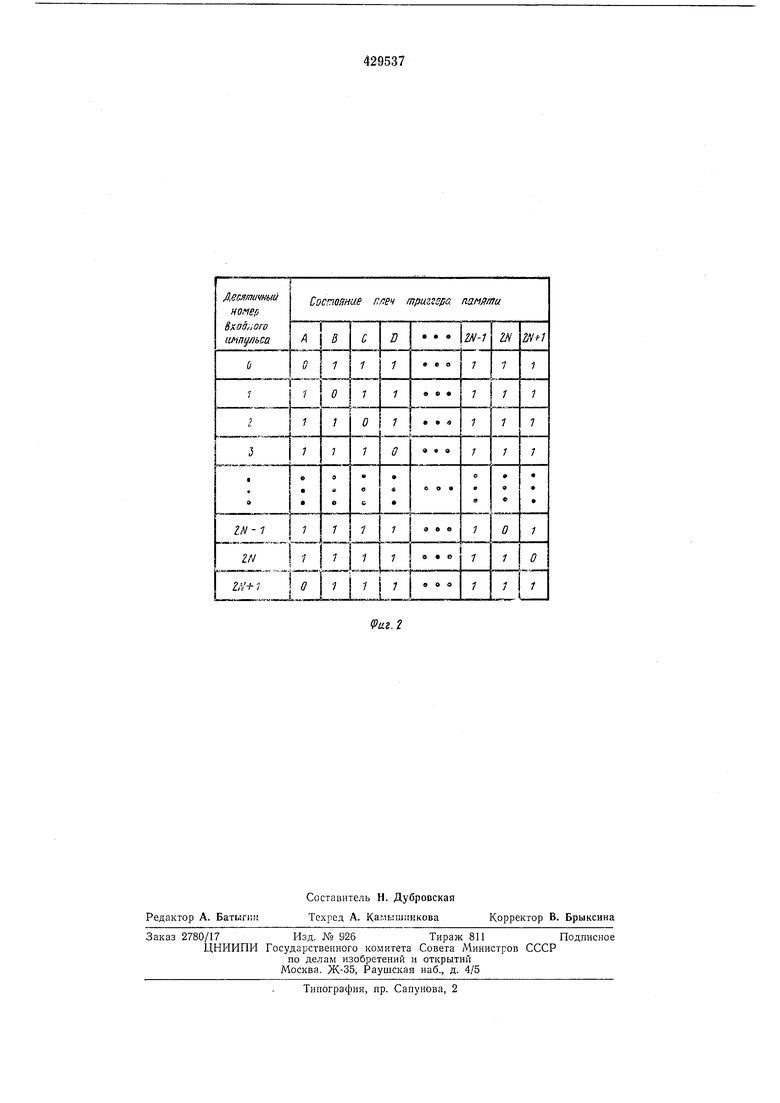

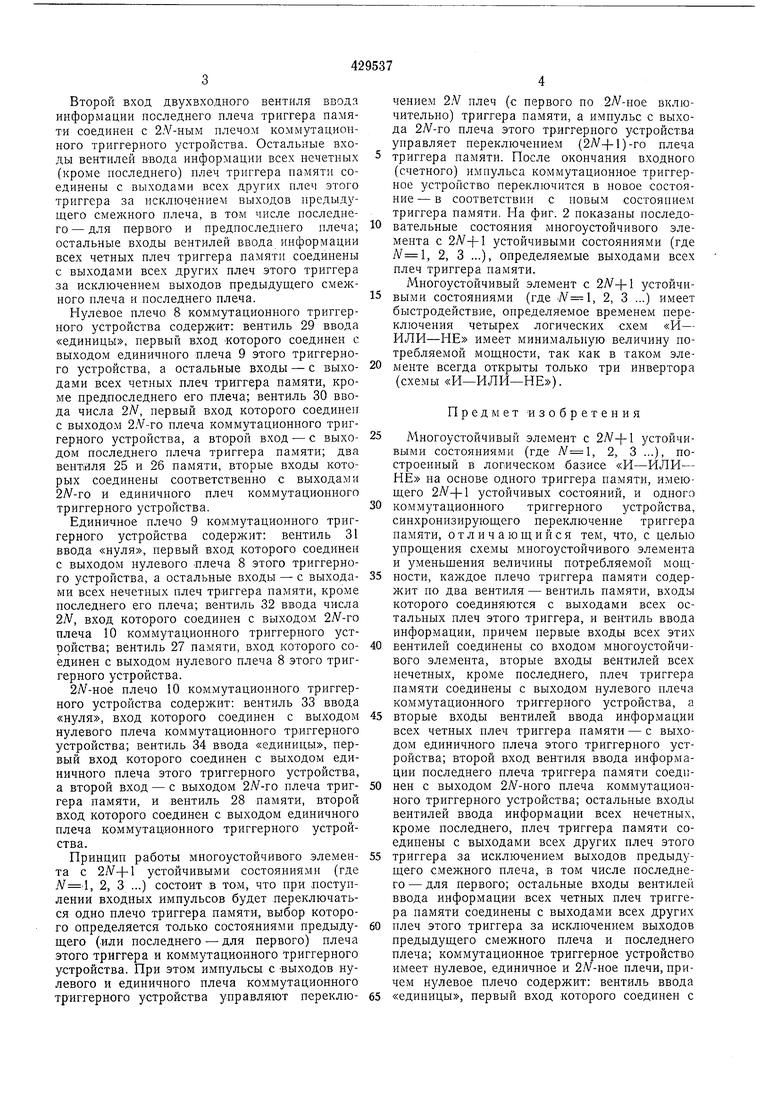

На фкг. 1 . представлена .функциональная схема, предлагаемого многоустойчивого элемента с 2Л-}-1 устойчивыми состояниями; на фиг. 2 - таблица состояний этого элемента.

Многоустойчивый элемент с 2ЛГ+1 устойчивыми состояниями (где , 2, 3...) построен Б логическом базисе «И-ИЛИ-НЕ и образован соединением триггера памяти с

устойчивыми состояниями (1-4 ... 5-7) и коммутационного триггерного устройства 8- 10, производящего пересчет 2N входных импульсов по модулю 2, регистрирующего 2Nный импульс и сбрасываемого в исходное состояние задним фронтом ()-го импульса.

Плечи триггера памяти содержат по одному вентилю 11 -17 ввода информации и по одному вентилю 18-24 памяти для образоваВИЯ триггерных связей: входы вентиля памяти любого плеча триггера памяти соединены с выходами всех остальных плеч этого триггера. Информационный (счетный) вход многоустойчивого элемента с 2Л-|-1 устойчивыми

состояниями соединен с первыми входами вентилей ввода информации всех плеч триггера памяти и со входами вентилей 25-28 памяти коммутационного триггерного устройства. Вторые входы вентилей ввода информации всех

нечетных (кроме последнего) плеч триггера памяти соединены с выходом нулевого плеча 8 коммутационного триггерного устройства, а вторые входы вентилей ввода информации всех четных плеч триггера памяти - с выходом единичного плеча 9 этого триггерного устройства. Второй вход двухвходного вентиля ввода информации последнего плеча триггера памяти соединен с 2Л-ным плечом коммутационнего триггерного устройства. Остальные входы вентилей ввода информации всех нечетных (кроме последнего) плеч триггера памяти соединены с выходами всех других плеч этого триггера за исключением выходов предыдущего смежного плеча, в том числе последнего-для первого и предпоследнего плеча; остальные входы вентилей ввода информации всех четных плеч триггера памяти соединены с выходами всех других плеч этого триггера за исключением выходов предыдущего смежного плеча и последнего плеча. Нулевое плечо 8 коммутационного триггерного устройства содержит: вентиль 29 ввода «единицы, первый вход которого соединен с выходом единичного плеча 9 этого триггерного устройства, а остальные входы - с выходами всех четных плеч триггера памяти, кроме предпоследнего его плеча; вентиль 30 ввода числа 2jV, первый вход которого соединен с выходом 2.V-ro плеча коммутационного триггерного устройства, а второй вход - с выходом последнего плеча триггера памяти; два вентиля 25 и 26 памяти, вторые входы которых соединены соответственно с выходами 2N-ro и единичного плеч коммутационного триггерного устройства. Единичное плечо 9 коммутационного триггерного устройства содержит: вентиль 31 ввода «нуля, первый вход которого соединен с выходом нулевого плеча 8 этого триггерного устройства, а остальные входы - с выхода-35 ми всех нечетных плеч триггера памяти, кроме последнего его плеча; вентиль 32 ввода числа 2N, вход которого соединен с выходом 2N-ro плеча 10 коммутационного триггерного устройства; вентиль 27 памяти, вход которого со-40 единен с выходом нулевого плеча 8 этого триггерного устройства. 2jV-Hoe плечо 10 коммутационного триггерного устройства содержит: вентиль 33 ввода «нуля, вход которого соединен с выходом45 нулевого плеча коммутационного триггерного устройства; вентиль 34 ввода «единицы, первый вход которого соединен с выходом единичного плеча этого триггерного устройства, а второй вход - с выходом 2М-то плеча триг-50 гера памяти, и вентиль 28 памяти, второй вход которого соединен с выходом единичного плеча коммутационного триггерного устройства. Принцип работы многоустойчивого элемен-55 та с 2iV+l устойчивыми состояниями (где ., 2, 3 ...) состоит в том, что при поступЛенин входных импульсов будет переключаться одно плечо триггера памяти, выбор которого определяется только состояниями предыду-60 щего (.или последнего - для первого) плеча этого триггера и коммутационного триггерного устройства. При этом импульсы с выходов нулевого и единичного плеча коммутационного триггерного устройства управляют переклю-65 чением 2.V плеч (с первого по включительно) триггера памяти, а импульс с выхода плеча этого триггерного устройства управляет переключением {2Л+1)-го плеча триггера памяти. После окончания входного (счетного) импульса коммутационное триггерное устройство переключится в новое состояние - в соответствии с новым состоянием триггера памяти. На фиг. 2 показаны последовательные состояния многоустончнвого элемента с 2Л/-)-1 устойчивыми состояниями (где , 2, 3 ...), определяемые выходами всех плеч триггера памяти. Многоустойчивый элемент с 2jV-f 1 устойчивыми состояниями (где , 2, 3 ...) имеет быстродействие, онределяемое временем переключения четырех логических схем «И- ИЛИ-НЕ имеет минимальную величину потребляемой мощности, так как в таком элементе всегда открыты только три инвертора (схемы «PI-ИЛИ-НЕ), Предмет изобретения Многоустойчивый элемент с устойчивыми состояниями (где , 2, 3 ...), построенный в логическом базисе «И-ИЛИ- НЕ на основе одного триггера памяти, имеющего устойчивых состояний, и одного коммутационного триггерного устройства, синхронизирующего переключение триггера памяти, отличающийся тем, что, с целью упрощения схемы многоустоичивого элемента и уменьщения величины потребляемой мощности, каждое плечо триггера памяти содержит по два вентиля - вентиль памяти, входы которого соединяются с выходами всех остальных плеч этого триггера, и вентиль ввода информации, причем первые входы всех этих вентилей соединены со входом многоустойчивого элемента, вторые входы вентилей всех нечетных, кроме носледнего, плеч триггера памяти соединены с выходом нулевого плеча коммутационного триггерного устройства, а вторые входы вентилей ввода информации всех четных плеч триггера памяти - с выходом единичного плеча этого триггерного устройства; второй вход вентиля ввода информации последнего плеча триггера памяти соединен с выходом 2М-ното нлеча коммутационного трнггерного устройства; остальные входы вентилей ввода информации всех нечетных, кроме последнего, плеч триггера памяти соединены с выходами всех других плеч этого триггера за исключением выходов предыдущего смежного плеча, в том числе последнего - для первого; остальные входы вентилей ввода информации всех четных плеч триггера памяти соединены с выходами всех других плеч этого триггера за исключением выходов предыдущего смежного плеча и последнего плеча; коммутационное триггерное устройство имеет нулевое, единичное и плечи, причем нулевое плечо содержит: вентиль ввода «единицы, первый вход которого соединен с выходом единичного плеча этого триггерного устройства, а остальные входы - с выходами всех четных плеч триггера памяти, кроме предпоследнего его плеча; вентиль ввода числа 2;V, первы вход которого соединен с выходом 2Л -1Юго плеча коммутационного триггерного устропсгва, а второй вход-с выходом последнего плеча триггера памяти и два вентиля памяти, первые входы которых соединены со входом многоустойчивого элемента, а вторые входы - соответственно с выходами единичного и 2Л -ного плеч коммутационного триггерного устройства; единичное плечо коммутационного триггерного устройства содержит: iJ,llWnnWiWILIitiVpllV.iv yv-A Jii--- - х - -, - -. вентиль ввода всех нечетных плеч триггера памяти кроме последнего его плеча; вентиль ввода числа 2N, вход которого соединен с выходом 2.V-Horo плеча коммутационного триггерного устройства, п вентиль памяти, первый вход которого соединен со входом многоустойчивого элемента, а второй вход - с выходом нулевого плеча этого триггерного устройства; 2N-HOQ плечо коммутационного триггерного устройства содержит: вентиль ввода «нуля, вход которого соединен с выходом нулевого плеча коммутационного устройства, вентиль ввода «единицы, первый вход которого соединен с выходом единичного плеча этого триггерного устройства, а второй вход - с выходом 2Л-ного нлеча триггера памяти, и вентиль памяти, первый вход которого соединен I со входом многоустойчивого элемента, а второй вход - с выходом единичного плеча коммутационного триггерного устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| КОЛЬЦЕВОЙ СЧЕТЧИК ПО МОДУЛЮ Л | 1972 |

|

SU421133A1 |

| Счетчик по модулю 4 | 1972 |

|

SU523529A1 |

| Счетчик по модулю 4 @ | 1982 |

|

SU1257840A2 |

| УСТРОЙСТВО ДЛЯ ВОСПРОИЗВЕДЕНИЯ | 1973 |

|

SU397905A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ СЧЕТЧИКОМ ИМПУЛЬСОВ | 1968 |

|

SU208339A1 |

| Разряд счетчика по модулю три | 1971 |

|

SU445989A1 |

| Блок коммутирующей среды | 1975 |

|

SU602938A1 |

| Устройство для умножения чисел, представленных фазо-импульсными кодами | 1972 |

|

SU439807A1 |

| ПРЕОБРАЗОВАТЕЛЬ НАПРЯЖЕНИЯ В КОНТРОЛИРУЮЩИЙСЯ | 1968 |

|

SU206906A1 |

| УСТРОЙСТВО для УМНОЖЕНИЯ ЧИСЕЛ, НРЕДСТАВЛЕННЫХ ФАЗОИМПУЛЬСНЫМИ ДЕСЯТИЧНЫМИ КОДАМИ | 1973 |

|

SU384104A1 |

Даты

1974-05-25—Публикация

1972-07-04—Подача