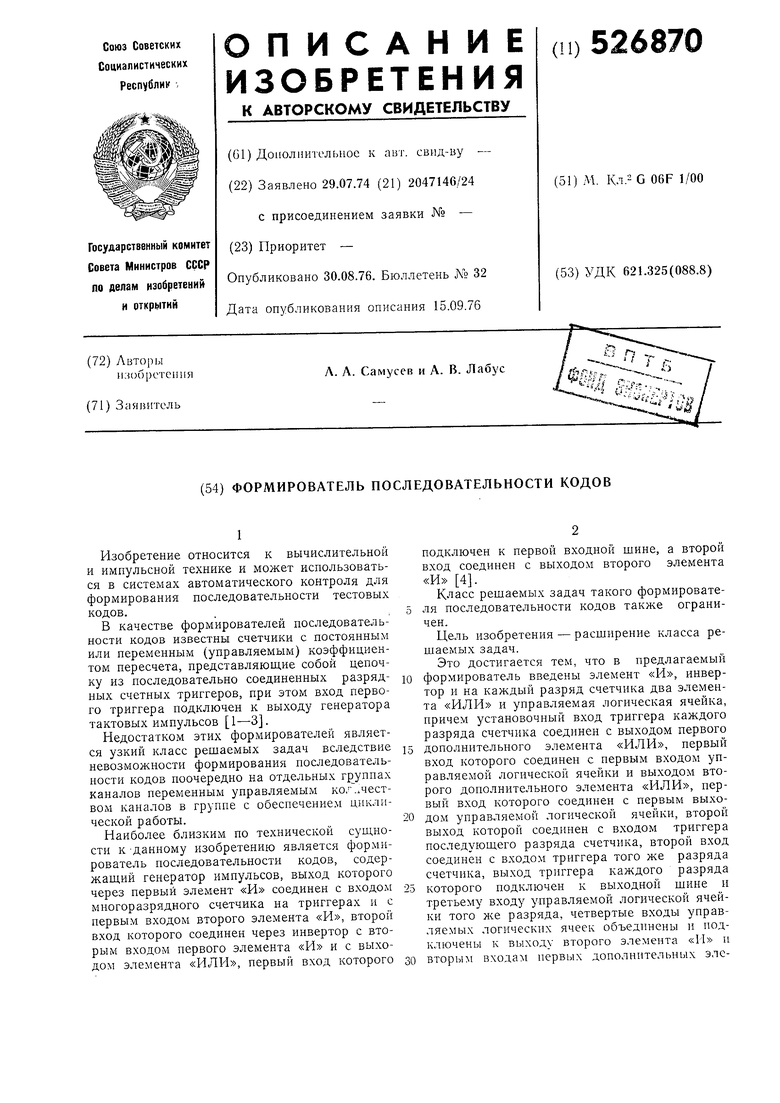

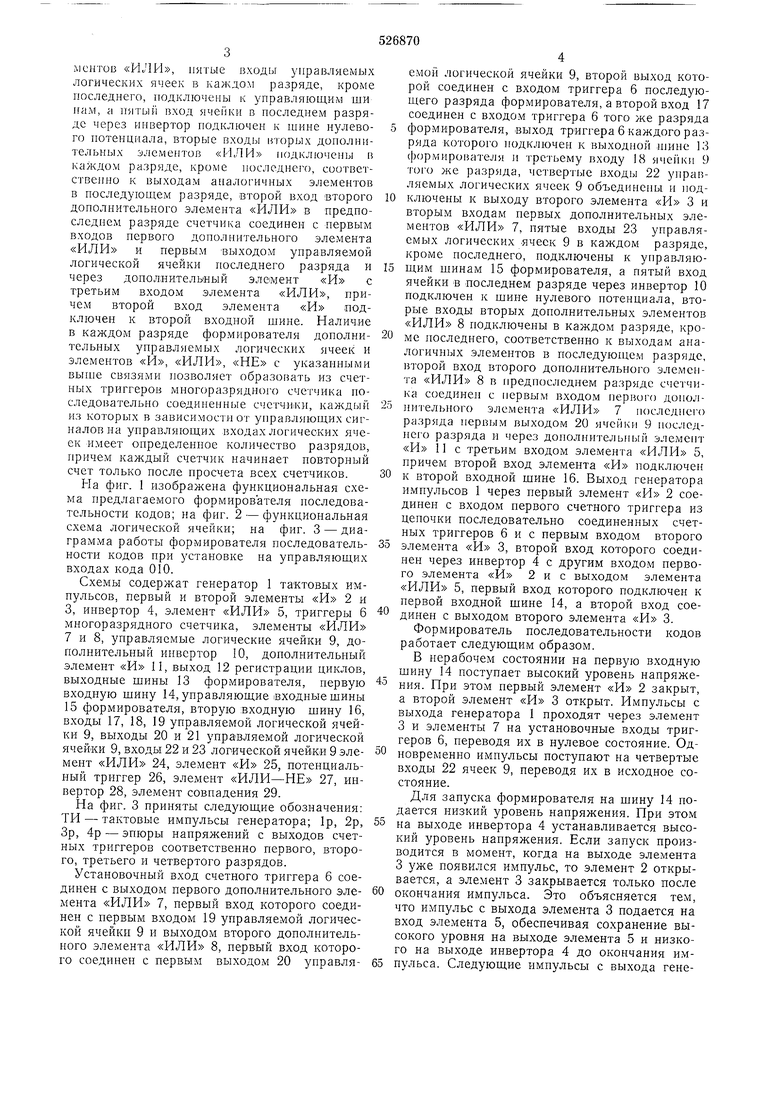

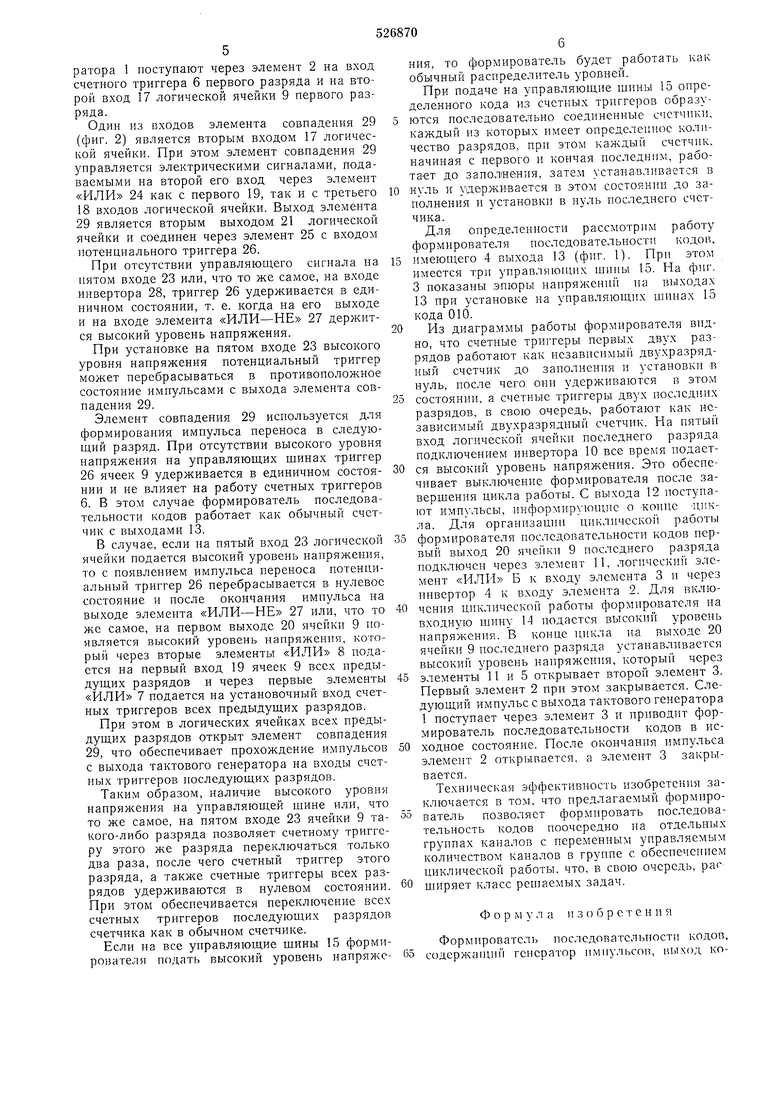

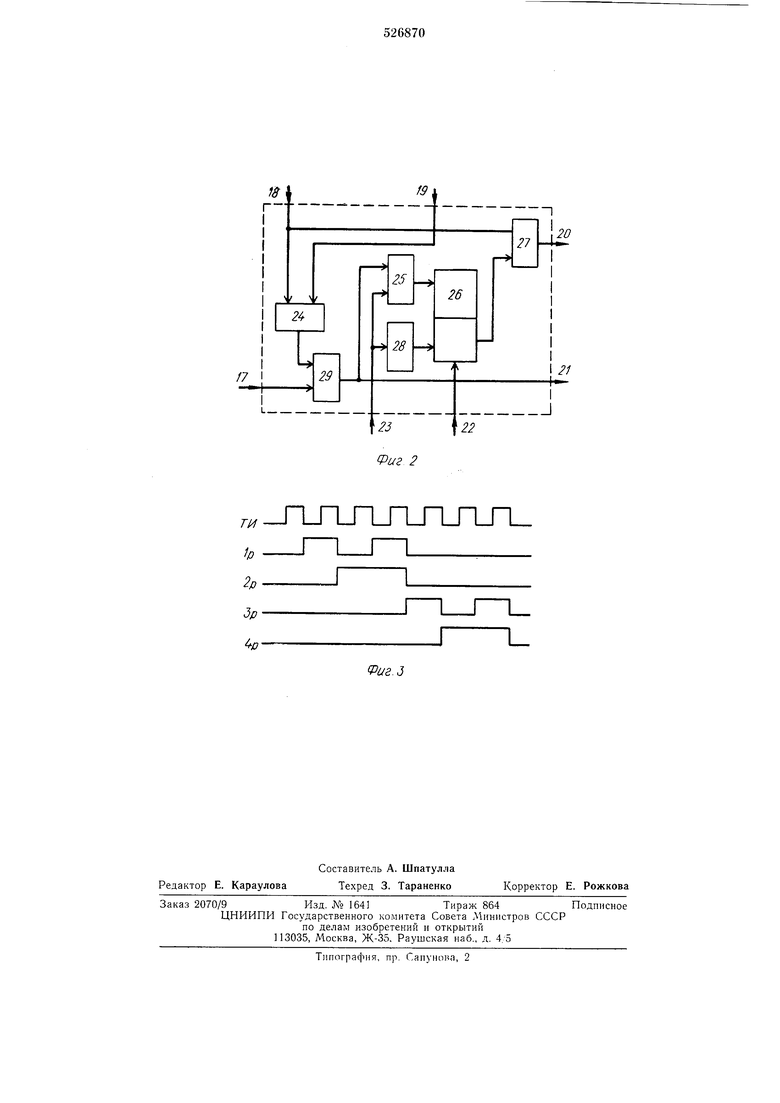

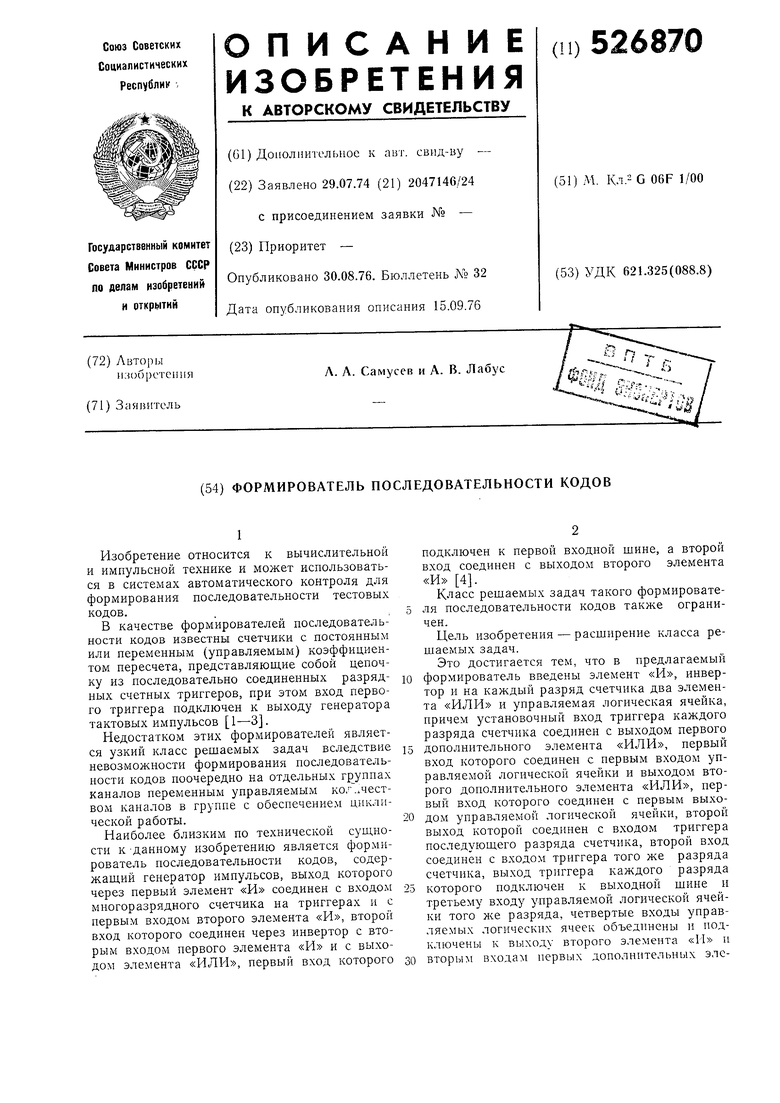

Л1СНТОВ «или, пятые входы управляемых логических ячеек в каждом разряде, кроме последнего, подключены к управляющим ши нам, а пятый вход ячейки в иоследпем разряде через инвертор подключен к шине нулевого потенциала, .1е входы вторых дополнительных элементов «ИЛИ подключены в каждом разряде, кроме последнего, соответственно к выходам аналогичных элементов в последуюа1ем разряде, второй вход второго дополнительного элемента «ИЛИ в предноеледпем разряде счетчика соединен с первым входов первого дополнительного элемента «ИЛИ и первым выходом управляемой логической ячейки последнего разряда и через дополнитель/ный элевдент «И с третьим входом элемента «ИЛИ, причем второй вход элемента «И подключен к второй входной шине. Наличие в каждом разряде формирователя дополнительных управляемых логических ячеек и элементов «И, «ИЛИ, «НЕ с указанными вьппе связями позволяет образовать из счетных триггеров многоразрядного счетчика носледовательно соединенные счетчики, каждый из которых в зависимости от управляющих сигпалов иа управляющих входах логических ячеек имеет определенное количество разрядов, причем каждый счетчик начинает повторный счет только после просчета всех счетчиков. На фиг. 1 изображена функциональная схема предлагаемого формирователя последовательности кодов; иа фиг. 2 - функциональная схема логической ячейки; на фиг. 3 - диаграмма работы формирователя последовательности кодов при установке на управляющих входах кода 010. Схемы содержат генератор 1 тактовых импульсов, первый и второй элементы «И 2 и 3, инвертор 4, элемент «ИЛИ 5, триггеры 6 многоразрядного счетчика, элементы «ИЛИ 7 и 8, управляемые логические ячейки 9, дополнительный инвертор 10, дополнительный элемент «И 11, выход 12 регистрации циклов, выходные щины 13 формирователя, первую входную щину 14, управляющие входные шины 15 формирователя, вторую входную шину 16, входы 17, 18, 19 управляемой логической ячейки 9, выходы 20 и 21 управляемой логической ячейки 9, входы 22 и 23 логической ячейки 9 элемент «ИЛИ 24, элемент «И 25, потенциальный триггер 26, элемент «ИЛИ-НЕ 27, инвертор 28, элемент совпадения 29. На фиг. 3 приняты следующие обозначения: ТИ - тактовые импульсы генератора; 1р, 2р, Зр, 4р - эпюры напряжений с выходов счетных триггеров соответственно первого, второго, третьего и четвертого разрядов. Установочный вход счетного триггера 6 соединен с выходом первого дополнительного элемента «ИЛИ 7, первый вход которого соединен с первым входом 19 управляемой логической ячейки 9 и выходом второго дополнительного элемента «ИЛИ 8, первый вход которого соединен с первым выходом 20 управляемой логической ячейки 9, второй выход которой соединен с входом триггера 6 последующего разряда формирователя, а второй вход 17 соединен с входом триггера 6 того же разряда формирователя, выход триггера 6 каждого разряда которого подключен к выходной .щине 13 (|)ормирователя и входу 18 9 того же разряда, четвертые входы 22 управляемых логических ячеек 9 объедииены и иодключены к выходу второго элемента «И 3 и вторым входам первых дополнительных элементов «ИЛИ 7, пятые входы 23 управляемых логических -ячеек 9 в каждом разряде, кроме последнего, подключены к управляющим щинам 15 формирователя, а пятый вход ячейки в последнем разряде через инвертор 10 подключен к щине нулевого потенциала, вторые входы вторых дополнительных элементов «ИЛИ 8 подключены в каждом разряде, кроме последнего, соответственно к выходам аналогичных элементов в последующем разряде, второй вход второго дополнительного элемента «ИЛИ 8 в предпоследнем разряде сче1-чика соединен с первым входом первого доиолнительиого элемента «ИЛИ 7 последнего разряда перв1)1м выходом 20 ячейки 9 иос;1едиего разряда и через дополиительный элемепт «И 11 с третьим входом элемента «ИЛИ 5, причем второй вход элемента «И подключен к второй входной шине 16. Выход генератора импульсов 1 через первый элемент «И 2 соединен с входом первого счетного триггера из цепочки последовательно соединенных счетных триггеров бис первым входом второго элемента «И 3, второй вход которого соединен через инвертор 4 с другим входом первого элемента «И 2 и с выходом элемента «ИЛИ 5, первый вход которого подключен к первой входной шине 14, а второй вход соединен с выходом второго элемента «И 3. Формирователь последовательности кодов работает следующим образом. В нерабочем состоянии на первую входную шину 14 поступает высокий уровень напряжеиия. Ири этом первый элемент «И 2 закрыт, а второй элемент «И 3 открыт. Импульсы е выхода генератора I проходят через элемент 3 и элементы 7 на установочные входы триггеров 6, переводя их в нулевое состояние. Одновременио импульсы поступают на четвертые входы 22 ячеек 9, переводя их в исходное состояние. Для запуска формирователя на шину 14 подается низкий уровень напряжения. При этом на выходе инвертора 4 устанавливается высокий уровень напряжения. Если запуск производится в момент, когда на выходе элемента 3 уже появился импульс, то элемент 2 открывается, а элемент 3 закрывается только после окончания импульса. Это объясняется тем, что импульс с выхода элемента 3 подается на вход элемента 5, обеспечивая сохранение высокого уровня на выходе элемента 5 и низкого на выходе инвертора 4 до окончания имиульса. Следующие импульсы с выхода геиератора 1 поступают через элемент 2 на вход счетного триггера 6 первого разряда и на второй вход 17 логической ячейки 9 первого разряда.

Один из входов элемента совпадения 29 (фиг. 2) является вторым входом 17 логической ячейки. При этом элемент совпадения 29 управляется электрическими сигналами, подаваемыми на второй его вход через элемент «ИЛИ 24 как с первого 19, так и с третьего 18 входов логической ячейки. Выход элемента 29 является вторым выходом 21 логической ячейки и соединен через элемент 25 с входом потенциального триггера 26.

При отсутствии управляющего сигнала на пятом входе 23 или, что то же самое, на входе инвертора 28, триггер 26 удерживается в единичном состоянии, т. е. когда на его выходе и на входе элемента «ИЛИ-НЕ 27 держится высокий уровень напряжения.

При установке на пятом входе 23 высокого уровня напряжения потенциальный триггер может перебрасываться в противоположное состояние импульсами с выхода элемента совпадения 29.

Элемент совпадения 29 исиользуется для формирования имнульса переноса в следующий разряд. При отсутствии высокого уровня напряжения на управляющих щинах триггер 26 ячеек 9 удерживается в единичном состоянии и не влияет на работу счетных триггеров 6. В этом случае формирователь последовательности кодов работает как обычный счетчик с выходами 13.

В случае, если на пятый вход 23 логической ячейки подается высокий уровень напряжения, то с появлением импульса переноса потенциальный триггер 26 перебрасывается в нулевое состояние и после окончания импульса на выходе элемента «ИЛИ-НЕ 27 или, что то же самое, на первом выходе 20 ячейки 9 появляется высокий уровень напряжения, который через вторые элементы «ИЛИ 8 подается на первый вход 19 ячеек 9 всех предыдущих разрядов и через первые элементы «ИЛИ 7 подается на установочный вход счетных триггеров всех предыдущих разрядов.

При этом в логических ячейках всех предыдущих разрядов открыт элемент совпадения 29, что обеспечивает прохождение импульсов с выхода тактового генератора на входы счетных триггеров носледующих разрядов.

Таким образом, наличие высокого уровня напряжеиия на управляющей щине или, что то же самое, на пятом входе 23 ячейки 9 такого-либо разряда позволяет счетному триггеру этого же разряда переключаться только два раза, после чего счетный триггер этого разряда, а также счетные триггеры всех разрядов удерживаются в нулевом состоянии. При этом обеспечивается переключение всех счетных триггеров последующих разрядов счетчика как в обычном счетчике.

Если на все управляющие щины 15 формирователи подать высокий уровень напряжения, то формирователь будет работать как обычный распределитель уровней.

При подаче на управляющие щины 15 определенного кода из счетных триггеров образуются последовательно соединенные счетчпки, каждый из которых имеет определенное количество разрядов, при этом каждый счетчик, начиная с первого и кончая последним, работает до заполнения, затем устана.вливается в

нуль и удерживается в этом состоянии до заполнения и установки в нуль последнего счетчика.

Для определенности рассмотрим работу формирователя последовательности кодов,

имеющего 4 выхода 13 (фиг. 1). Прп этом имеется три управляюп1,пх щипы 15. На фиг. 3 показаны эпюры напряжений па выходах 13 при установке на управляющих шинах 15 кода 010.

Из диаграммы работы формирователя впдно, что счетные триггеры первых двух разрядов работают как независимый двухразрядный счетчик до заполнения и установки В нуль, после чего они удерживаются в этом

состоянии, а счетные триггеры двух последних разрядов, в свою очередь, работают как независимый двухразрядный счетчик. На пятый вход логической ячейки последнего разряда подключением инвертора 10 все время подается высокий уровень напряжения. Это обеспечивает выключение формирователя после заверщения цикла работы. С выхода 12 поступают импульсы, лнформируюпще о КОнце Дикла. Для организацпп циклической работы

формирователя последовательности кодов первый выход 20 ячейки 9 последнего разряда подключен через элемент 11, логический элемент «ИЛИ Б к входу элемента 3 и через инвертор 4 к входу элемента 2. Для включения циклической работы формирователя ца входную щнну 14 подается высокий уровень напряжения. В конце цикла на выходе 20 ячейки 9 цоследнего разряда устанавливается высокий уровень напряжения, который через

элементы 11 и 5 открывает второй элемент 3. Первый элемент 2 при этол закрывается. Следующий импульс с выхода тактового генератора 1 поступает через элемент 3 и приводит формирователь последовательности кодов в исходное состояние. После окончания импульса элемент 2 открывается, а элемент 3 закрывается.

Техническая эффективность изобретения заключается в том, что предлагаемый формнрователь позволяет формировать последовательность кодов поочередно на отдельных группах каналов с переменным управляемым количеством каналов в группе с обеспечением циклической работы, что, в свою очередь, рас

щиряет класс решаемых задач.

Фор м у .4 а и 3 о б р е т е н и я

Формирователь последовательпостп кодов, содержапщй генератор пмпульсов, выход которого через первый элемент «И соединен с входом многоразрядного счетчика на триггерах и с нервым входом второго элемента «И, второй вход которого соединен через инвертор с вторым входом первого элемента «И и с выходом элемента «ИЛИ, первый вход которого подключен к первой входной шине, а второй вход соединен с выходом второго элемента «И, отличаюгцийся тем, что, с целью расширения класса решаемых задач, в него дополнительно введены элемент «И, инвертор и на каждый разряд счетчика два элемента «ИЛИ и управляемая логическая ячейка, причем установочный вход триггера каждого разряда счетчика соединен с выходом первого дополнительного элемента «ИЛИ, первый вход которого соединен с первым входом управляемой логической ячейки и выходом второго дополнительного элемента «ИЛИ, первый вход которого соединен с первым выходом управляемой логической ячейки, второй выход которой соединен с входом триггера последующего разряда счетчика, второй вход соединен с входом триггера того же разряда счетчика, выход триггера каждого разряда которого подключен к выходной шине и третьему входу управляемой логической ячейки того же разряда, четвертые входы управляемых логических ячеек объединены и подключены к выходу второго элемеита «И и вторым входам первых дополнительных элементов «ИЛИ, пятые входы управляемых логических ячеек в каждом разряде, кроме последнего, подключены к управляющим шинам, а пятый вход ячейки в последнем разряде через инвертор подключен к щине нулевого потенциала, вторые входы вторых дополнительных элементов «ИЛИ подключены в каждом разряде, кроме последнего, соответственно к выходам аналогичных элементов в последующем разряде, второй вход второго дополнительного элемеита «ИЛИ в предпоследнем разряде счетчика соединен с первым входом первого дополнительного элемента «ИЛИ и первым выходом управляемой логической ячейки последнего разряда и через дополнительный элемент «И с третьим входом элемента «ИЛИ, причем второй вход элемепта «И подключен к второй входной шине. Источники информации, принятые во внимание нри экспертизе: 1. И. Н. Букреем. Микроэлектронные схемы цифровых устройств. М., «Сов. радио, 1973, с. 151 - 167, рис. 5.17-3.30, 2. И. Ф. Барсуков и др. Элементы и устройства радиотелеметрических систел, М., «Энергия, 1973, стр. 182, рис. 6-10. 3.В. С. Гутников. Интегральная электроника в измерительных приборах. «Энергия,. Ленинградское отделение, 1974, с. 86, ipiHic 43. 4.Иатент США № 3716783, кл. 235-165, опубл. 1971.

| название | год | авторы | номер документа |

|---|---|---|---|

| Постоянное запоминающее устройство | 1979 |

|

SU849303A1 |

| Цифровой регистратор повторяющихся сигналов | 1987 |

|

SU1610279A1 |

| Реверсивный аналого-цифровой преобразователь | 1988 |

|

SU1612373A1 |

| Устройство для отображения информации | 1986 |

|

SU1319072A1 |

| Шифратор | 1980 |

|

SU920835A1 |

| Коммутатор | 1985 |

|

SU1265990A2 |

| УСТРОЙСТВО ДЛЯ РЕГУЛИРОВАНИЯ КОЛЕБАНИЙ | 1991 |

|

RU2024912C1 |

| Двоичный реверсивный счетчик | 1990 |

|

SU1758873A1 |

| Адаптивный формирователь импульсов | 1990 |

|

SU1750034A1 |

| Устройство для контроля электронной вычислительной машины | 1981 |

|

SU1019451A1 |

9

20

21

26

21

.J

ТИ Ь 2р Зр о

иг 2

Авторы

Даты

1976-08-30—Публикация

1974-07-29—Подача