I

Изобретение относится к области цифровой электроиздмернтельной техники и может быть использовано в цифровых измерительных приборах и системах, имеющих высокое быстродействие, большое число разрядов и малые габариты, особенно в микро- или в интегральном исиолнении.

Известны устройства для управления цифровыми Ириборами иоразрядного уравновешивания, содержащее источник синхроимпульсов, индикатор баланса, иотенциальные триггеры памяти, схемы совпадения и разделительные элементы в цепях управления триггеров памяти.

Цель изобретения - упрощение схемы и повышение быстродействия устройства без увеличения или удорожания обо1рудования.

Это достигается тем, что выход каждого триггера подсоединен к иервому входу схемы сов-падения, второй вход схемы совпадения подключен к шине тактовых имиульсов, выход через иоследовательно соединенный выпрямляюший элемент и разделительны) элемент - к входу последующего трнтгера, а через два носледовательно соединенных диода - к шине сброса синхроим1иульсов.

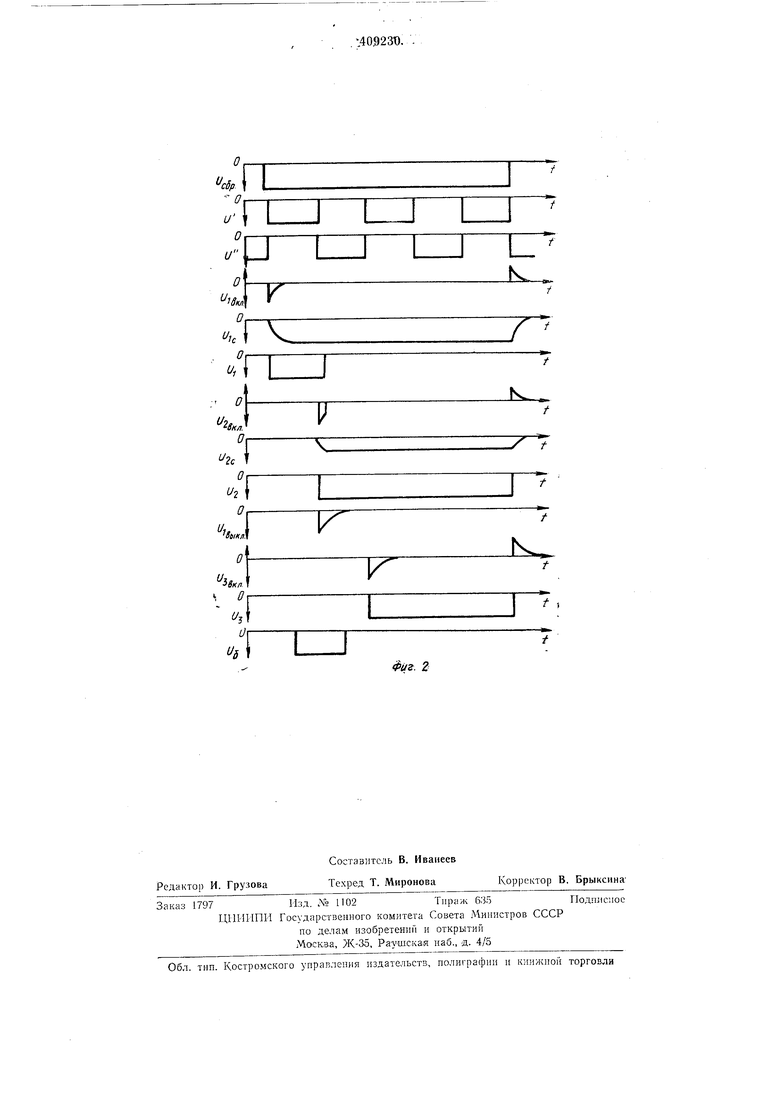

На фиг. 1 приведена упрощенная схема предлагаемого устройства на четыре разряда с изображением цепей включения триггеров памят1г при выиолнении устройства на транзисторах прямой нроводимостн (р-п-р); на фиг. 2 - временные днаграммы напряжений, ноясняющие работу устройства. Устройство содержит источник / синхроимпульсов с щинами 2 (четных) и 3 (нечетных) та.ктовых импульсов и с шиной 4 сброса, индикатор 5 баланса с выходной шииой 6, потенциальные триггеры 7 намяти, схемы 8 совпадеиия и разделительные элементы - конденсаторы 9 в цепях включення триггеров памяти.

Схемы 8 совпадения имеют два входа, один из которых, например диодный, нодсоединен к выходам триггеров намятн, а другой вход, например резисторный,-к одной из тактовых

шнн 2 нли о. Выходы схем совиадения через иос тедо вательно соединенные диод 10 и конденсатор 9 подключены к входам включения триггеров 7 иамяти. Точки соединения выпрямляющих элементов - диодов JO и конденеаторов 9 через выо1рямляюш}1е элементы - диоды // соединены с шиной 4 сброса.

Предлагаемое построение цепей включения триггеров памяти в устройстве позволяет упростить схему и новысить быстродействие

устройства при отработке кода без увеличения и удорожания обо-рудования.

Иа фиг. 1 показан один из возможных ваp:iaHTOiB построения ценей выключения триггеров иамяти на схемах 12 совпадения. Один и,-:

входоз схем совнаденш (импульсный) соедпнен с выходами триггеров 7 памяти, другом вход (потейциальаый) -с выходной шиной 6 индикатора баланса, а выходы схем сов.иадения-с входами выключения предыдущих триггеров памяти.

Ра1ботает устройство следующим образом.

В исходном положении тритгоры 7 находятся в состоянии «О - на едииичных выходах триггеров (заштрихованная половина) напряжение имеет нулевой уровень (близко к О в). Конденсаторы 9 разряжены, шина 4 сброса замкнута на землю ключом в источнике синхронМпульоов, на шине 3 нечетных тактовых импульсов - «улевой уровень напряжения, на шине 2 четных тактовых импульсов - единичный уровень напряжения.

Работа схемы разрешается при отключении шины 4 от земли и при подаче на нее единичного уровня напряжения Уобр. Первый нечетный тактовый нмпульс напряжения по шине 3 проходит через диод 10 и конденсатор 9 на вход включения первого триггера памяти, образуя напряжение включения , под воздействием которого первый триггер устанавливается в положение «1 - единичный уровень напряжения f/i на единичном выходе этого триггера. Ко1нденсатор 9 в цепи включения первого триггера заряжается (диаграмма t/ic), вследствие чего напряжение включения t/iBi.-. имеет форму продифференцированного импульса, длительность которО)го меньше длительности тактового импулыса напряжения. На входы включения других нечетных триггеров памяти первый импульс И не проходит, так как соответствующие схемы 8 совпадения не подготовлены (нулевой уровень напряжения на единичных выходах четных триггеров намяти).

По окончании первого имшульса U на шине 3, по шине 2 приходит первый четный тактовый импульс напряжения LI. В этот момент подготавлена к срабатыванию только схема совиадения в цепи включения второго трИГгера, поэтому первый импульс U проходит через схему 8 совпадения, диод 10 и конденсатор 9 на вход включения второго триггера, образуя напряжение включения .под воздействием которого второй три1ггер устанавливается в положение «1 - иашряжевие U на его единичном выходе имеет единичный уровень. Конденсатор 9 в цепи включения второго триггера заряжается (диаграмма f/2c), вследствие чего длительность имлулыса С/2Екл оказывается меньше длительности тактового импульса U. На входы включения других четных тритгеров первый импульс U не поступает, так как не подготовлены соответствующие схемы 8 совпадения. Перепад напряжения Vz с выхода второго триггера подается на схему 12 совпадения в цепи выключения первого трипгера. Если по шине 6 поступает с индикатора баланса сипнал перебаланса (единичный уровень напряжения t/e), то первый триггер сбрасывается на «О. Когда напряжение Ьб имеет нулевой уровень (недобаланс), то первый триггер остается несброшенным в связи с тем, что импульс выключения не проходит на его нулевой вход (схема 12 совпадения закрыта).

Напряжение f/z с выхода второго триг:гера подготавливает к срабатыванию схему 8 совпадения в цепи включения третьего триггера. При приходе второго нечетного импульса U по шине 3 (по окончании первого четного импульса U) перепад напряжения U проходит через схему 8 совпадения, диод 10, конденсатор 9 на вход включения третьего триггера, образуя напряжение бзок--, под воздействием которого третий триггер устанавливается в положение «1. Перепад напряжения t/з с выхо: да этого триггера поступает на схему 12 совпадения в цепи выключения второго триггера и, в случае перебаланса, сбрасывает его на «О. Аналогичным образом П|роисхО1ДИт включение последующих триггеров памяти н формирование импульсов выключения в случае перебаланса.

При этом конденсатор 9 в цепи включения каждого последующего триггера заряжается

полностью за время одного такта, если предыдущий триггер не сбрасывается на «О, или заряжается не полностью, если предыдущий триггер сбрасывается на «О. И в том и другом случае очередные тактовые импульсы И и U

не могут пройти на вход включения триггера, уже включившегося, так как в первом случае ток заряда конденсатора 9 равен нулю (заряд на конденсаторе сохраняется почти неизменным в течение времени уравновешивания), а

во втором случае не подготовлена схема 8 совпадения предыдущим триггером.

Для сохранения заряда конденсаторов во время уравновещнвання, обратные сопротивления диодов 10 и 11 должны быть достаточно

большими, в то же время прямые сопротивления диодов 10 и сопротивления цепей заряда конденсаторов должны обеспечивать заряд за время одного тактового импульса И или Ь. Эти тре1бования легко выполняются кремневыми диодами при количестве разрядов до 20.

Таким образом, достигается поочередное и однократное включение каждого триггера памяти за время одного уравновешивай и я независиэдо от кода, формируемого в триггерах,

что и необходимо при поразрядном уравновешивании.

Код, образуемый в процессе уравновешивания, может сниматыся в последо1вательном виде, например, с шины 6 индикатора баланса (о1братный код), а также в параллельном виде с триггеров памяти. В первом случае последний триггер памяти сбрасывать при перебалансе нет необходимости, во втором случае

для сброса можно использовать импульс конца измерения с источника синхроимпульсов и поставить схему 12 совпадения в цепь выключения последнего триггера. По окончании измерения триггеры памяти

устанавливаются в исходное положение «О.

Сброс триггеров можно осуществлять замыканием шины 4 сброса на землю (сигнал -сброса источника 1 синхроимпульсов), если конденсатор 9 успевает зарядиться до достаточной величины прИ выключении предыдущего разряда (при перебалансе). В этом случае конденсаторы разряжаются на входы включения триггеров памяти и устанавливают их в положение «О (положительные имлульсы {Уркл, t/2ui -i и т. д.).

Если же схема рассчитана таким образом, что заряд конденсаторов недостаточен для сброса триггеров, то необходимо поставить специальную сбросовую цепь.

По о-кончании сброса схема готова к следующему циклу уравновешивания.

ТакИМ образом, пр-именение в цепи включения каждого триггера памяти схемы совпадений с двумя входами, двух диодов и конденсатора, соединенных описанным способом, обеспечивает работу устройства при поразрядном уравновешиваиии, причем режнмы работы всех элементов не зависят от количества триггера памяти, а ампл«туда импульсов включения триггеров памяти - от количества триггеров (разрядов). Это упрощает схему, ее расчет и настройку. Количество же используемых элементов даже меньше, чем в известных схемах с последовательно соединенными цепочками схем совпадений.

При этом существенно повышается быстродействие устройства при отработке кода, так

как все конденсаторы в цепях включения триггеров памяти подготавливаются до момеита начала измерения сбросовым импульсом. В известных же устройствах каждый конденсатор Г , цепи включения каждого триггера подготав.1ивается для пропускания имнульса включения во время измерения непосредственно перед включением соответствующего разряда (триггера) и так как разряды включаются иоочередно, быстродействие ограничивается суммарным временем перезаряда всех конденсаторов. В предлагаемом устройстве этого ограичения нет, конденсаторы подготавливаются одновременно все до начала измерения.

15

Предмет изобретения

Устройство для управления цифровыми приборами поразрядного уравновешивания, содержащее источник сиихролмпульсов, индикатор баланса, триггеры, схемы совладения и разделительные элементы, отличающееся тем, что, с целью упрощения устройства и повыщения быстродействия, выход каждого триггера подключей к первому входу схемы совпадения, пторой вход которой по.дключен к шине тактовых импульсов, а выход через последовательно соединенный выпрямляющий элемент и разделительный элемент подключен к

входу последующего триггера, а через два последовательно соединенных диода соедине; с ШИНОЙ сброса синхроимпульсов.

| название | год | авторы | номер документа |

|---|---|---|---|

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ НАПРЯЖЕНИЯВ КОД | 1969 |

|

SU238909A1 |

| ЦИФРОВОЙ ВОЛЬТМЕТР | 1970 |

|

SU288138A1 |

| УПРАВЛЯЕМЫЙ ГЕНЕРАТОР ИМПУЛЬСОВ | 2003 |

|

RU2254670C1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ИМПУЛЬСОВ | 2004 |

|

RU2256288C1 |

| ПРЕОБРАЗОВАТЕЛЬ НАПРЯЖЕНИЯ В ИНТЕРВАЛ ВРЕМЕНИ | 1991 |

|

RU2032269C1 |

| Распределитель на транзисторах | 1973 |

|

SU504302A1 |

| Фазоимпульсный счетчик | 1975 |

|

SU524323A1 |

| УПРАВЛЯЕМЫЙ ФОРМИРОВАТЕЛЬ ИМПУЛЬСОВ | 2004 |

|

RU2257003C1 |

| ПРЕОБРАЗОВАТЕЛЬ ЧАСТОТЫ С АВТОНОМНЫМ ИНДУКТОРОМ | 2005 |

|

RU2291548C1 |

| Устройство для приема команд телеуправления | 1984 |

|

SU1229791A1 |

rv

Лгл

т

х

2с

/

/

:7

Авторы

Даты

1973-01-01—Публикация