Предлагаемое устройство относится к области электросвязи и используется в системах СВЯЗИ с импульсно-кодовой модуляцией (ИКМ), в частности в вычислительной технике, автоматике, телемеханике.

Известны устройства для деления и распределения .импульсов, построенные на основе регистра одвига с обратной связью (кольцевого счетчика) с использованием элементов с ПОСТОЯННОЙ памятью (например, блокинг-генераторов, ключевых усилителей с трансформаторной нагрузкой, дифференцирующих цепей к т. п.).

Однако известные устройства характеризуются малым допуском на тактовую частоту (или фазовую нестабильность тактовых импульсов), кроме того, трудно поддаются микроминиатюризации.

С целью повышения допуска на частоту следования тактовых импульсов или величину ИЗ фазовой нестабильности без снижения .помехозащищенности в предлагаемом устройстве ячейки распределителя выполнены на эл ментах с постоян-ной памятью и охвачены местной отрицательной обратной связью, задержанной на время действия Импульса тактовой частоты ДЛЯ «стирания памяти после прохождения импульса через элемент логижи, кроме того, цепь обратной связи, формирующая импульс запрета с квазипеременной

длительностью, выполнена на логических элементах «ИЛИ и «НЕТ-НЕ причем вход элемента «ИЛИ соединен с выходами всех ячеек распределителя, кроме первой и последней, а выход - с управляющим входол схемы эалрета «НЕТ-НЕ, запрещающий вход которой соединен с выходом последней ячейми распределителя, а выход - с запрещающим входом схемы запрета «НЕТ.

Таким образом, предлагаемое устройство ОТНОСИТСЯ к классу устройств, построенных )ia элементах с кв азипеременной памятью.

Отличительной особенностью таких устройств является то, что допуск на частоту

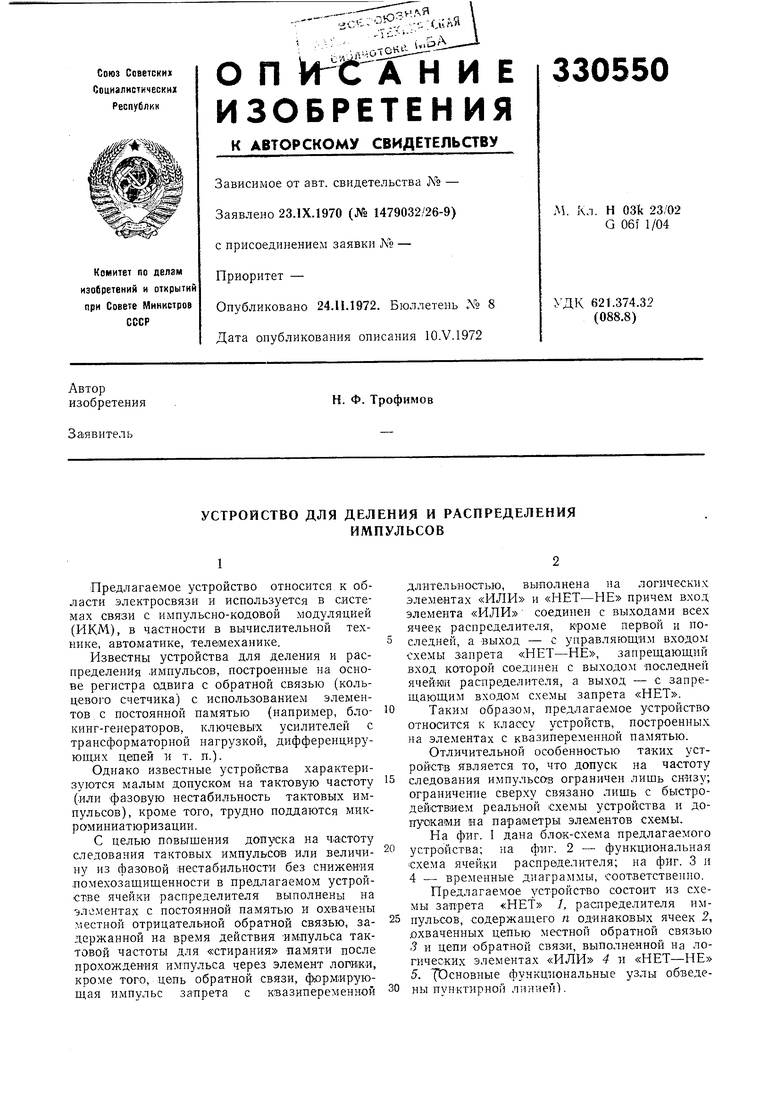

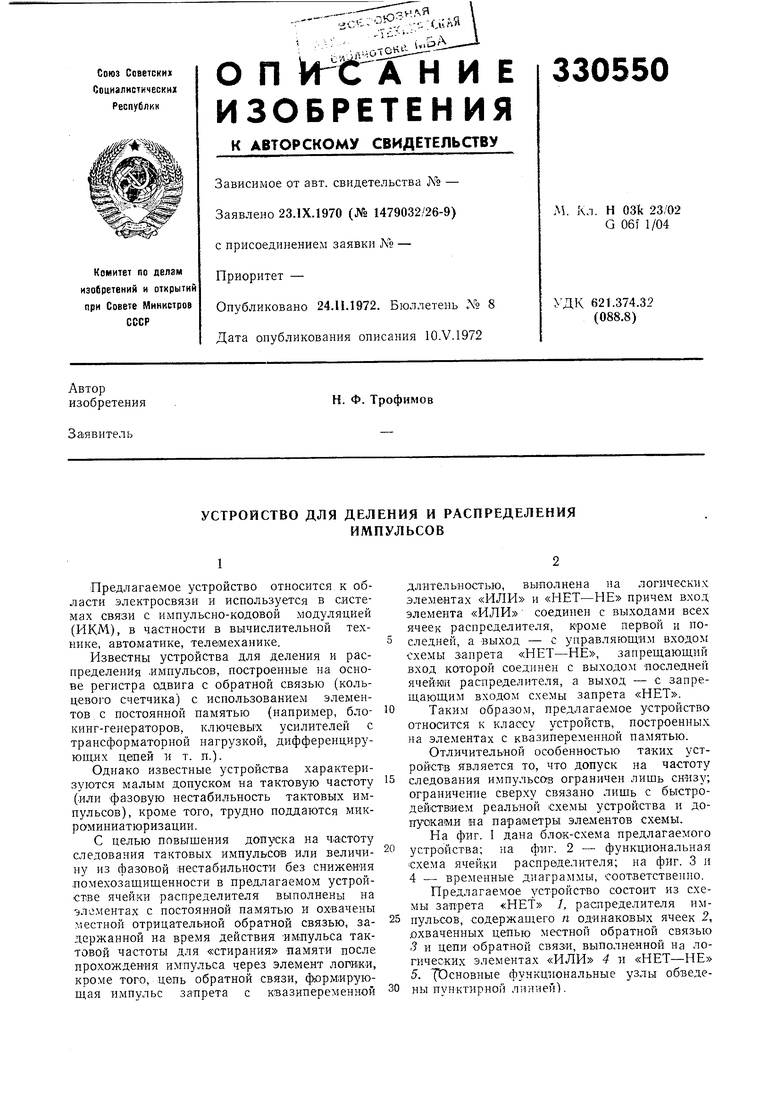

следования импульсав ограничен лишь снизу; ограничение свер.ху связано лищь с быстродействием реальной схемы устройства и допусками на параметры элел1ентов схемы. На фиг. I дана блок-схема предлагаемого

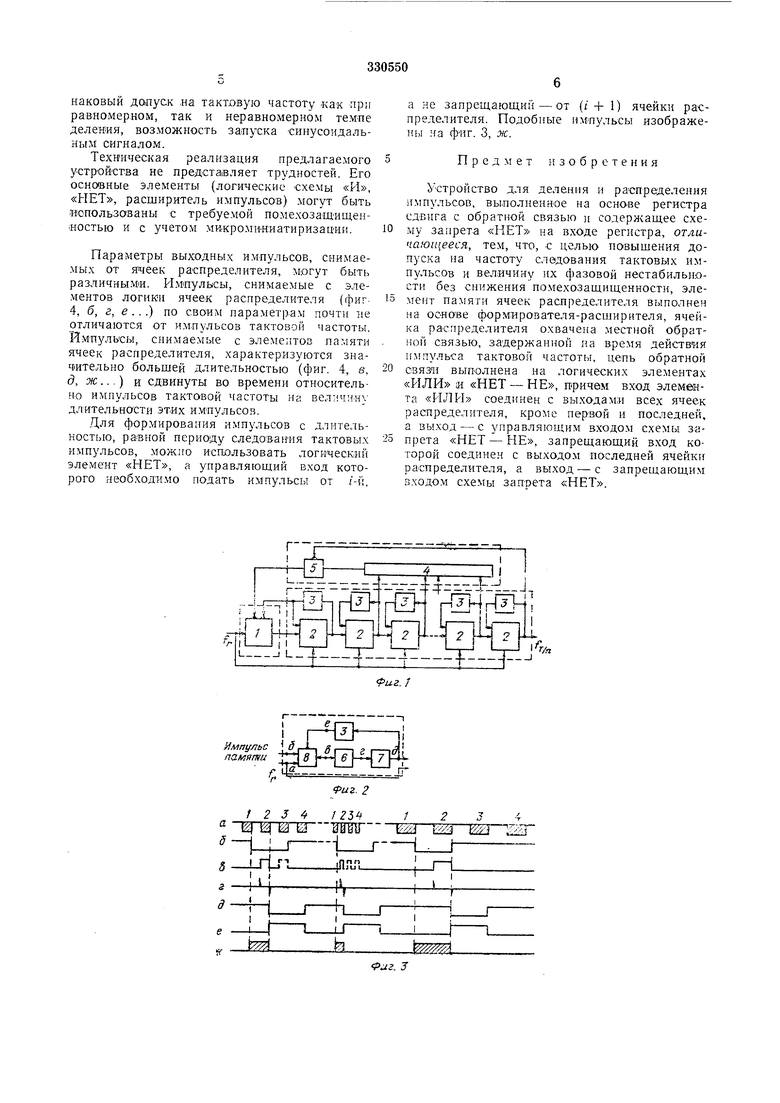

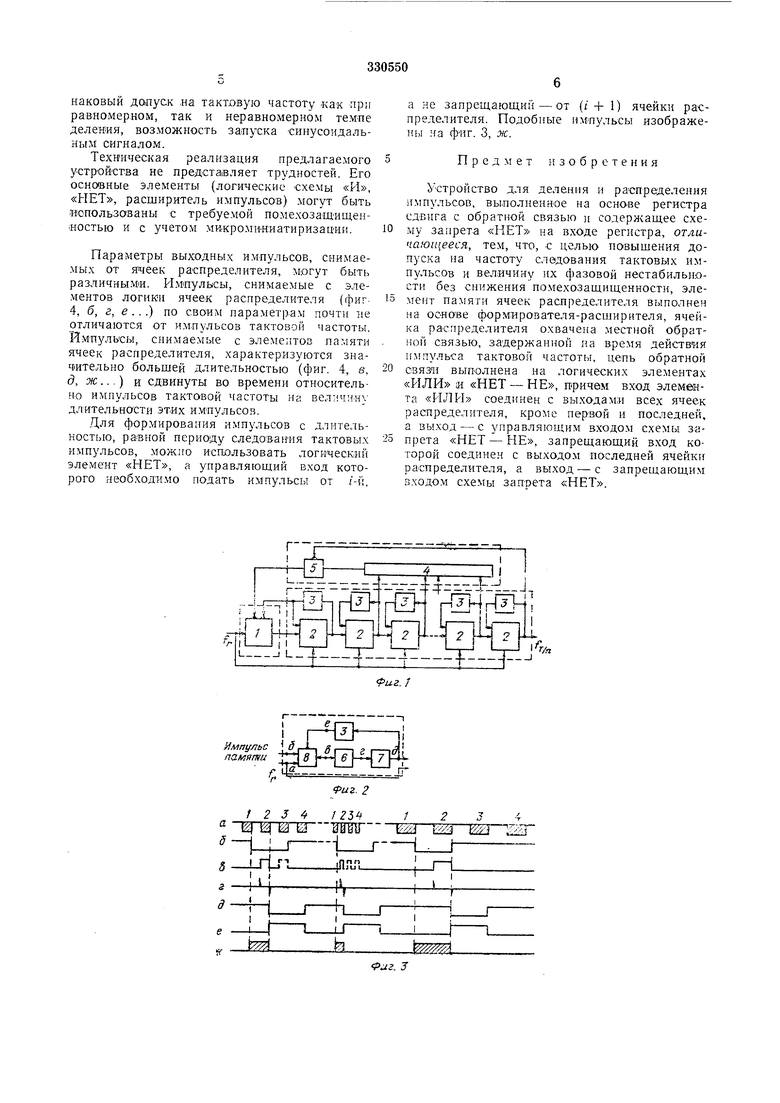

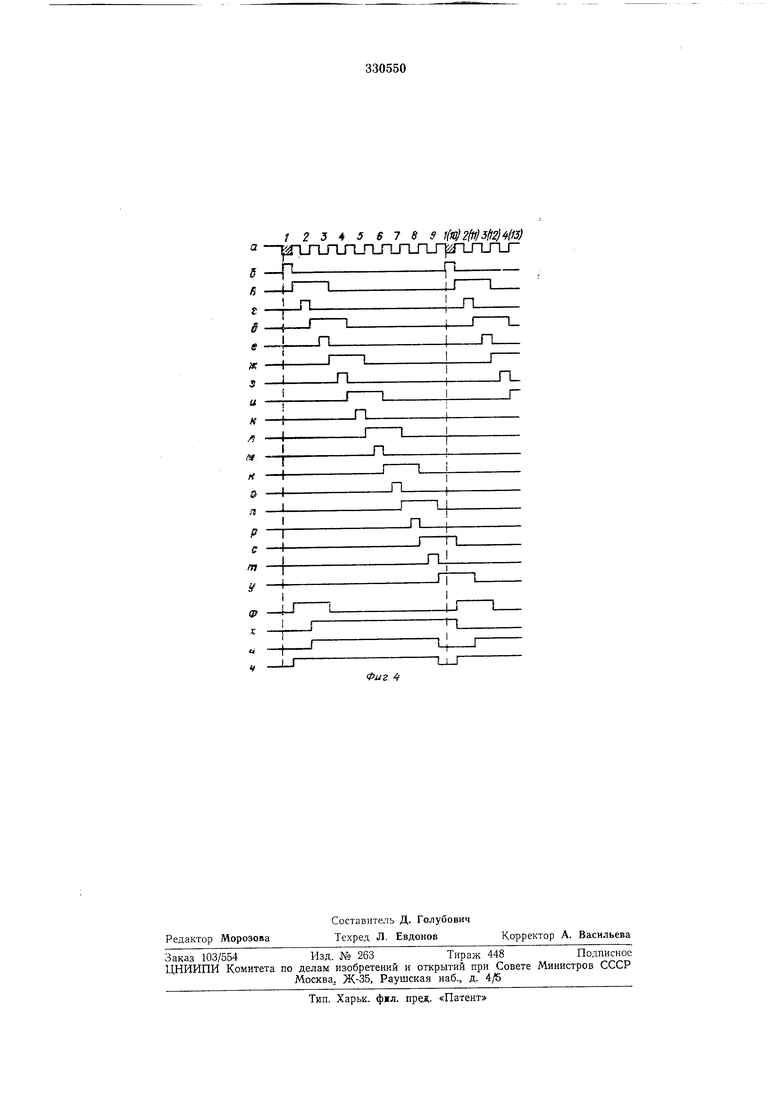

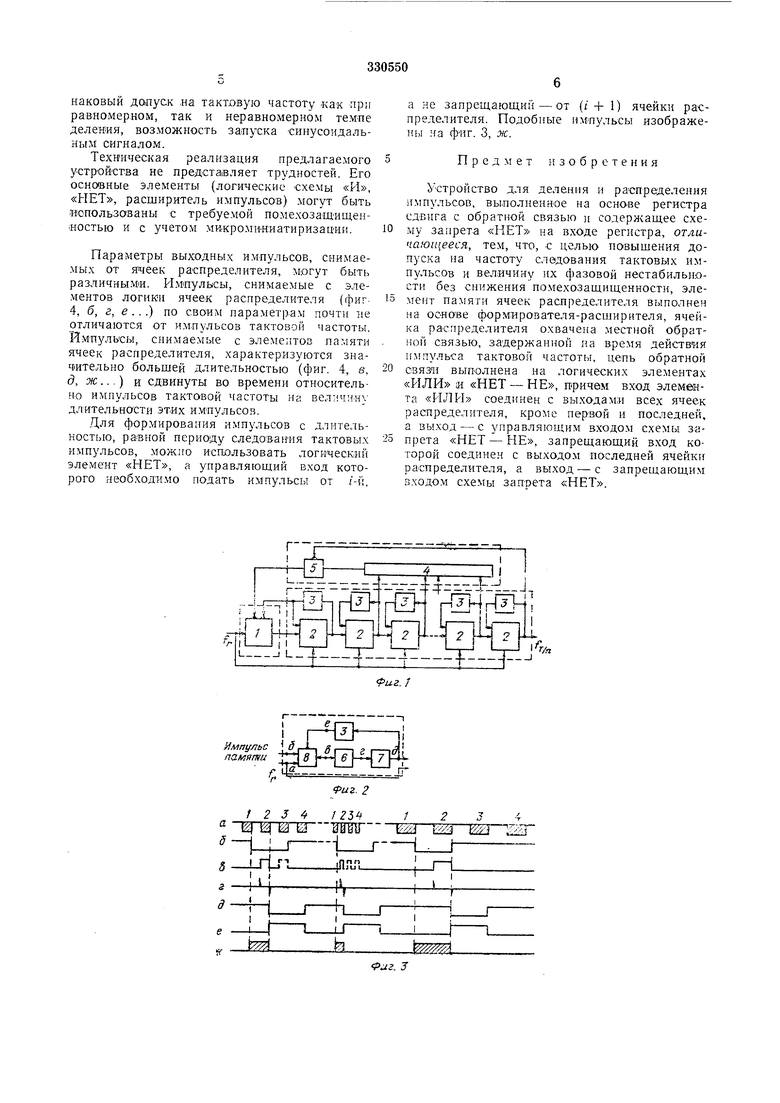

устройства; на фиг. 2 - функциональная схема ячейки распределителя; на фнг. 3 и 4 - временные диаграммы, соответственно.

Предлагаемое устройство состоит из схемы запрета «НЕТ 1, распределителя импульсов, содержап,его п одинаковых ячеек 2, охваченных цепью местной обратной связью 3 И цепи обратной связи, выполненной на логических элементах «ИЛИ 4 и «НЕТ-НЕ 5. (Основные функциональные узлы обведеЯчейка распределителя состоит из дифференцирующей цепи 6, расширителя импульсов 7 И цепи местной обратной связи 3, логического элемента «И 8, выполняющего функция элементов «И и «НЕТ.

Предлагаемое устройство работает следующим образом.

На управляющие входы элемента «И в ячейки распределителя поступают импульсы тактовой частоты (фиг. 3, а) и импульсы памяти (фиг. 3, б) предыдущей ячейки распределителя- С выхода элемента «И 8 импульсы (. 3, в), совпадающие во времени с импульса лш тактовой частоты, поступают на формирователь «Широких и.мпульсов памяти, где они вначале дифференцируются дифференцирующей цепью 6 (фиг. 3, г), а затем расширяются от заднего фронта этих импульсов расщирителем 7. «Широкие импульсы па,м:ЯТ1и (фн-г. 3, д) одновременно поступают ia вход следующей ячейки распределителя и через цепь местной обратной связи 3 на запрещающий вход элемента «И 8 этой же ячейки, в результате чего ячейка распределителя выключается по входу и запрещает прохождение импульсов тактовой частоты, которые могли бы пройти в случае отсутствия цепи местной обратной связи (на фиг. 3, в они отмечены пунктиром).

Время, в течение которого ячейка открыта по входу, строго равно величине текущего пе(иода следования тактовых им;пульсов определяет эквивалентную длительпость импульсов памяти ячейки (фиг. Зж), которая изменяется при изменении частоты следования тактовых импульсов. Нормальная работа ячейкой распределителя, следовательно, « распределителя в целом, как видно из временных диаграмм фиг. 3, обеопеч1иэается при условии, если величина текущего периода следования тактовых имлульсов не превышает длительности импульсов памят1н ячейки (фиг. 3, д), а действие местной обратной связи начинается после окончания импульса аактовой частоты.

Рассматриваемая ячейка распределителя характеризуется квазипеременной памятью и нормально функционировать при больщих пределах изменения тактовой частоты. Нижняя граничная частота следования тактовых импульсов /, определяется длительностью импульса памяти ячейки Гн//„-- i, d

и I

верхняя граничная частота определяется лищь быстродействием реальрюй схемы ячейки распределителя.

В предлагаемом устройстве цепь обратной связи обеспечивает формирование импульса запрета с автоматически изменяющейся длительностью и тем самым обеспечивает правильный процесс деления при -изменении тактовой частоты, что достигается следующим образом.

теля (временные диаграммы 4//, ж, и, л, н, п, с), кр.оме первой и последней (л-й), поступают ка схему объединения «ИЛИ 4 цепи обратной связи (фиг. ), а с ее выхода щнродай импульс запрета (фиг- 4, х) поступает на управляющий вход схе.мы «НЕТ-НЕ 5, на запрещающий вход которой поступает импульс памяти п-ой ячейки распределителя, в результате чего длительпость импульса запрета (фиг. 4, ц), поступающего на запрещающий вход схемы запрета «НЕТ 1 с выхода схемы «НЕТ-НЕ 5, строго ограничивается ио длительности. Начало этого импульса совпадает с началом импульса памяти второй ячей-ки, а конец его -- с началом импульса памяти л ячейки, т. е. с моментом окончания последнего (в цикле деления) запрещаемого импульса тактовой частоты (девятого импульса на фиг. 4, а).

Импульс запрета запрещает (п-2) импульсы тактовой частоты, начиная со второго по (п-1) включительно. Первый же запрещаемый импульс тактовой частоты (на фиг. 4, а - второй по счету) запрещается

другим импульсом запрета (фиг. 4, ф). поступающим с выхода первой ячейки распределителя через цепь местной обратной свяЗИ на другой запрещающий вход схемы запрета «НЕТ /. В результате действия двух

импульсов запрета (фиг. 4, ц и 4, ф запрещаются строго определенные (я - 1) импульсы тактовой частотьг. Эквивалентный (суммарный) импульс запрета изображен на фиг. 4,ч, где йидно, что начало импульса запрета

«привязано к моменту окончания проходного импульса тактовой частоты, а конец его - к моменту окончания последнего запрещаемого импульса тактовой частоты, поэтому при изменении тактовой частоты (или фазы тактовых импульсов) соответственно изменяется положение начала и конца и, следовательно, длительность импульса запрета.

TaiMMM образом, цепь обратной свяЗИ обеспечивает формирование импульса запрета с

переменной длительностью, определяемую текуЩИм периодом следования импульсов тактовой частоты.

Предлагаемое устройство для деления и распределения импульсов может функционировать при больщих пределах изменения частоты следо1вания тактовых импульсов (или фазы тактовых импульсов).

Допуск на величину тактовой частоты ограничен лишь снизу и определяется величиной длительности импульса памяти ячеек

распределителя i З,- - 1 ), где Т„ -дли т /

тельность импульса памяти, Тт -период следования тактовых импульсов) и, не зависит

от коэффициента деления.

наковый допуск ,на тактовую частоту -как при равномер.ном, так и неравномерном темпе деления, возможность запуска синусоидальным сигналом.

Техническая реализация нредлагаемого устройства не представляет трудностей. Его основные элементы (логические схемы «И, «НЕТ, расширитель импульсов) .могут быть использованы с требуе.мой поме.хозаЩИщен«остью и с учетом микроминиатиризации.

Пара.метры выходных и.мпульсов, снимаемых от ячеек распределителя, могут быть различными. И.мпульсы, снимаемые с эле.ментов логик и ячеек распределителя (фиг4, б, г, е .. .} по своил: параметр.а.м почти не отличаются от и.млульсов тактовой частоты. Й.мпульсы, снимаемые с элементов памяти ячеек распределителя, характеризуются значительно большей длительностью (фиг. 4, в, д, ж...) и сдвинуты во времени относительно и.мпульсов тактовой частоты на величннчдлительности этих импульсов.

Для фор.мирования импульсов с длительностью, ра-вной периоду следования тактовых импульсов, можно использовать логический элемент «НЕТ, а управляюш;ий вход которого необходи.мо подать импульсы от ;-(;.

а не запрещающий - от (i + 1) ячейки распределителя. Подобные им пульсы изображеи 1 на фиг. 3, ж.

Пред.мет изобретения

Устройство для деления и распределения и.мпульсов, вылолненное на основе регистра сдвига с обратной связью и содержащее схе.му запрета «НЕТ на входе регистра, отличаюиееся, тем, что, с целью повышения допуска на частоту следования тактовых импульсов и величину их фазовой нестабильности без снижения помехозащищенности, элемемт памяти ячеек распределителя выполнен на основе формирователя-расширителя, ячейка распределителя охвачена .местной обратной связью, задержанной на время действия импульса тактовой частоты, цепь обратной

связи выполнена на логических элементах «РШИ 1И «НЕТ - НЕ, П1ричем вход элемента «ИЛИ соединен с выходами всех ячеек распределителя, кроме первой и последней, а вы.ход - с управляющим входом схемы запрета «НЕТ - НЕ, запрещающий вход которой соединен с выходом последней ячейки распределителя, а выход - с запрещающим входом схемы запрета «НЕТ.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО КОММУТАЦИИ ТЕЛЕГРАФНЫХ КАНАЛОВ | 1970 |

|

SU270804A1 |

| УСТРОЙСТВО КОММУТАЦИИ ТЕЛЕГРАФНЫХ КАНАЛОВ | 1971 |

|

SU320075A1 |

| Селектор-преобразователь импульсных сигналов | 1981 |

|

SU966879A1 |

| Устройство фазовой автоподстройки частоты | 1991 |

|

SU1811020A1 |

| Устройство фазовой автоподстройки частоты | 1991 |

|

SU1826135A1 |

| Устройство синхронизации | 1988 |

|

SU1644398A1 |

| РАСПРЕДЕЛИТЕЛЬ ИМПУЛЬСОВ | 1971 |

|

SU306564A1 |

| УСТРОЙСТВО ЦИКЛИЧЕСКОЙ, СИНХРОННОЙ, с ВРЕМЕННЫМ | 1970 |

|

SU277009A1 |

| АНАЛИЗАТОР ДЛЯ ОПРЕДЕЛЕНИЯ УСТОЙЧИВОСТИ ФАЗИРУЮЩИХ УСТРОЙСТВ С ДИСКРЕТНЫМ УПРАВЛЕНИЕМ | 1968 |

|

SU211151A1 |

| УСТРОЙСТВО для СЕЛЕКЦИИ КАНАЛОВ СВЯЗИ | 1970 |

|

SU265978A1 |

fuz. 2

/ 2 J 2

°- Щ ЩЖШ 1ШиЕШ Ш д

1234567

« -I TJTJlJTJljnjlJTr nJTriJ

5 flП

9 l()Sfl2)4ilS)

Авторы

Даты

1972-01-01—Публикация