Изобретение относится к вычислительной технике и предназначено для вычисления авто- и взаимных корреляционных функций.

Известный многоканальный коррелятор содержит цифровую линию задержки и умножитель, через ключи соединенный с интеграторами.

Недостатком известного коррелятора является то, что при работе в режиме коррелированной выборки верхний частотный диапазон его входных сигналов ограничен числом одновременно вычисляемых точек корреляционной функции, т. е. числом каналов. В этом случае за шаг временной дискретизации входного сигнала необходимо производить число умножений, равное числу точек корреляционной функции и такое же число шагов распределения произведений по интеграторам.

Целью изобретения является увеличение верхнего частотного диапазона входных сигналов.

Предложенный многоканальный коррелятор отличается от известного тем, что содержит генератор чисел, соединенный с устройством умножения и со схемами эквивалентности, а выходы схем эквивалентности соединены с управляющими входами ключей.

достигается за счет того, что устройство умножения за время между двумя соседними отсчетами входного сигнала совершает число умножений, равное числу уровней квантования одного из сигналов, которое практически всегда меньше числа каналов.

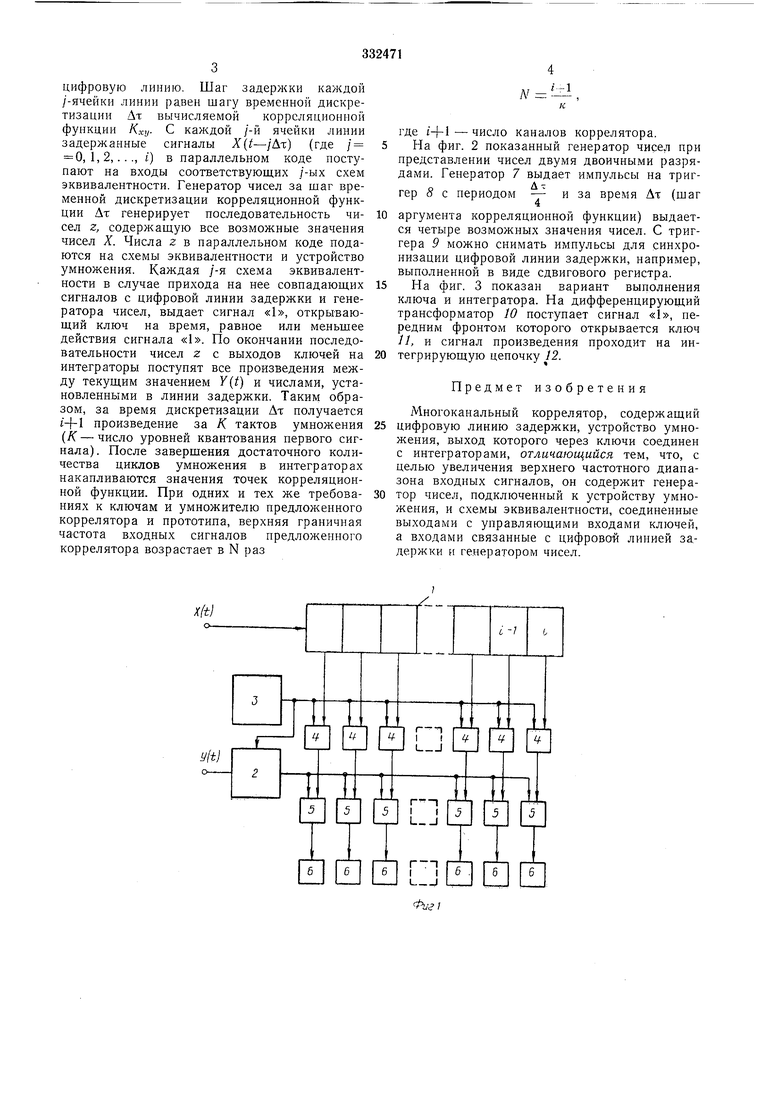

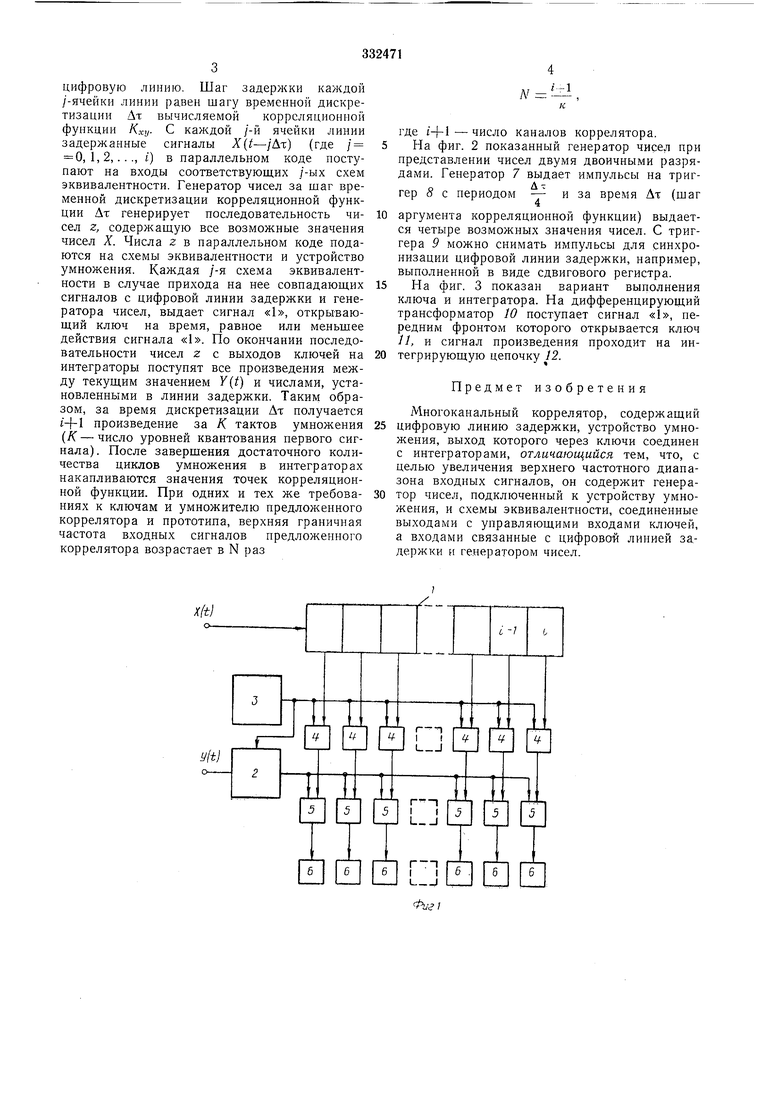

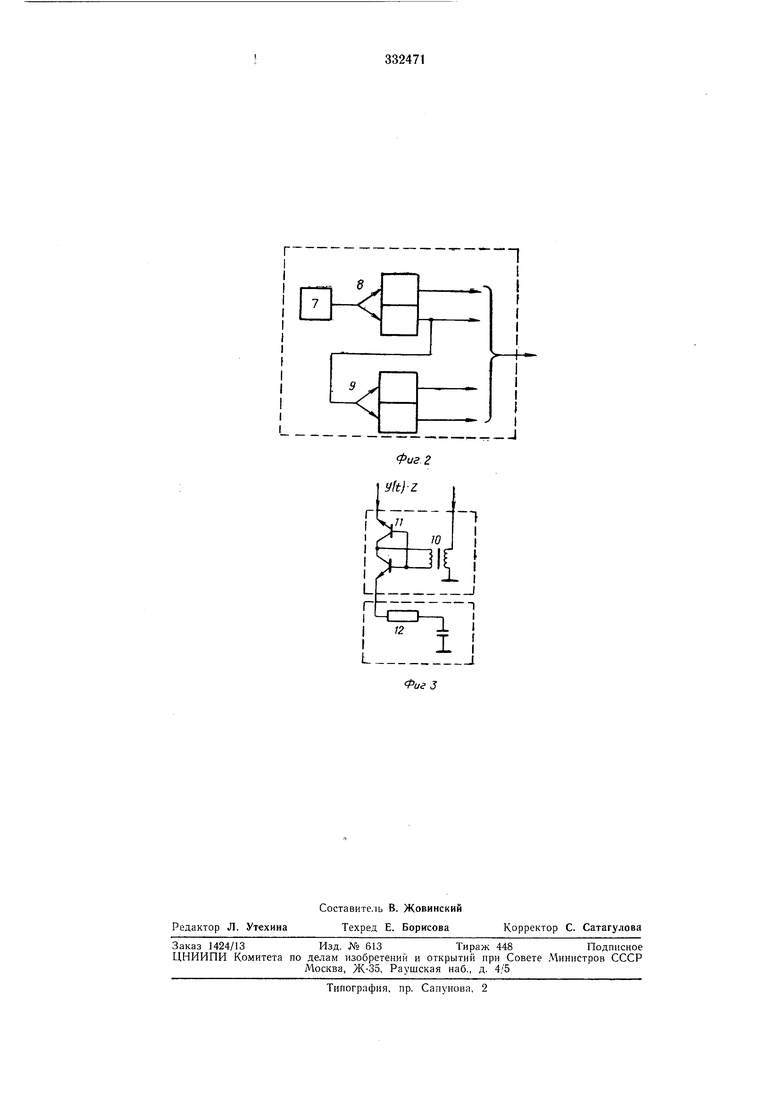

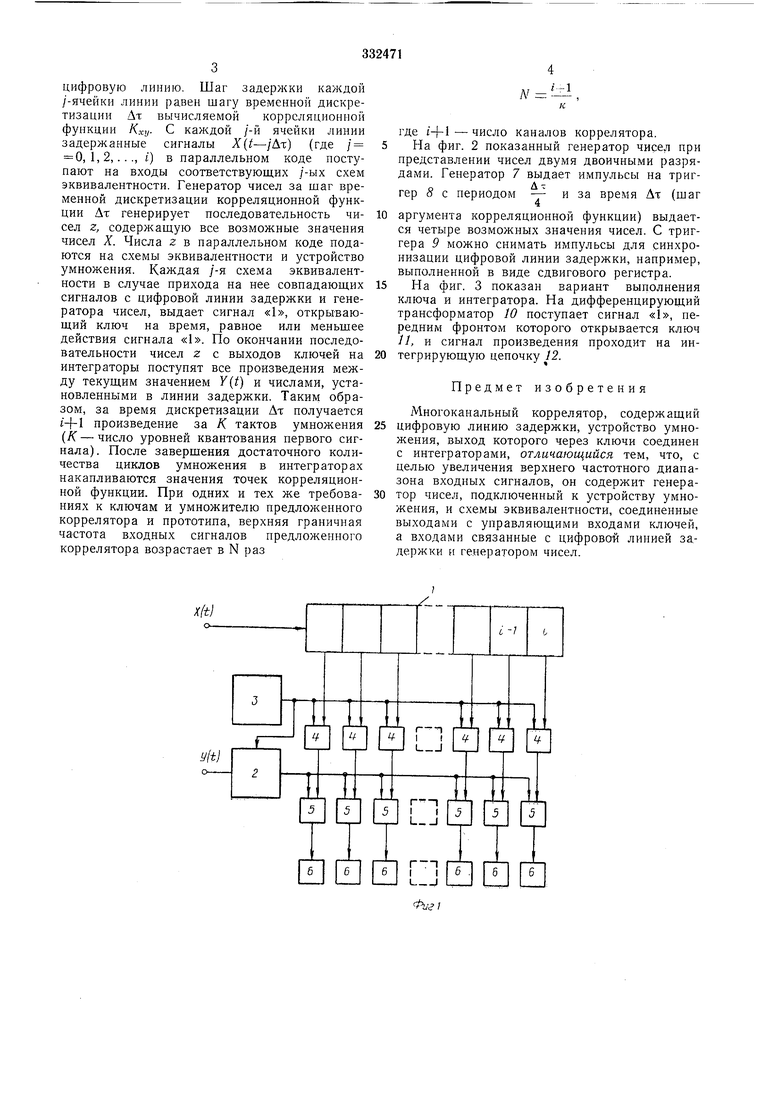

На фиг. 1 дана обшая структурная схема предложенного коррелятора; на фиг. 2 - вариант выполнепия генератора чисел; на

фиг. 3 - вариант выполнения ключа и интегратора.

Коррелятор содержит цифровую линию задержки 1, например, выполненную на основе сдвигающего регистра, устройство умножения 2, соединенное с генератором чисел 5. Входы схем эквивалентности 4 соединены с генератором чисел и соответствующими ячейками линии /. Через управляемые входы ключей 5 интеграторы 6 соединены с выходом устройства умножения. Управляющие входы ключей соединены с выходами соответствующих схем эквивалентности.

Наиболее целесообразен режим работы предложенного коррелятора по алгоритму

Стилтьеса: первый сигнал квантован на небольшое число уровней, но больше двух; второй сигнал аналоговый. Первый сигнал, заранее преобразованный, например, аналогоцифровым преобразователем в дискретный

цифровую линию. Шаг задержки каждой /-ячейки линии равен шагу временной дискретизации Дт вычисляемой корреляционной функции Кху- С /-и ячейки линии задержанные сигналы X(t-/Лт) (где / 0,1,2,..., i) в параллельном коде поступают на входы соответствующих /-ых схем эквивалентности. Генератор чисел за шаг временной дискретизации корреляционной функции Дт генерирует последовательность чисел Z, содерл ащую все возможные значения чисел X. Числа z в параллельном коде подаются на схемы эквивалентности и устройство умножения. Каждая /-я схема эквивалентности в случае прихода на нее совпадающих сигналов с цифровой линии задержки и генератора чисел, выдает сигнал «1, открывающий ключ на время, равное или меньшее действия сигнала «1. По окончании последовательности чисел z с выходов ключей на интеграторы поступят все произведения между текущим значением К (О и числами, установленными в линии задержки. Таким образом, за время дискретизации Дт получается 1+1 произведение за К. тактов умножения (К-число уровней квантования первого сигнала) . После завершения достаточного количества циклов умножения в интеграторах накапливаются значения точек корреляционной функции. При одних и тех же требованиях к ключам и умножителю предложенного коррелятора и прототипа, верхняя граничная частота входных сигналов предложенного коррелятора возрастает в N раз

Л, к

где г+1 - число каналов коррелятора. На фиг. 2 показанный генератор чисел при представлении чисел двумя двоичными разрядами. Генератор 7 выдает импульсы на триггер 8 с периодом --- и за время Дт (шаг

аргумента корреляционной функции) выдается четыре возможных значения чисел. С триггера 9 можно снимать импульсы для синхронизации цифровой линии задержки, например, выполненной в виде сдвигового регистра.

На фиг. 3 показан вариант выполнения ключа и интегратора. На дифференцирующий трансформатор 10 поступает сигнал «1, передним фронтом которого открывается ключ 11, и сигнал произведения проходит на интегрирующую цепочку 12.

Предмет изобретения

Многоканальный коррелятор, содержащий цифровую линию задержки, устройство умножения, выход которого через ключи соединен с интеграторами, отличающийся тем, что, с целью увеличения верхнего частотного диапазона входных сигналов, он содержит генератор чисел, подключенный к устройству умножения, и схемы эквивалентности, соединенные выходами с управляющими входами ключей, а входами связанные с цифровой линией задержки и генератором чисел.

| название | год | авторы | номер документа |

|---|---|---|---|

| МНОГОКАНАЛЬНЫЙ КОРРЕЛЯТОР | 1973 |

|

SU408338A1 |

| Цифровой коррелятор | 1976 |

|

SU636619A1 |

| Коррелятор | 1975 |

|

SU525119A1 |

| Время-импульсный анализаторСигНАлА | 1979 |

|

SU817725A1 |

| Многоканальный коррелятор | 1979 |

|

SU832563A1 |

| Коррелятор | 1982 |

|

SU1042030A1 |

| Цифровой автокоррелятор | 1983 |

|

SU1149277A1 |

| Цифровой коррелятор | 1980 |

|

SU903892A1 |

| Коррелятор | 1972 |

|

SU447717A1 |

| Коррелометр | 1982 |

|

SU1026144A1 |

Даты

1972-01-01—Публикация