(54) ЦИФРОВОЙ КОРРЕЛЯТОР

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой коррелятор | 1980 |

|

SU900289A1 |

| Цифровой коррелятор | 1982 |

|

SU1073776A1 |

| Цифровой коррелятор | 1980 |

|

SU940172A1 |

| Цифровой коррелятор для обнаружения эхо-сигналов | 1980 |

|

SU959091A1 |

| Цифровой коррелятор для обнаружения эхосигналов | 1979 |

|

SU879595A1 |

| Цифровой фильтр | 1980 |

|

SU904201A1 |

| Устройство для определения взаимной корреляционной функции | 1990 |

|

SU1751779A1 |

| Цифровой коррелятор | 1986 |

|

SU1336031A1 |

| Многоканальный многомерныйцифРОВОй КОРРЕлОМЕТР | 1978 |

|

SU809199A1 |

| Цифровой фильтр | 1980 |

|

SU919054A1 |

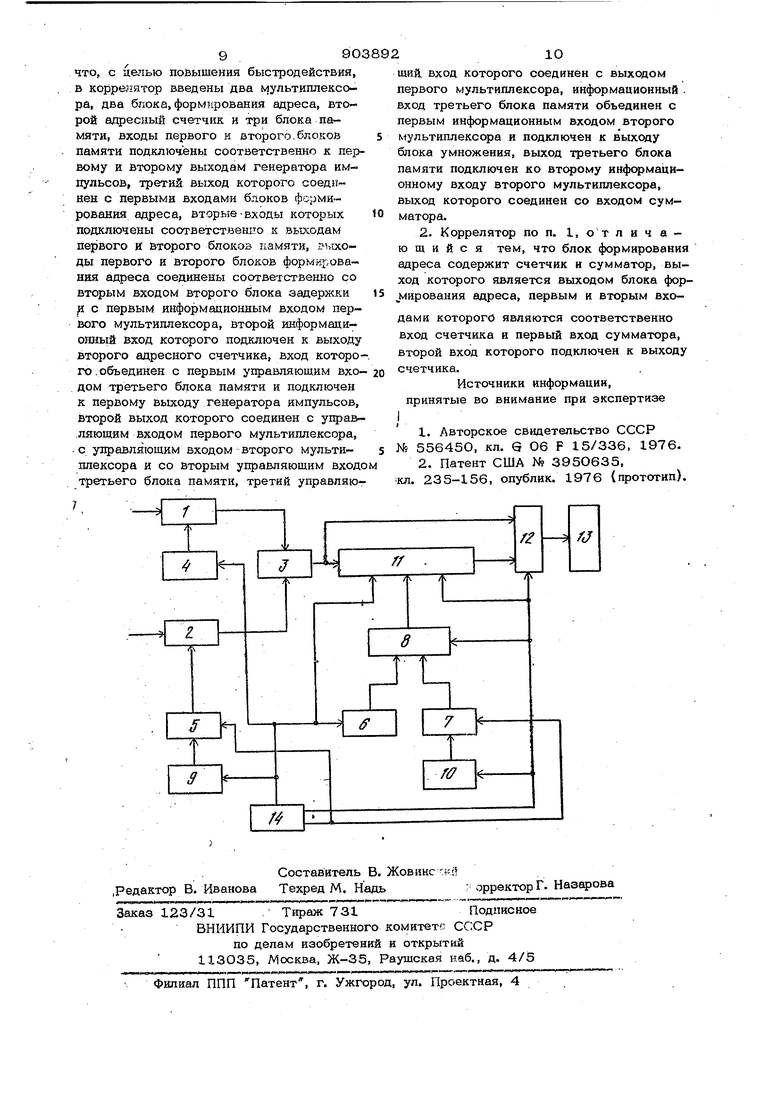

Изобретение относится к .вычислитель кой технике и предназначено для взаимокорреляционной обработки эхосигналов. Измерение взаимной корреляционной функции (ЕЖФ) между входным и сигналами в реальном масштабе времени требует обработки всего массива N выборок (определяемого длительностью сигнала и точностными параметрам измерения) за время между двумя соседними выборками, поступающими на вход коррелятора. N выборок входного сигнала и М выборок опорного сигнала попарно ( N пар выборок) поступают на умножитель, где перемножаются, а результат поступает в накапливающий сумматор, который усредняет результат перемножения на интервале длительности сигнала ( N пар выборок). Таким образом, при большом количестве N и малом интервале между входными выборками возникает -сложност Ц)актической реализации цифровых корреляторов, работающих в реальном масштабе времени. Быстродействие коррелятора определяется в основном быстродействием умножителя, как наиболее сложного и трудоемкого узла. С целью увеличения быстродействия, как правило, используют щшн- цип параллельного подключения нескольких умножителей, что позволяет увеличить быстродействие, но ведет к увеличению аппаратурных затрат, потребляемой мощности и, как следствие этого, понижает надежность коррелятора, сокращает .область применения. В современных трактах обработки сигнашов, где одновременно во многих щ остранственных и частотных каналах ведется обработка сигналов, остро встает вопрос реализации быстродействующего малогабаритного коррелятора. Известен многоканальный коррелятор, содержащий цифровую линию задержки, цифровые блоки умножения, дешифраторы, коммутаторы, и интеграторы. С целью по3903вышения быстродействия цифровые, блоки , умножения умножают один отсчет вход -, ного сигнала на коды, равные уровням квантования другого опорного сигнала. Коррелятор позволит одновременно вычислять несколько значений ординат ВКФ и при этом, чем больше ординат он вычисляет одновременно, тем эффективнее его работа 1 . Однако в системах обнаружения сигналов (неизвестно время прихода отраженного сигнала) использование такого коррелятора неэффективно, так как там требуемся последовательное непрерывное вычисление одинат ВКФ, соответствующих определенным моментам времени. Использование одного канала такого коррелятора приводит к избыточности аппаратуры. Наиболее близким к предлагаемому по технической сущности является цифро вой коррелятор содержащий два цифровых устройствазадержки с памятью, генератор импульсов, адресный счетчик, соединенный с адресными Входами устройств задержки с памятью, выходы которых соединены со входами умножителя, к выходу которого подключен сумматор. Работа коррелятора осуществляется следующим образом. . Выборки входного сигнала последовательно поступают в устройства задержки с памятью, гре хранятся N текущих зна чений выборок входного сигнала,, в друго устройство задержки с памятью последовательно поступают N выборок опорного .сигнала (запись опорных выборок обычно. осуществляется в момент излучения зондирующего сигнала). Вычислени ординаты ВКФ между входным и опорным сигналом осуществляется путег полного образования N пар выборок за время между двумя соседними выборками входного сигнала. Дальнейшее вычисление .ВКФ в умнож теле и сумматоре производится традиционными методами перемножения выборок, составляющих пары и усреднения результ тов перемножения за время между двумя выборками, поступающими на вход коррелятора. Очередная входная выборка, по:отупающая в память, стирает рамую ст рую по времени прихода в память выбор ку и цикл .вычисления очередной ординаты ь ВКФ повторяется. Адресный счетчик посл довательно формирует адреса обращения IK N ячейкам памяти каж51ого устройства (Задержки с памятью С 23. Недостатком такого коррелятора являтся то, что использование его в трактах , бработки сигналов, работающих в реальом масщтабе времени, ограничивается ыстродействием умножителя (как наиолее сложного и трудоемкого узла). Па аллелизация операции умножения ведет значительному увеличению аппаратурных атрат, что при больщом числе каналов тракте обработки не всегда приемлемо. Цель изобретения - повышение быстроействия цифрового коррелятора при отноительно незначительном увеличении аппаатуры. При малой разрядности выборок порного сигнала и большой длине реализаии N в оперном сигнале будут присуттвов ать выборки равные по значению. В силу этого при вычислении различных ординат ВКФ по алгоритму Rxntu.Ar ;J-|: хат уат-илГ), где х( iT), у( ,1Т-кдГ) - цифровые отсчеты сигналов х и у в моменты 1т и гТ - кД соответственно;N - число выборок процесса; дГ - шаг задержки процесса; Т - интервал дискретизации; К - отсчет ординаты корреляционной функции, имеет место повторяемость одинаковых результатов умножения, моменты появления которых определяет структура де терминированного опорного сигнала. Сущность изобретения заключается в том, что обеспечивается возможность использований промежуточных значений парныхшроизведений, полученных при вычислении одной ординаты ВКФ при вычислении последующих ее ординат. Таким образом, сокращается время на вычисление, что приводит к увеличению быстродействия. Поставленная цель достигается тем, что в цифровой коррелятор, содержащий сумматор, два блока задержки, входы которых являются соответственно первым и вторым входами коррелятора, а выходы подключены соответственно к му и второму входам блока умножения управляющий вход первого блока задержки соединен с выходом первого адресного счетчика, вход которого соединен с первым выходом генератора импульсов, введены два мультиплексора, два блока формирования адреса, второй адресный счетчик и три блока памяти, входы перво го и второго блоков памяти подключены соответственно к первому и второму выходам генератора импульсов, третий выход которого соединен с первыми входами блоков формирования адреса, вторые входы которых подключены соответственн к выходам первого и второго блоков памяти, выходы первого и второго блоков формирования адреса соединены соответственно со вторым входом второго блока задержки и с первым информационным входом первого мультиплексора, второй информационный вход которого подключен к выходу второго адресного счетчика, вход которого объединен с первым управляющим входом третьего блока памяти и подключен к первому выходу генерато- ра импульсов, второй выход которого сое динен с управляющим входом первого мультиплексора, с управляющим входом вт рого мультиплексора и со вторым угфав- ляющим входом третьего блока памяти, третий управляющий вход которого соединен с выходом первого мультиплексора, информационный вход третьего блока памяти объединен с первым информационны входом второго мультиплексора и подклю чен к выходу блока умножения, выход третьего блока памяти подклврчен ко второму инффмационному входу BTqporo муль типлексора, выход которого соединен со входом сумматора. Кроме того, блок формирования адреса содержит и сумматор, выход которого является выходом блока формирования адреса, первым и вторым входами которого являются соответственно вход счетчика и первый вход сумматора, второй вход которого подключен к выходу счетчика, На чертеже представлена структурная схема предлагаемого коррелятора. и. коррелятор содержит два блока 1 и 2 задержки, (с памятью), выходы которых соединены со входами блока 3 умножения, а адресные входы - с .выходами адресного счетчика 4 и блока 5 формирования адресов соответственно, адресный счетчик 6 и блок 7 формирования адресов своими выходами соединены с информационными входами мультиплексора 8, первые входы блоков 5 и 7 формирования адресов соединены с выходами блоков 9 и 10 памяти соответственно выход блока 3 умножения соединен с информационным входом блока И памяти щзомежуточных произведений (БППП), ВЫХОД которого соединен через второй мультиплексор 12 с входом сумматора 13, второй информационный вход второго, мультиплексора 12 соединен с выходом блока 3 умножения, первый выход генератора 14 импульсов соединен с входами адресных счетчиков 4 и 6, входом блока 9 памяти и входом Запись блока 11 Второй выход генератора 14 импульсов соединен с входом 10 блока памяти, с управляющимивходами мультиплексоров 8 и 12 и входом,Считывание БППП 11 третий выход генератора 14 импульсов соединен с вторыми вг одами блоков 5 и 7 формирования адреса. Работа цифрового коррелятора происходит следующим образом. Каждая выборка входного сигнала записывается в память блока 2, где хранится в течение N циклов вычисления ВКФ, т.е. всегда в памяти блока 2 хранится N выборок входного сигнала. В памятв блока 1 хранится Q выборок опорного сигнала, отличающихся друг от друга до своему значению. При вычислении каждой ординаты ВКФ с помощью а/фесного счетчика 4 последовательно осуществляется опрос (3 ячеек памяти блока I (в каждом цикле опрос начинается с первой ячейки). Синхронно с опросом ячеек памяти блока 1 огфашивается Q из N ячеек памяти блока 2 с помощью блока 5 формирования адресов, формирующего коды адресов ячеек, содержание которых в данном цикле должно быть перемножено с содержанием соответствующих им ячеек в памяти блока 1, т.е. на каждую из Q выборок опорного сигнала умножается только та входная выборка из N , которая для данного цикла соответствует значению опорной выборки и имеет минимальную задержку в блоке 2. Полученное ири. вычислении данной ординаты ВКФ парное .произведение X (iT) yli Т) используется (путем предварительной записи и последующего считывания из блока 11) прк вычислении ординаты ВКФ через оС цик лов при выполнении условия ) ijCU- -(.)T3jX.e. когда входная выборка xt.i т) снова должна быть умножена на то же значение опорнбй выборки. В каждом последующем цикле опрос памяти блока 2 осуществляется с ячеек, код адреса которых на единицу 1февыщ(ает код адреса ячеек, опрашиваемых в 1федьздуЩем цикле. Таким образом, из памяти блока 2 в каждом цикле извлекаются 790 d выборок, что обеспечивается поступпь нием Q кодов из блоке 9 памяти на блок 5 формирования адреса, который в свою очередь формирует .кодов адресов ячеек, с которых происходит считывание в данном цикле Изменение адресов ячеек памяти блока 2 от цикла к циклу осуществляется блоком 5 формирова.чня адреса путем суммирования по модулю . кода определяемого номером цикла с кодом,выдаваемым блоком 9 памяти. Q соответствующих выборок из обоих блоков I и 2 поступают в блок 3 умно- жения, попарно деремножаютсЯг а реауль таты (парные произведения) запоминают,ся в блоке 11 и одновременно через мультиплексор 12 суммируются в торе 13. ЗаписЬ в блок 11 осуществляется при помощи адресного счетчика 6, который в момент формирования парных прокзведе НИИ с выхода блока 3 умножения формирует последовательно коды адресов ячеек блока 11, в которые осуществляется аапись. Адресный счетчик 6 в каждом цикле формируют (3 кодов адресов, а за N ци& лов NQ кодов адресов после чего адресный счетчик 6 обнуляется и повторяет формирование кодов адресов, начиная с первого. В каждом цикле осуществляется опрос N-U ячеек памяти блока 11 с помощью блока 7 формирования адреса, что обеспечивается поступлением на него N-Ci кодов из блока 10 памяти. Изменение адресов ячеек блока 11 от цикла к циклу осуществляется блоком 7 формирования адреса путем суммирования по модулю WQ кода, определяемого но- мером цикла с кодом, вьздаваемым блоком 10 памяти. Через Мультиплексор 8 коды адресов поступают на адресные входы блока 11 с выхода которого N- парных произведен.ий, полученных и записанных в блок 11 в йредьщущие циклы, поступают через мультиплексор 12 на сумматор 13. В каждом цшсле вычисления ВКФ на первом выходе генератора 14 формируются Q импульсов, синхронизирующих считывание с блока 1 и 2 и запись результатов умножения на блок 11; на втором выходе генератора 14 формируются N-u импульсов синхронизирующих считьшание с блока 11 и управляющих работой муяьтиплексоров 8 и 12; на третьем выходе формируются импульсы для образования непрерывных циклических 2. последовательностей кодов адресов считывания как с блока 2, так и с блока 11. Каждый выходной отсчет ВКФ вычисляется путем накопления 0. последова «тельных произведений, образованных на выходе блока 3 умножения в процессе выполнения текущего цикла и |vl-Q парных произведений в выхода блока 11, образованных в предыдущие циклы. Таким образом, в каждом цикле суммируется на сумматоре 13 Ы парных произведений при количестве операций умножения в цикле в блоке 3 умножения 3 равным Q , т.е. на каждом цикле вр.емя, необходимое на операции умножения сократилось в N/Q раз. Реализация изобретения не вносит дополнительных погрещностей и при значительном увеличении быстродействия ци { рового коррелятора лищь незначительно увеличивает аппаратурные затраты, Использование цифрового коррелятора в многоканальных трактах обработки как по пространству, так и по частоте не приведет к увеличению аппаратурных затрат пропорционально росту-каналов, так как многие элементы цифрового коррелятора будут для них общими. Так при многоканальном тракте обработки по пространству едиными для всех каналов будут следующие элементы: блоки 1 задержки, адресные счетчики 4 и 6, блоки 5 и 7 формирования адреса, мультиплексор 8 и блоки 9 и 10 памяти. По сравнению с известным коррелятором время, необходимое для выполнения операций умножения, сократилось более чем в 20О раз при М 4О96, 4, что позволило отказаться от многоканаИьной структуры реализации процессора и построить коррелятор в виде последовательного одноканального устройства. Формула изобретения 1г Цифровой коррелятор, содержащий сумматор., два блока задержки, входы которЁЕ Я.Ш1ЯЮТСЯ соответственно первые; ,; агорым входами коррелятора, а выходы подключены соответственно к nepBOMj к второму входам блока умноже ния, управляющий вход первого блока задержки соединен с выходом первого адресного счетчика, вход которого соединен с первым выходом генератора имдульсов о тличающийся тем.

Авторы

Даты

1982-02-07—Публикация

1980-06-09—Подача