1

Изобретение относится к вычислительной технике и предназначено для вычисления корреляционных функций сигналов в реальном масштабе времени.

Известный коррелятор, содержащий умножитель, соединенный с управляемыми интеграторами, и генератор вспомогательного сигнала (генератор чисел), соединенный с умножителем и схемами сравнения (схемами эквивалентности) вспомогательного сигнала с сигналами с линии задержки, характеризуется относительной сложностью реализации.

Цель изобретения - унрощен«е работы устройства.

Предлагаемый коррелятор отличается от известного тем, что содержит схемы «И и распределитель, выходы которого подключены соответственно к выходам схем сравнения, выходы схем «И подключены соответственно ко вторым входам управляемых интеграторов, выход синхронизации распределителя соединен со схемой задержки.

Преимущество предлагаемого коррелятора состоит в том, что 1ИСЛО отводов от линии задержки в нем в несколько раз меньще. Это значительно упрощает устройство, особенно при цифровой линии задержки коррелятора.

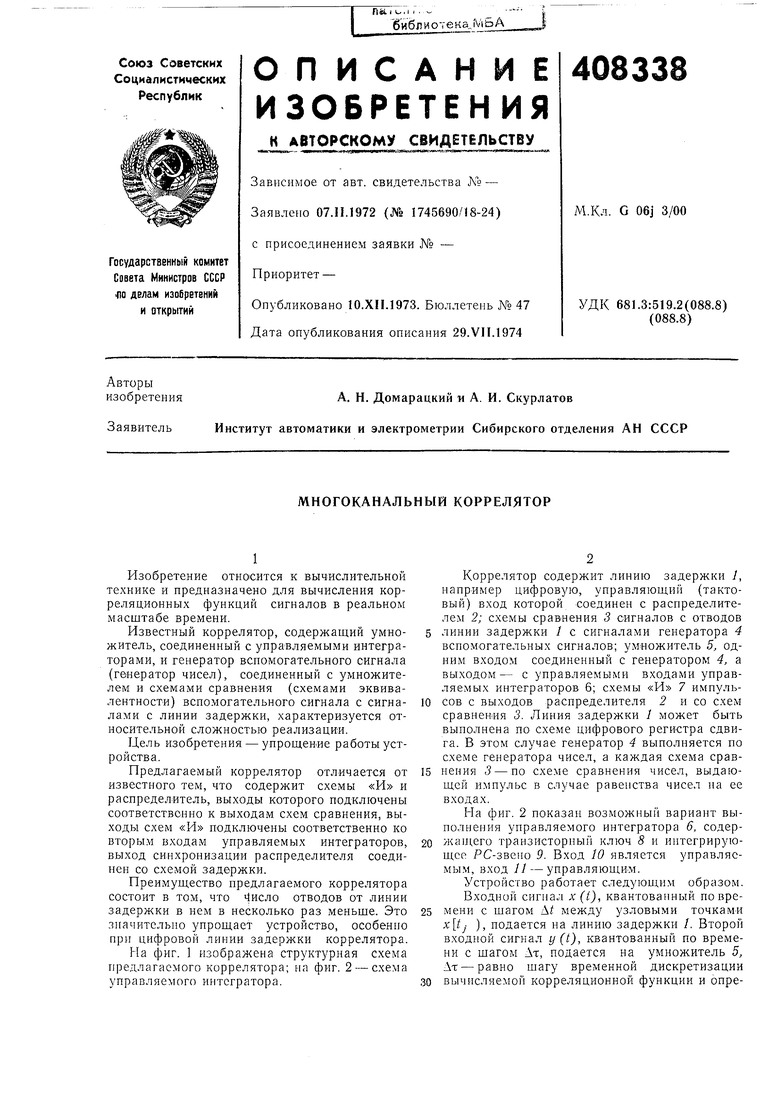

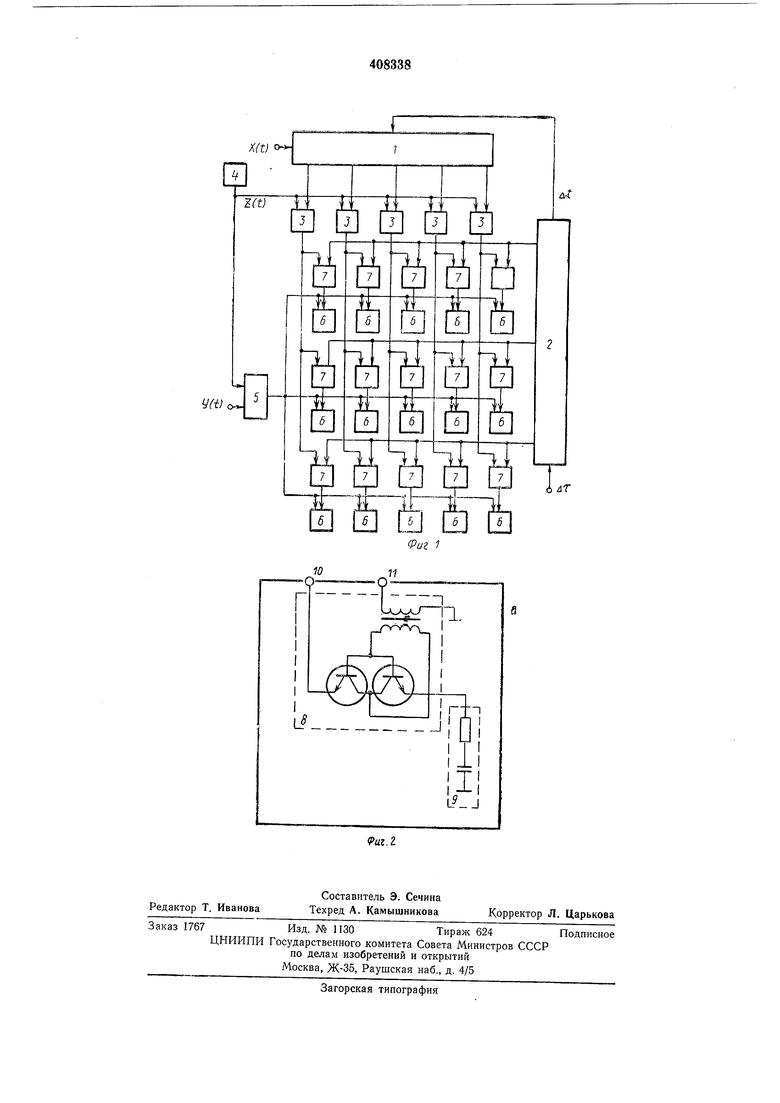

На фиг. 1 изображена структурная схема предлагаемого коррелятора; на фиг. 2 - схема управляемого интегратора.

Коррелятор содержит линию задержки У, например цифровую, управляющий (тактовый) вход которой соединен с распределителем 2; схемы сравнения 3 сигналов с отводов

линии задержки / с сигналами генератора 4 вспомогательных сигналов; умножитель 5, одним входом соединенный с генератором 4, а выходом- с управляемыми входами управляемых интеграторов 6; схемы «И 7 импульсов с выходов распределителя 2 и со схем сравнения 3. Линия задержки 1 может быть выполнена по схеме цифрового регистра сдвига. В этом случае генератор 4 выполняется по схеме генератора чисел, а каждая схема сравнения 3 - по схеме сравнения чисел, выдающей импульс в случае равенства чисе.1 на ее входах.

На фиг. 2 показан возможный вариант выполнения управляемого интегратора 6, содержащего транзисторный ключ 8 и интегрирующее РС-звено 9. Вход 10 является управляемым, вход 11 - управляющим.

Устройство работает следуюи;и.м образом. Входной сигнал x(i), квантованный повремени с шагом At между узловыми точками ), подается на линию задержки /. Второй входной сигнал y(t), квантованный по времени с шагом Лт, подается на умножитель 5, AT - равно шагу временной дискретизации

вычисляемой корреляционной функции и определяется верхней граничной частотой входных сигналов; Д Ат, где |„ -целое число, равное числу отводов от распределителя.

Распределитель 2 и линия задержки взаимно синхронизированы привязкой их тактовых импульсов к t j моментам времени. С распределителя импульсы последовательно поступают на схемы «И 7, подключая соответствующие ряды (строки), управляемых интеграторов к схемам сравнения 3 на время Ат. Сигналы с линии задержки x(tj), x(tj-At), ..., (n - 2) At, - (n- 1) Aa где n - номер отвода от линии задержки, подаются на схемы сравнения 3, на другие входы которых поступают вспомогательный сигнал z(t) с генератора 4, который принимает все возможные значения сигнала x(t). В моменты /, равенства значений сигналов на входах схем сравнения 3, последние генерируют управляющие импульсы, поступающее на управляющие входы интеграторов 6, и сигналы произведения у (f) -г (f) с выхода умножителя 5 проходят через управляемые входы интеграторов. Поскольку за Ат сигнал z (t) принимает все возможные значения х (t) то в промежутке {tj t j + AT на интеграторы 6 первого ряда поступают произведения сигнала у (tj ) на x(t f), X (tj-At), ..., . - (n-l) At. В промежуток tj + AT; t. + 2Ат распределителем 2 к схемам сравнения 5 подключен следующий ряд интеграторов 6 (остальные отключены) и получены произведения сигнала у (t + Ат) на x(ti), x(t,-At), ..., , -(n)At}.

При I-TOM шаге вычислений одного цикла получают произведения y{ti + (-1) Ат на л-Г,), x(t,-M), ..., x{t, -(.

Таким образом, за время А на интеграторы поступит П парных произведений, причем шаг задержки будет равен Ат.

Многократное повторение циклов аналогичных вычислений приводит к накоплению на интеграторах сигналов, пропорциональных значеННям точек корреляционной функции К ху ( дискретизированной по т с шагом Ат.

Предмет изобретения

Многоканальный коррелятор, содержащий

схемы сравнения, первые входы которых подключены соответственно к выходам схемы задержки, вход.которой подключен к первому входу коррелятора, вторые входы схем сравнения объединены и подключены к выходу генератора вспомогательного сигнала и к первому входу умножителя, второй вход которого соединен со вторым входом коррелятора, а выход подключен к первым входам управляемых интеграторов, отличающийся тем, что, с целью

упрощения работы устройства, он содержит схемы «И и распределитель, выходы которого подключены к первым входам схем «И, вторые входы которых подключены соответственно к выходам схем сравнения, выходы схем

«И подключены соответственно ко вторым входам управляемых интеграторов, выход синхрон изации распределителя соединен со схемой задержки.

| название | год | авторы | номер документа |

|---|---|---|---|

| МНОГОКАНАЛЬНЫЙ КОРРЕЛЯТОРBGECOiOcv,;^- ;*» 4 '•^' ••* в i Ч" в jl •*>& -^i" •' -v-;' J '-'-•••• ; ' -flAЬ:ШHu-Гt..^;.„ ,. :- ' ^ЬИБлИО^ ^iiA S | 1972 |

|

SU332471A1 |

| СПОСОБ ДЕМОДУЛЯЦИИ СИГНАЛОВ С ОТНОСИТЕЛЬНОЙ ФАЗОВОЙ МОДУЛЯЦИЕЙ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2003 |

|

RU2271071C2 |

| Время-импульсный анализаторСигНАлА | 1979 |

|

SU817725A1 |

| Аналого-цифровой коррелятор | 1981 |

|

SU1019462A1 |

| Цифровой коррелятор | 2020 |

|

RU2735488C1 |

| Цифровой автокоррелятор | 1982 |

|

SU1020835A1 |

| Цифровой коррелятор | 1980 |

|

SU903892A1 |

| ДЕМОДУЛЯТОР СИГНАЛОВ С ОТНОСИТЕЛЬНОЙ ФАЗОВОЙ МОДУЛЯЦИЕЙ | 2011 |

|

RU2460224C1 |

| Автокоррелометр | 1982 |

|

SU1084809A1 |

| Знаковый коррелометр | 1979 |

|

SU832564A1 |

Авторы

Даты

1973-01-01—Публикация