(54) АССОЦИАТИВНОЕ ЛОГИЧЕСКОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| ЛОГИЧЕСКОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1970 |

|

SU258388A1 |

| Логическое запоминающее устройство | 1979 |

|

SU864336A1 |

| ЛОГИЧЕСКОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1972 |

|

SU428450A1 |

| ЛОГИЧЕСКОЕ ЗАПОЛНИНАЮЩЕЕ УСТРОЙСТВО | 1972 |

|

SU432598A1 |

| Логическое запоминающее устройство | 1972 |

|

SU474847A2 |

| ЛОГИЧЕСКОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1973 |

|

SU368643A1 |

| ЦИФРОВОЕ ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО" | 1973 |

|

SU368606A1 |

| Логическое запоминающее устройство | 1980 |

|

SU886052A2 |

| Логическое запоминающее устройство | 1979 |

|

SU801101A2 |

| УСТРОЙСТВО для ПАРАЛЛЕЛЬНОГО СУММИРОВАНИЯДВУХ ЧИСЕЛ | 1970 |

|

SU268498A1 |

1

Изобретение относится к запоминающим | устройствам (ЗУ)

Известно ассоциативное логическое ЗУ, содержащее числовые линейки, выполненные ка магнитных сердечниках, прошитых числовыми шинами записи, считывания и чтения, подключенными к адресным формирователям записи, считывания и индикаторам совпадения соответственно, и разрядными шинами записи, считывания и чтения,по ключенными к разрядным формирователям з писи считывания и усилителям чтения соответственно,регистр признака, выходы которого подключены к информационным входам адресных схем И, регистр слова, подсоединенный к регистру маски, выходы которого через разрядные схемы И и ИЛИ подключены к соответствующим разрядным формирователялМ записи и считывания, управляющие шины и шины,сброса.

Эти запоминающие устройства построены на элементах, памяти с разветвленным магнитопроводом, производство которых поканедостаточно освоено. того, для хранения одного бита информации при-J

меняется по два трансфлюксора и требуется большое количество оборудования в

разрядных цепях.

Цель изобретения - упрощение работы устройства и повышение надежности его работы.

Предлагаемое ЗУ отличается от известного тем, что оно содержит схемы задержки, дополнительные И, пары схем ИЛИ и индикаторы регенерации - по количеству числовых линеек, один вход каждой дополнительной схемы И подключен к одной из управляющих шин, другой - к выходу соответствующего индикатора регeнepaш ИJ а выход - к входу схемы задеки и входу одной из пары схем И.ПИ, другие входы каждой пары схем ИЛИ подсоединены к выходам соответствующих адресных схем И, а выходы - к входам адресных формирователей записи и считывания, один вход каждого индикатора регенерации подключен к соответствующей числовой щине чтения, а другие - к щине сброса.

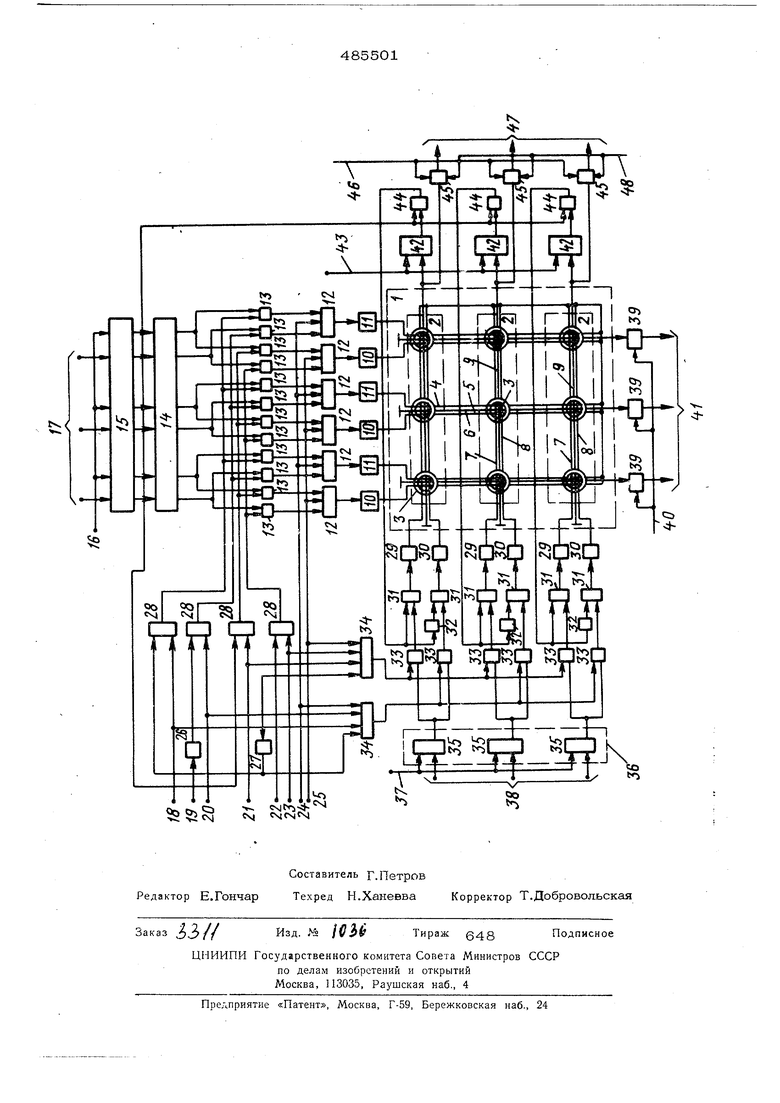

На чертеже изображена функциональная схема предлагаемого ассоциативного логйХ ческого ЗУ. Устройство содержит накопитель 1 с числовыми линейками 2 на магнитных сердечниках 3, прошитых разрядными шинами 4 считывания, разрядными шинами 5 записи, разрядными шинами 6 чтения, числовыми шинами 7 записи, числовыми шина ми 8 считьтания и числовыми шинами 9 чтения, разрядные формирователи 10 записи, разрядныеформирователи 11 чтения, разрядные схемы 12 ИЛИ, разрядные схемы И 13, регистр 14 маски, регистр 15 слова, шина 16 сброса, входы 17., управляюшие шины 18-25, схемы26 и 27 задержки, схемы 28 ИЛИ, адресные фор мирователи 29 записи, адресные формирователи 30 считывания, схемы 31 ИЛИ, схемы 32 задержки, адресные схемы И 33, схемы 34 ИЛИ, триггеры 35 регистра признаков, регистр 36 признаков, шина 37 сброса, входы 38 регистра признаков, усилители 39 чтения, шину 40 стробирования, выходы усилителей чтения, индикаторы 42 регенерации, шину 43 сброса, дополнительные схемы , индикаторы 45 совпадения, шину 46 сфоса, вЬ)1ходы 47- индикаторов совпадения, шину 48 сброса. Управляющий вход каждой дополнитель- с ной схемы И 44 подключен к управляющей шине 19, информационные входы - к выходу соответствующего индикатора 42 регенерации, а выходы дополнительных схем И 44 - к входу схемы 32 задерж ки и входу одной из пары схем ИЛИ 31 другие входы каждой пары схем ИЛИ 31 подсоединены к выходам соответствующих адресных схем И 33, |;а выходы - к уходам адресных формирователей записи ё и считывания 30. Информационные входы индикаторов 42 регенерации подсоединены к соответствующим числовым шинам 9 чтения, а управляющие - к шине 43 сброса. Устройство работает следующим образом. В исходном состоянии Б регистре 15 слова хранится входное слово X(Xi,...X;. ... Xfj ) , а в каждой числЬвой линейке 2 накопителя 1 хранится некоторое слово У ).. YtiV Регистр 14 маски находится в состоянии, при котором выделяется I -ык разряд входного слова, :а индикаторы 42 регенерации и индикаторы 45 срвпадения - в состоянии О. Логические oпepaцииJ которые могут быть реализованы в предлагаемом ЗУ, выполняются при подаче управляющих сигналов на шину 18-425. Операция ассоциативного поиска реали- зуется следующим образом. Реализация операции ассоциативного поиска в данном ЗУ основывается на выполнении операции неравнозначности поразрядно над входным словом и произвольным viacijHBOM слов, хранящихся в накопителе. Логическая операция неравнозначности реализуется за два тнДта цикла обрашения к ЗУ. В первом такте цикла при подаче управляющэго сигнала на шину 22 на выходных числовых шинах 9 чтения формируется сигнал Z-(i,) XVL который фиксируется на индикаторах 42 регенерации и индикаторах 45 совпадения, а сер- j дечники 3 числовых линеек 2 переходят в состояния Qi(t,) Xj V Yi, -Во втором такте под действием сигналов с выхода схемы 27 задержки сердечники 3 числовых линеек переходят в состояния ,(i,.)X , а на выходной шине 9 чтения наводится сигнал, соответствующий Z (t tt) у Х Таким образом, в одном из двух тактов первого цикла обращения к ЗУ на числовых щинах 9 чтения избранных числовых линеек 2 появляется сигнал, соответствующий выполнению операции сравнения (, -го разряда входного слова с I -ым разрядом каждого из слов, хранящихся в избранных j числовых линейках 2, так как Zi(t,vZi(t,T)Xiyi VX;Vi . Индикаторы 42 регенерации и индикаторы 45 совпадения фиксируют результат сравнения в I -ом разряде и в случае несовпадения признаков в данном разряде индикаторы 42 регенерации и индикаторы 45 совпадения соответствующих числовых линеек 2 переключаются в состояние 1. Каждый из опрошенных сердечников 3 t го разряда данных числовых линевк 2 принимают состояния, соответствующие результату i (t,+ T ) Х; .. Операция регенерации выполняется так-же в два такта при подаче сигнала на управляющую шину 19 в цикле регенерации. При этом в первом такте данного цикла при подаче сигнала на управляющую щину 19 под действием данного сигнала производится опрос вентилей 44, с выходов которых через схемы 31 ИЛИ на входы . адресных формирователей 29 записи прохоДят адресные сигналы возбуждения, если индикаторы регенерации 42 находятся в состоянии 1, т. е. в j,-ом. разряде избранных числовых линеек 2 был сформирован сигнал несовпадения VX у . Од- |новременно через управляющую схему 28 с инверсных выходов регистра 15 слова через регистр 14 маски, разрядные схемы И 13 и схемы 12 ИЛИ на входы разрядных формирователей 10 записи проходят разрядные сигналы возбуждения Xj 1. В результате этого в данном такте сердечники 3 опрошенных числовых линеек 2 переходят в состояния . Х-V У; , а на выходных числовых шинах J I 9 чтения наводятся сигналы Z;{t,)(. , которые подтверждают состояния индикаторов 42 регенерации и индикаторов 45 сов падения. Во втором такте второго цикла обращения через время , определяемое схемой 26 задержки, на его выходе появляется сигнал под действием которого с прямого выхода i/ -го разряда регистра 15 слова, если он находится в состоянии , через регистр 14 маски, выделяющий -ый разряд, через разрядные схемь И 13 и схемы 12 ИШ на входы разрядных формирователей 11 считывания про ходят сигналы возбуждения Xj 1. Одновременно с выходов схем 32 задержки через схемы 31 ИЛИ возбуждаются адресные формирователи 30 считывания тех числовых линеек 2, индикаторы 42 регенерации которых находятся в состояниях I Таким образом, во втором цикле обращения - цикле регенерации под действием разрядного и адресных полутоков сердечники 3 L -го разряда избранных числовых линеек 2 переходит в исходное состояние Q; (to i) У; , а на числовых шинах 9 чтения наедятся сигналы Z;(t,-« ) которые подтверждают состояния индикаторов 42 к 45. После выполнения операции сравнения J, -го разряда входного слова с i -ым разрядом каждого из избранных слов индикаторы 42 регенерации при подаче сигна ла на управляющую шину 43 сбрасывайтгся в состояние О, а в индикаторах 45 совпадения зафиксированы результаты сравнения значений I -ых разрядов входного слова и каждого из слов, хранящихся в числовых линейках 2 накопителя 1. Таким же образом реализуется операция

60 I сравнения в остальных ( ft - 1) разрядах сравниваемых слов. После выполнения операции сравнения входного слова с массивом слов, хранимых в накопителе, индикаторы 45 совпадения опрашиваются. При этом на выходах 47 появляются сигналы только с тех индикаторов, которые остались в исходном состоявми, т. е. код в данной числовой линейке 2 совпал с кодом входного слова. Предмет изобретения Ассоциативное логическое запоминающее устройство, содержащее числовые линейки, выполненные на магнитных сердечниках, прошитых числовыми шинами записи, считывания и чтения, подключенными к адресным формирователям записи, считывания и индикаторам совпадения соответственно, и разрядными шинами записи, считывания и чтения, подключенными к разрядным формирователям записи, считывания и усилителям чтения соответственно, регистр признака, выходы которого подключены к информационным входам адресных схем И, регистр слова, подсоединенный к регистру маски, выходы которого через разрядные схемы И и ИЛИ подключены к соответствующим разряднЫлМ формирователям записи и считывания, управляющие шины и шины сброса, отличающееся тем, что, с целью упрощения устройства и no-f вышения надежности его рабрты, оно содержит схемы задержки, дополнительные схемы И, пары схем ИЛИ и индикаторы регенерации - по количеству числовых линеек, один вход каждой дополнительной схемы И подключен к одной из управляющих шин, другой - к выходу соответствующего индикатора регенерации, а выход к входу схемы задержки и входу одной из ijapbi схем ИЛИ, другие входы каждой пары схем ИЛИ подсоединены к выходам соответствующих адресных схем И, а выходы - к входам адресных формирователей записи и считывания, один вход каждого индикатора регенерации подключен к соответствующей числовой шине чтения, а другие - к шине сброса.

Авторы

Даты

1975-09-25—Публикация

1972-07-18—Подача