УМНОЖИТЕЛЬ ЧАСТОТЫ ПЕРИОДИЧЕСКИХ ИМПУЛЬСОВ

Изобретение относится к области имнульсной техники и может быть использовано в синтезаторах частоты, измерителях частоты синхроиизаторах и других устройствах для умножения частоты периодических импульсов. Особенно целесообразно его .применение в диапазоне низких и инфранизких частот при большом требуемом коэффициенте умножения.

Избестнь умножители частоты имлульсов, основанные на залолнении периода входных Импульсов импульсами более высокой частоты, содержащие опорный генератор н схему занолнения.

Цель изобретения - обеспечение стабильного коэффициента умножения, уменьшение фазово-импульсной модуляции выходного сигнала и расширение рабочего диапазона частот.

Это достигается тем, что к выходу опорного генератора подключен делитель частоты с коэффициентом деления, равным требуемому коэффициенту умножения, а схема заполнения содержит два счетчика, первый из которых подключен к делителю, а второй - к опорному генератору, запоминающее устройство, подсоединенное к выходам ячеек первого счетчика, и схему сравнения, подключен-, ную к выходам ячеек запоминающего устройства и второго счетчика, выход которой соединен с выходом умнол ителя и через схему «ИЛИ - с входом установки нуля второго счетчика. При этом вход умножителя соединен с входом установки нуля запоминающего

устройства и линией задержки, часть которой подключена к входу считывания первого счетчика, а конец - к .входам установки нуля делИтеля И первого счетчика, а также к второму входу упомянутой схемы «ИЛИ.

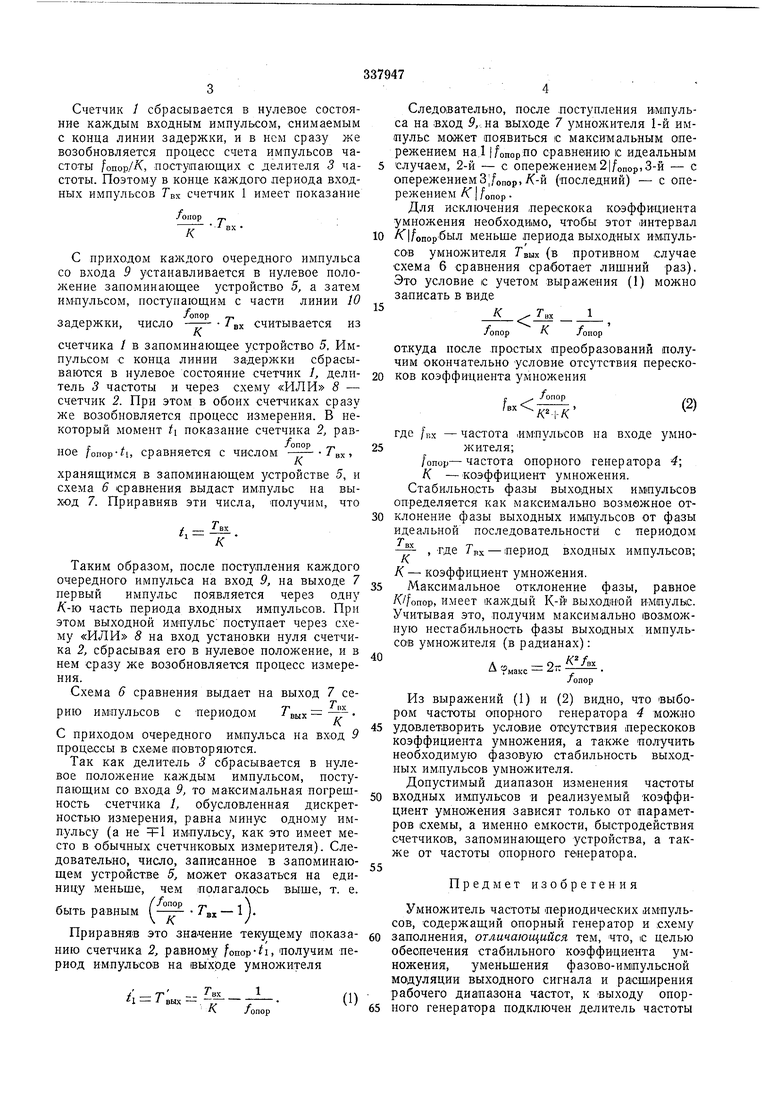

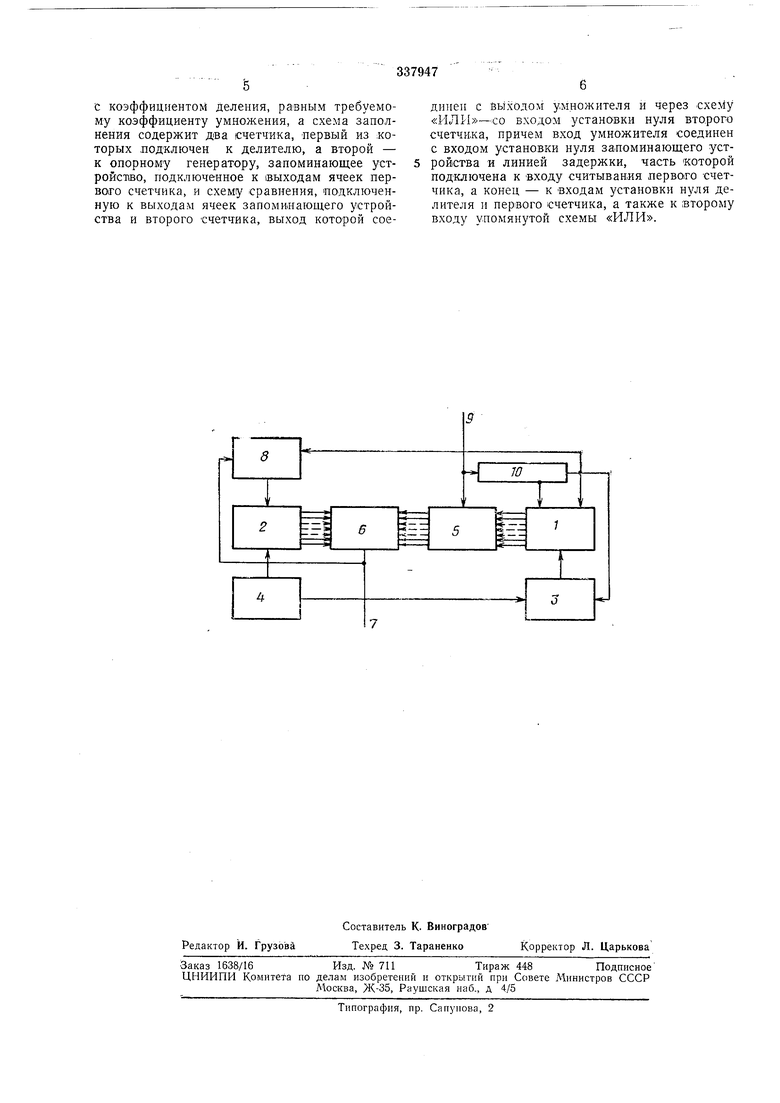

Блок-схема устройства приведена на чертеже. :

Счетчики 1 и 2 подключены к выходам соответственно делителя 3 частоты, имеющего коэффициент деления К, равный требуемому

коэффициенту умножения, и о.порного генератора 4. Выходы ячеек счетчика 1 соединены с входами запоминающего устройства 5. Выходы запоминающего устройства 5 и счетчика 2 иодключены к схеме 6 ср.авнения, от которой сигнал поступает на выход 7 умножителя и через схему «ИЛИ 8 - на вход установки нуля счетчика 2. Вход 9 умножителя связан с входом у|становки нуля запоминающего устройства 5 и началом линии 10 задержки. Отвод от ее части соединен с входом считывания счетчика 1, а К;онед - с входом установки нуля счетчика 1, входом установки нуля делителя 5 и с вторым входом упомянутой схемы «ИЛИ 8.

Счетчик 1 сбрасывается в нулевое состояние каждым входным импульсом, снимаемым с конца линии задержки, и в нем сразу же возобновляется процесс счета импульсов частоты fonof/K, пост шающих с делителя 3 частоты. Поэтому в конце каждого периода входных импульсов Гвх счетчик 1 имеет показание

/опор

Т

R

/

С приходом каждого очередного импульса со входа 9 устанавливается в нулевое положение запоминающее устройство 5, а затем импульсом, поступающим с части линии 10

/опор

задержки, число - / вх считывается из К

счетчика / в запоминающее устройство 5, Импульсом с конца линии задержки сбрасываются в нулевое состояние счетчик 1, делитель 3 частоты и через схему «ИЛИ 8 - счетчик 2. При этом в обоих счетчиках сразу же возобновляется процесс измерения. В некоторый момент /1 показание счетчика 2, рав.-,/опор „

ное /onop-ti, сравняется с числом --- / вх

хранящимся в запоминающем устройстве 5, и схема 6 сравнения выдаст импульс на выход 7. Приравняв эти числа, получим, что

Таким образом, после поступления каждого очередного импульса на вход 9, на выходе 7 первый импульс появляется через одну Л-ю часть периода входных импульсов. При этом выходной импульс поступает через схему «ИЛИ 8 на вход установки нуля счетчика 2, сбрасывая его в нулевое положение, и в нем сразу же возобновляется процесс измерения.

Схема 6 сравнения выдает на выход 7 сепх

рИЮ импульсов с периодом вых -

с приходом очередного импульса на вход 9 процессы в схеме повторяются.

Так как делитель 5 сбрасывается в нулевое положение каждым импульсом, поступающим со входа 9, то максимальная погрешность счетчика /, обусловленная дискретностью измерения, равна минус одному импульсу (а не +1 импульсу, как это имеет место в обычных счетчиковых измерителя). Следовательно, число, записанное в запоминающем устройстве 5, может оказаться на единицу меньше, чем полагалась выше, т. е.

ffonop ..N

./ /опор

быть равным I - К

(Г J

Приравняв это значение текущему показанию счетчика 2, равному fonop- i, получим период импульсов на выходе умножителя

Следовательно, после .поступления импульса на вход Я:на выходе 7 умножителя 1-й импульс может появиться с максимальным опережением на Ifonopno сравнению с идеальным случаем, 2-й - с опережением 2|/опор.3-й - с опережением3|/опор.-й (последний) - с опережением AIfonopДля исключения перескока коэффициента

умножения необходимо, чтобы этот интервал

K fonof6bin меньше периода выходных и-мпульсов умножителя Гвых (в противном случае схема 6 сравнения сработает лишний раз). Это условие с учетом выражения (1) можно записать в виде

.;Zsx . 1

/опорА/опор

откуда после простых преобразований получим окончательно условие отсутствия перескоков коэффициента умножения

/опор

Гвх

(2)

К.

где /,.,х - частота импульсов на входе умножителя;

/опор-частота опорного генератора 4; К - коэффициент умножения. Стабильность фазы выходных импульсов определяется как максимально возможное отклонение фазы выходных импульсов от фазы идеальной последовательности с периодом

J DVгт-1

-Г , тде 7 Ех - период входных импульсов;

К - коэффициент умножения. Максимальное отклонение фазы, равное K/fomp, имеет каждый К-й выходной и-мпулыс. Учитывая это, получим максимально «озможную нестабильность фазы выходных импульсов умножителя (в радианах):

Д макс /опор

Из выражений (1) и (2) видно, что выбором частоты опорного генератора 4 можно удовлетворить условие отсутствия перескоков коэффициента умножения, а также получить необходимую фазовую стабильность выходных им.пульсов умножителя.

Допустимый диапазон изменения частоты входных импульсов и реализуемый коэффициент умножения зависят только от параметров схемы, а именно емкости, быстродействия счетчиков, запоминающего устройства, а также от частоты опорного генератО|ра.

Предмет изобретения

Умножитель частоты периодических импульсов, содержащий опорный генератор и схему

заполнения, отличающийся тем, что, с целью обеспечения стабильного коэффициента умножения, уменьшения фазово-импульсной модуляции выходного сигнала и расширения рабочего диапазона частот, к выходу опорс коэффициентом деления, равным требуемому коэффициенту умножения, а схема заполнения содержит д;ва счетчика, первый из ;которых .подключен к делителю, а второй - к опорному генератору, запоминающее устройстто, подключенное к выходам ячеек первого счетчика, и схему сравнения, подключенную к выходам ячеек запоминающего устройства и второго счетчика, выход которой соединен с выходом умножителя и через схеМу входом установки нуля второго счетчи,ка, причем вход умножителя соединен с входом установки нуля запоминающего устройства и линией задержки, часть которой подключена к входу считывания первого счетчика, а конец - к входам установки нуля делителя и первого счетчика, а также к второму входу упомянутой схемы «ИЛИ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Умножитель частоты периодических импульсов | 1972 |

|

SU438123A1 |

| Умножитель частоты периодических импульсов | 1973 |

|

SU468375A1 |

| Умножитель частоты следованияиМпульСОВ | 1979 |

|

SU824418A1 |

| Умножитель частоты | 1978 |

|

SU750711A2 |

| Умножитель частоты | 1978 |

|

SU746885A1 |

| Умножитель частоты | 1977 |

|

SU748882A2 |

| Умножитель частоты | 1974 |

|

SU530462A1 |

| Умножитель частоты периодических импульсов | 1978 |

|

SU741433A2 |

| Устройство для умножения частоты следования импульсов | 1980 |

|

SU884102A1 |

| Умножитель частоты следования импульсов | 1977 |

|

SU664303A1 |

Даты

1972-01-01—Публикация