ки нуля делителя частоты и первого счетчика и ко второму входу элемента И, введены регистр сдвига, счетный вход которого соединен с выходом опорного генератора, дешифратора выходы которого подключены ко входам регистра сдвига, дополнительное запоминакадее устройство,обнуляющий вход которого соединен со входом линии задержки, установочные входы с выходами делителя частоты, а выходы - со входами дешифратора и дополнительный делитель частоты, счетный вход которого соединен с выходом блока сравнения и входом дешифратора, обнуляющий вход - с выходом лини задержки, отвод которой подключен ,к счетному входу делителя частоты, а выходы с дополнительными входами дешифратора .

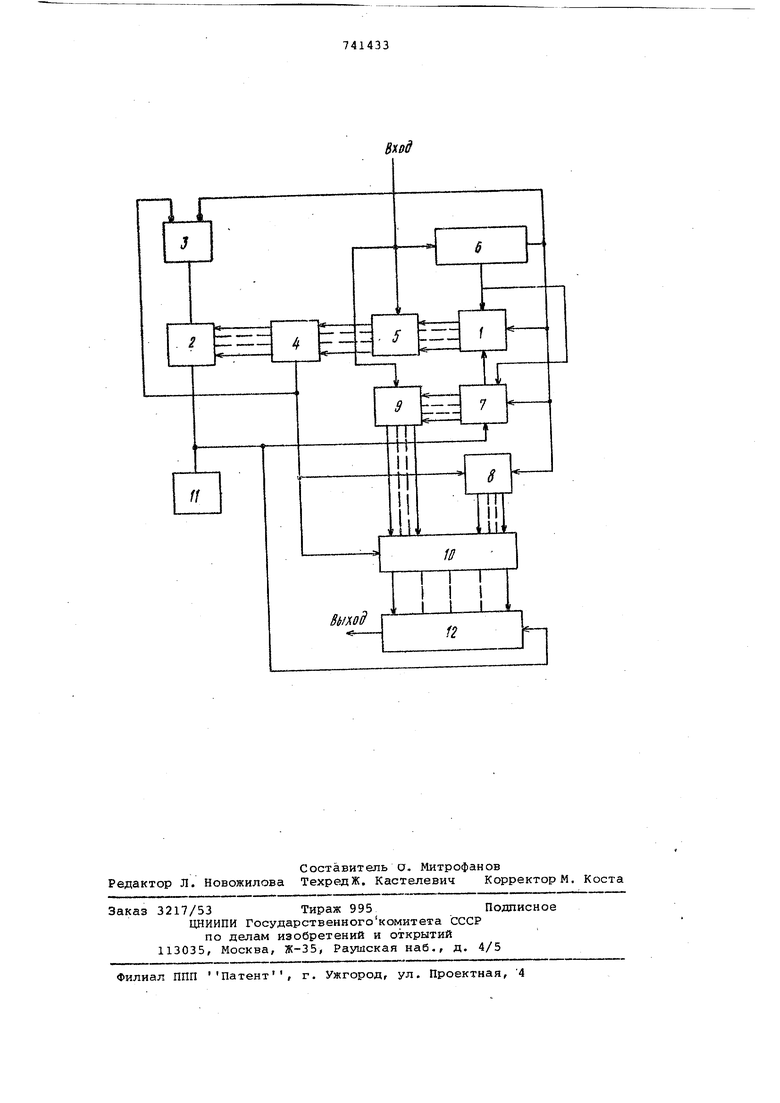

На чертеже изображена структурная электрическая схема умножителя частоты периодических импульсов.

Он содержит первый и втогой счетчики 1 и 2 импульсов, элемент ИЛИ 3, блок сравнения 4, запоминающее устройство 5, линию задержки 6, делитель 7 частоты, дополнительный делитель 8 частоты, дополнительное запоминаюМё устройство 9, дешифратор 10 опорный генератор 11 и регистр 12 сдвига.

Счетчики 1 и 2 импульсов подключены к выходам соответственно делителл 7 частоты, имеющего коэффициент деления 5, равный требуемому коэффициенту умножения и опорного генератора 11. Выходы ячеек счетчика 1 соединены с входами запоминающего устройства 5. Выходы запоминающего устройства 5 и счетчика 2 подключены к блоку 4 сравнения, от которого сигнал поступает на вход дополнительного делителя 8, стробирующий вход дешифратора 10, и первому входу элемента ИЛИ 3. Вход умножителя связан с входами установки нуля запоминающего устройства 5, дополнительного запоминающего устройства 9 и началом линии задержки 6. Отвод от ее части соединен с входами счетчика 1 и делителя- 7, а конец - с в::одом установки нуля счетчика 1, входом установки нуля делителя 7, входом установки дополнительного де.лителя 8 и со вторым входом эле- мента. ИЛИ 3, Выходы ячеек делителя 7 соединены со входами дополнительного запоминающего устройства 9. Ячейки дополнительного запоминающего устройства 9 и дополнительного делителя 8 соединены со входси 1И дешифратора 10, к - входов которого со Динены с соответствующими к -входами установки к-разрядного регистра 12 сдвига. Счетный вход регистра 12 сдвига соединен с выходом опорного, генератора 11, а выход является вы/ходом умножителя.

В описываемом устройстве величиfla (к -т), где (к - гп ) число, записанное в делитель 7 частоты, измеряется с помощью дополнительного запоминающего устройства 9, в которое из делителя 7 переписывается ин формация после прихода входного сигнала. Номер периода i выходного сигнала подсчитывается дополнительным делителем & на к + 1. Операция где 3 . - целая часть числа реализуется с помощью дешифратора 10 с к выходами, который строится таким образом, что в зависимости от числа, записанного в дополнительное запоминающее устройство 9 и текущего значения, записанного в дополнительном делителе 8 на (к t 1), единица появляется только на том выхде дешифратора 10, номер которого определяется выражением

Y.{

Задержка каждого выходно1о импульса блока 4 сравнения на величину т, определенную выражением

,

г

к Io ,

где TO - период частоты опорного генератора 11 осуществляется с помощью

к разрядного регистра 12 сдвига, в соответствующий разряд которого записывается единица из дешифратора 10 при наличии стробирующего импульса на входе дешифратора 10, путем постоянного списывания из регистра 12 сдвига записанных единиц с частотой опорного генератора 11.

Рассмотрим работу схегФ. Дели тель частоты 7 считает импульсом опорного генератора 11 частоты fonoPH/ а счетчик 1 импульсы частотыfo pj,/к, поступающие с делителя частоты 7. В конце каждого периода умножаемой частоты счетчик 1 имеет показания, равные о„ор /к{9 где - частота на входе устройства, определенные числом импульсов, поступивших на вход делителя частоты 7 в интервале между импульсами частоты i .В этот момент показания делителя частоты определяются остатком от делени числа импульсов, поступивших на вход делителя частоты 7 на коэффициент деления К. Остаток может быть меньше или равен (к - 1) . Таким образом, в запоминающее устройство 5 записывается частное от деления опорнА ь)с S дополнительное запоминающее устройство 9 остаток от деления. Запись Чисел в запоминающие устройства 5 и 9 осуществляется импульсом, снимаемым с отвода линии задержки 6, а их подготовка - импульCCW, поступающим на вход умножителя Коэффициент пересчета счетчика 2 определяется числом, хранящимся в запоминающем устройстве 5. За период умножаемой частоты на вход счетчика 2 поступает число импульсов от опорного генератора 11, равн отнсмению{о„(,.„Лр;( . Счетчик 2, непрерывно считая импульсы опорного генератйра 11, при помощи блока 4 сравнения сравнивают число импульсов, поступающее на его вход, с числом, записанным в запоминающее устройство, 5. При достижении равенс ва этих чисел блок 4 сравнения выдает импульсы, который поступает на вход элемента ИЛИ 3, устанавливая счетчик 2 в нулевое состояние. Кроме того, этот же импульс поступает на вход дополнительного делителя 8, который подсчитывает количество этих импульсов, и на стробирующий вход дешифратора 10, разрешая появление единицы на одном к - выходом дешифратора. Остаток от деления, хранящийся в дополнительно запоминающем устройстве 9 подается на входы дешифратора 10, на другие входы которого подается число, записанное в дополнительный делитель Дополнительный делитель 8 обнуляетс входным импульсом, задержанный линией задержки б, Входной набор детаифратора 10 от импульсов к импульсу на выходе бло ка сравнения 4 постоянно изменяется. При этом в зависи1 1ости от входного набора при наличии стробирующ импульса единица появляется на том выходе дешифратора 10, номер которого определяется выражением 1. Еди ница, появляющая на выходе даиифра тора 10 записывается в.соответств .щий разряд регистра 12 сдвига, откуда она описывается импульсами, с дующими с частотой опорного генера тора 11. В случае, когда для выход блока 4 сравнения не выполняется у лавйелт„д {к - 1) TO evV (2), гд ДТ - макс максимальная абсолютная фазово-импульснаянестабильность, входной частоты, дополнительный де литель 8 сосчитав (к + 1) импульс сохраняет это состояние до прихода обнуляющего импульса с выхода линии задержки 6, при этом запись единиц в разряды регистра 12 сдвига пре- кращается, поскольку этому состоянию дополнительного делителя В соответствуют нули на всех катодах дешифратора 10, Положительный эффект описанного умножителя частоты периодических импульсов состоит в расширении рабочего диапазона умножаемых частот. Это достигается тем, что задержка каждого выходного импульса блока сравнения 4 на величину ТГ , определяемую выражением 1, позволяет снизить фазово-импульсиую нестабильность умножения частоты. Формула изобретения Умножитель частоты периодических импульсов по авт. св. № 337947, о тличающийся тем; что, с целью расширения рабочего диапазона частот, в него введены регистр сдвига, счетный вход которого соединен с выходом опорного ген атора, дешифратор, выходы которого подключены ко входам регистра сдвига, дополнительное запоминающее устройство, обнуляющий вход которого соединен со входом линии задержки/ установочные входы - с выходами делителя частоты, а выходы - со входами дешифратора, и дополнительный делитель частоты, счетный вход которого соединен с выходом блока сравнения и входом дешифратора, обнуляющий вход - с выходом линии задержки, отвод которой подключен к счетному входу делителя частоты, а выков - с дополнительными входами дешифратора. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР 337947, кл. Н 03 К 23/00,23.1.70.

| название | год | авторы | номер документа |

|---|---|---|---|

| Умножитель частоты следования импульсов | 1981 |

|

SU1018219A1 |

| Умножитель частоты следования импульсов | 1981 |

|

SU1012431A1 |

| Умножитель частоты периодических импульсов | 1973 |

|

SU468375A1 |

| Устройство для коррекции шкалы времени | 1985 |

|

SU1247828A2 |

| Умножитель частоты следования импульсов | 1981 |

|

SU993461A1 |

| Пересчетное устройство | 1981 |

|

SU993460A1 |

| Устройство для деления периодов следования импульсных сигналов | 1977 |

|

SU732902A1 |

| Умножитель частоты следования импульсов | 1982 |

|

SU1038943A1 |

| Цифровой умножитель частоты | 1979 |

|

SU788363A1 |

| Умножитель частоты следования импульсов | 1982 |

|

SU1072755A1 |

Авторы

Даты

1980-06-15—Публикация

1978-02-08—Подача