(54) УМНОЖИТЕЛЬ ЧАСТОТЫ

| название | год | авторы | номер документа |

|---|---|---|---|

| Умножитель частоты | 1974 |

|

SU530462A1 |

| Умножитель частоты | 1977 |

|

SU748882A2 |

| Умножитель частоты следованияиМпульСОВ | 1979 |

|

SU824418A1 |

| ПАТЕНТВО-ТЕКШ12БИБЛИОТЕКАВ. А. Иванов | 1972 |

|

SU337947A1 |

| Умножитель частоты | 1978 |

|

SU746885A1 |

| Умножитель частоты следования импульсов | 1977 |

|

SU664303A1 |

| Умножитель частоты периодических импульсов | 1978 |

|

SU741433A2 |

| Умножитель частоты | 1979 |

|

SU907781A1 |

| Умножитель частоты периодических импульсов | 1972 |

|

SU438123A1 |

| Умножитель частоты повторения импульсов | 1977 |

|

SU687602A1 |

Изобретение относится к измерительной технике, автоматике и может использоваться, в частности, в системах регулирования авиационных двигателей.

Известен умножитель частоты, содержащий последовательно соединенные первый счетчик и делитель частоты, входы которых объединены и через линию задержки подключены к входной шине и к входу запоминающего устройства, входы которого соединены с выходами ячеек первого счетчика, опорный . генератор, выходы которого подключены к входам второго счетчика и делителя частоты, элемент совпадения и дополнительную линию задержки, под ключенную к выходу элемента совпадения и к второму входу второго счетчика, выходы ячеек которого соединены с входами элемента совпадения, а входы ячеек - с выходами запоминающего устройства 1.

Недостатком описанного умножителя частоты является возникающая при совпадении моментов считывания показаний из первого счетчика в запоминающее устройство и показаний запоминиющего устройства во второй счетчик возможность ошибки.

Целью изобретения является повышение точности умножения.

С этой целью в умножитель частоты, содержащий последовательно соединенные первый счетчик и делитель частоты, входы которых объединены и через линию задержки подключены к входной шине и к входу запоминающего устройст10ва, входы которого соединены с выходами ячеек первого счетчика, опорный генератор, выходы которого подключены к входам второго счетчика и делителя частоты, элемент совпадения и до15полнительную линию задержки, подключенную к входу элемента совпадений и ко второму входу второго счетчика, выходы ячеек которого соединены с входами элемента совпадения, а входы яче20ек - с выходами запоминающего устройства, введены элемент ИЛИ, включенный между вторым входом второго счетчика и выходом дополнительной линии задержки, дополнительный элемент совпадения,

25 входы которого соединены с выходом дополнительной линии задержки и с выходом запоминающего устройства, и элемент задержки, вход которого соединен с выходом дополнительного эле30

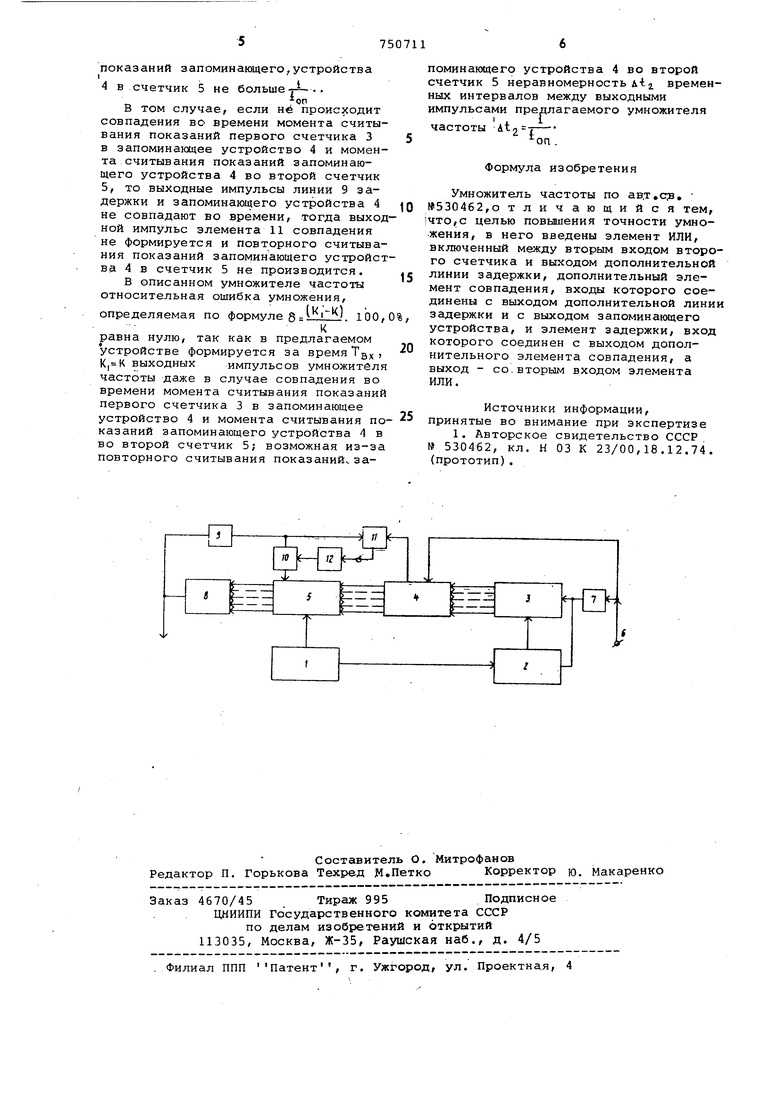

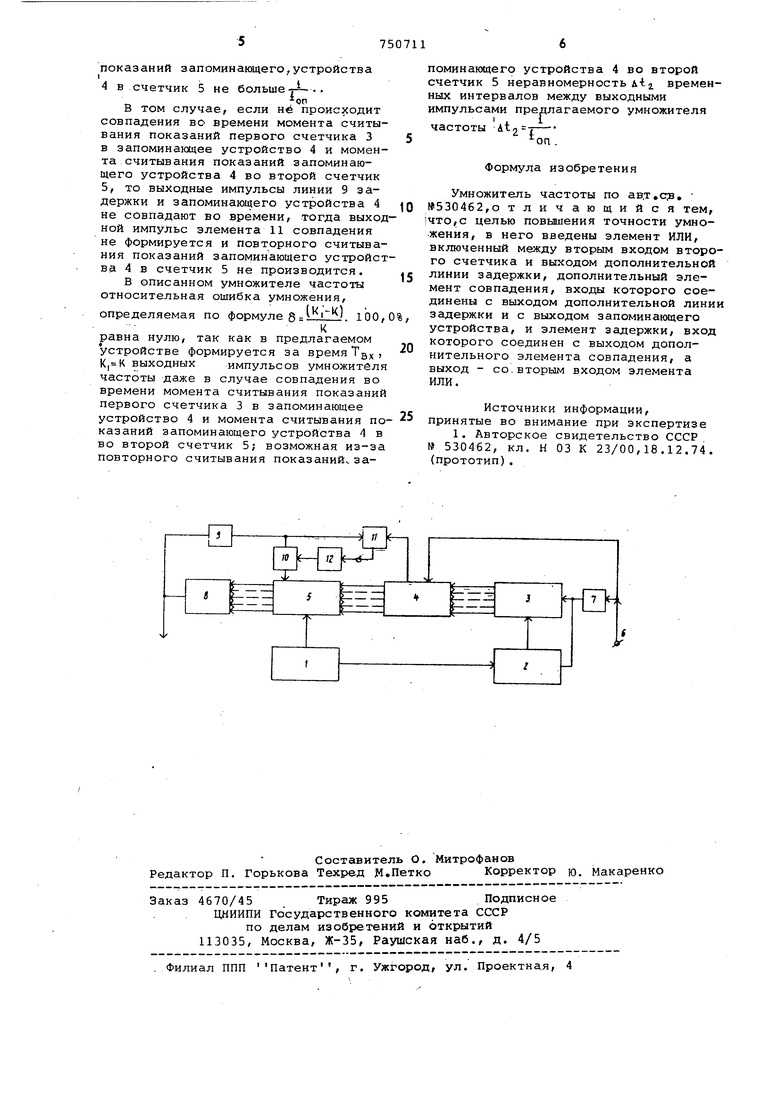

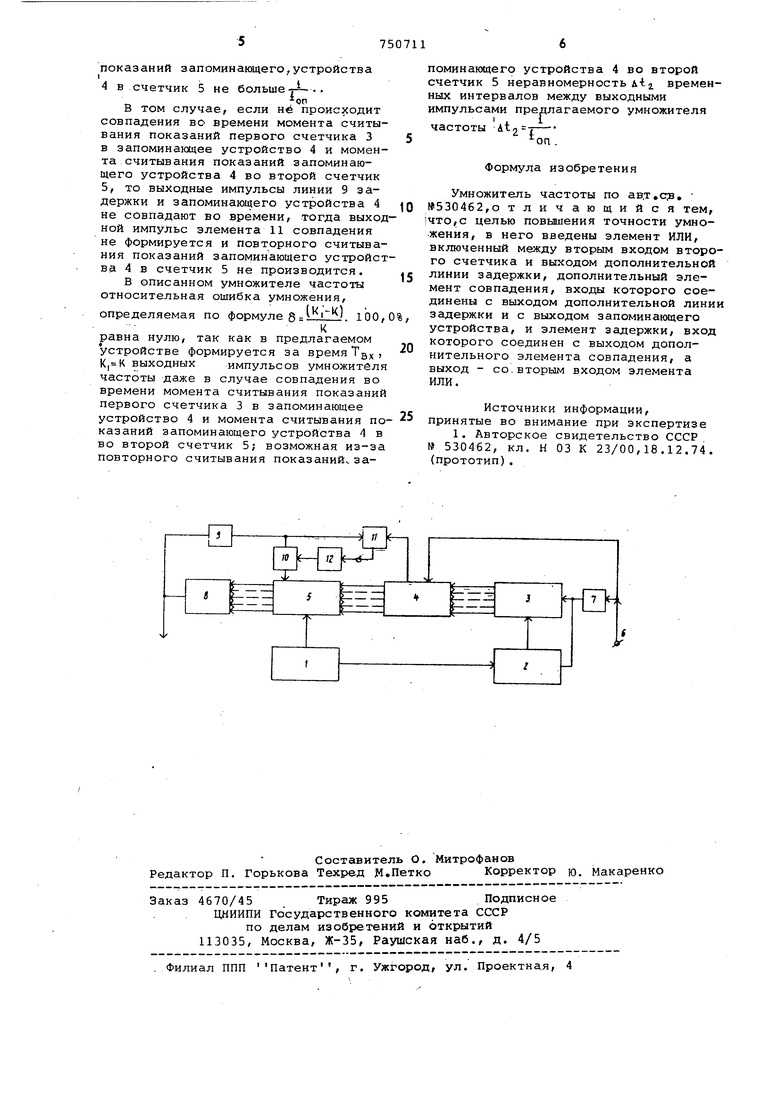

..мента совпадения, а выход - со вторым входом элемента ИЛИ. На чертеже изображена структурная электрическая схема умножителя частоты, содержащего опорный генератор 1, делитель 2 частоты, первый счетчи 3, запоминающее устройство 4, второй счетчик 5, входную шину б умножителя линию 7 задержки, элемент 8 совпадения, дополнительную линию 9 задержки лемент ИЛИ 10, дополнительный элеме 11 совпадения и элемент 12 задержки. Умножитель частоты состоит }гз генератора 1, опорной Частоты соединен ного с входом делителя 2 частоты с коэффициентом деления, равным требуе мому коэффициенту умножения, к выходу которого подключен вход первого счетчика 3. К выходам ячеек счетчика 3 подкл{очено запоминающее устройс во 4, к выходам ячеек которого подключен второй счетчик 5, выполненный вычитающим. Вход счетчика 5 соединен с опорным генератором 1. Входная шина 6 подключена к цепям считывания показаний счетчика 3 в запоминающее устройство 4 и к выходу линии 7 задержки, выход которой подключен к цепям сброса на нуль первого, счетчик 3 и делителя 2 частоты. Выход умножителя подключен к элементу 8 совпадения, входы которого подключены к выходам ячеек счетчика 5 к входу линии 9 задержки, выход которой подклю чен ко входам элемента ИЛИ 10, допол . нительного элемента 11 совпадения,второй вход которого связан с выходо запоминающего устройства 4, а выход через элемент 12 задержки соединен со вторым входом элемента ИЛИ 10, выход которого подкл ючен к цепям считывания показаний запоминающего устройства 4 во второй счетчик 5. Умножитель частоты работает следующим образом. После прохождения через линий 7 задержки очередного импульса, поступившего на входную шину 6 умножителя частоты, происходит сброс на нуль счетчика 3 и делителя 2 частоты Затем происходит накопление счетчиком 3 импульсов, поступающих с выход делителя 2 частоты. К моменту прихода на вход умножителя частоты следую щего импульса, в счетчик 3 записывае {-Г Входной импульс ся число умножителя частоты поступает к цепям считывания показаний счетчика 3 в запоминающее устройство 4, которое формирует во время считывания показаний импульс, поступающий на вход элемента 11 совпадения. Импульс с выхода линии 7 задержки сбрасывает на нуль счетчик 3 и делитель частоты. Таким образом, в запомниаквдё устройстве 4 хранится всё время чис ло, соответствующее периоду входной частоты. Это число не стирается, а олько может изменяться в случае, сли изменяется входная частота. мпульсы опорного генератора 1, поступая- на вход вычитающего счетчика 5, некоторый момент приводят его в улевое состояние В момент попадания го в нулевое состояние с выхода элемента В совпадения поступает имульс на выход умножителя частоты. тот же импульс поступает на вход линии 9 задержки после прохождения чеез которую поступает на вход элемента ИЛИ 10, выходной импульс которого производит запись показаний запоминаюего устройства 4 в счетчик 5. Слеующий импульс на выходе умножителя частоты появляется через время. 1.Т t- .. It частота опорного генератора;период входных сигналов; коэффициент умножения В случае, если считьшание показа-. НИИ запоминающего устройства 4 в счетчик 5 совпадает во времени с считыванием показаний счетчика 3 в запоминающее устройство 4, то выходной импульс линии 9 задержки совпадает во времени с выходным импульсом запоминающего устройства 4, что приводит к появлению выходного импульса элемента 11 совпадения, который, пройдя через элемент 12 задержки, поступает во второй вход элемента ИЛИ 10. Выходной импульс элемента ИЛИ 10 поступает на второй вход счетчика 5 и производит повторную запись показаний запоминающего устройства 4 в счетчик 5. (Первая запись показаний производится выходные импульсом элемента ИЛИ 10, на вход которой поступает выходной импульс линии 9 задержки, совпадающей во времени с выходным импульсом запоминающего устройства 4 - т.е. в тех условиях, при которых возможно неверное считывание показаний запоминающего устройства 4 в счетчик 5). Время задержки t элемента 12 задержки должно удовлетворять неравенству t.4 - t - А , где t - наибольшая из длительностей двух импульсов: выходного импульса запоминающего устройства 4 и выходного импульса линии 9 задержки; Д максимально допустимая величина неравномерности временных интервалов между выходными импульсами умножителя частоты, возникающая из-за повторного считывания показаний запоминающего устройства 4 в счетчик 5. При ,f неравномерность вре оп менных интервалов между выходными импульсами умножителя частоты, воз никающая из-за повторного считывания показаний запоминающего,устройства 4 в счетчик 5 не больше . fon В том случае, если не происходит совпадения во времени момента считывания показаний первого счетчика 3 в запоминающее устройство 4 и момента считывания показаний запоминающего устройства 4 во второй счетчик 5, то выходные импульсы линии 9 задержки и запоминающего устройства 4 не совпадают во времени, тогда выход ной импульс элемента 11 совпадения не формируется и повторного считывания показаний запоминающего устройст ва 4 в счетчик 5 не производится. В описанном умножителе частоты относительная ошибка умножения, ). ibo. определяемая по формулеS равна нулю, так как в предлагаемом устройстве формируется за время Тц К, К выходных импульсов умножителя частоты даже в случае совпадения во времени момента считывания показаний первого счетчика 3 в запоминающее устройство 4 и момента считывания по казаний запоминающего устройства 4 в во второй счетчик 5; возможная из-за повторного считывания показаний заоминающего устройства 4 во второй четчик 5 неравномерность A-tj. временных интервалов между выходными импульсами предлагаемого умножителя частоты Формула изобретения Умножитель частоты по ан.т,с;в, №530462,0 тличающийся тем, что,с целью повышения точности умножения, в него введены элемент ИЛИ, включенный между вторым входом второго счетчика и выходом дополнительной линии задержки, дополнительный элемент совпадения, входы которого соединены с выходом дополнительной линии задержки и с выходом запоминающего устройства, и элемент задержки, вход которого соединен с выходом дополнительного элемента совпадения, а выход - со.вторым входом элемента ИЛИ, Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР, №530462, кл, Н 03 К 23/00,18.12.74. (прототип).

Авторы

Даты

1980-07-23—Публикация

1978-01-20—Подача