Предлагаемое устройство управления буферной памяти для накопления и считывания информации в пОрядке ее поступления может быть использовано при проектировании схем ввода и вывода данных в цифровых системах связи, а также в цифровых вычислительных машинах, если необходимо накапливать однородную информацию в шамяти и производить ее выборку для дальнейшей обработки в порядке очереди.

Известны устройства управления буферной памяти, содержащие матрицу числовых трансформаторов, магнитный дешифратор записи, магнитный шифратор и схемы «И.

Предл агаемое устройство отличается тем, что, с целью повышения надежности устройства, сердечники шифратора и матрицы числовых трансформаторов последовательно прошиты соответствующими выходными шинами магнитного дешифратора записи и ма-гнитного дешифратора считывания. Выходные обмотки сердечников магнитного дешифратора подключены через схемы «И к источнику сигнала записи, соединены со входными обмотками магнитного дешифратора записи, выходные обмотки сердечников -магнитного дешифратора подключены через схемы «И к источнику сигнала считывания и соединены со входными обмотками магнитното дешифратора считывания.

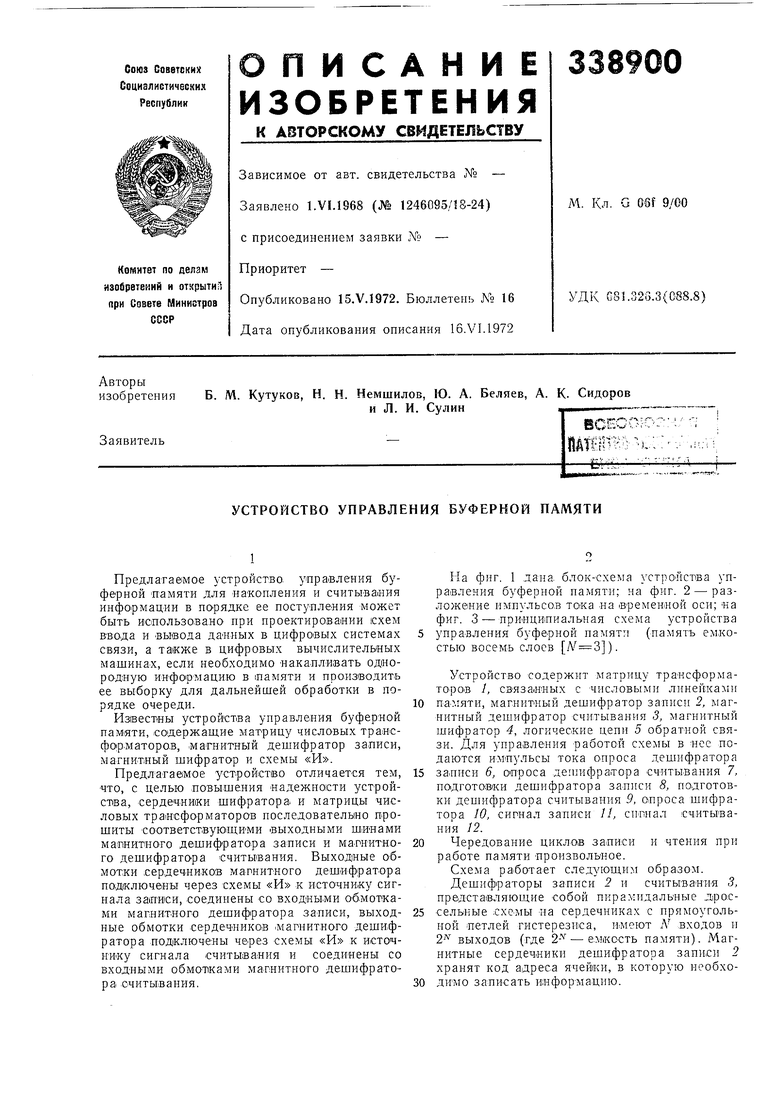

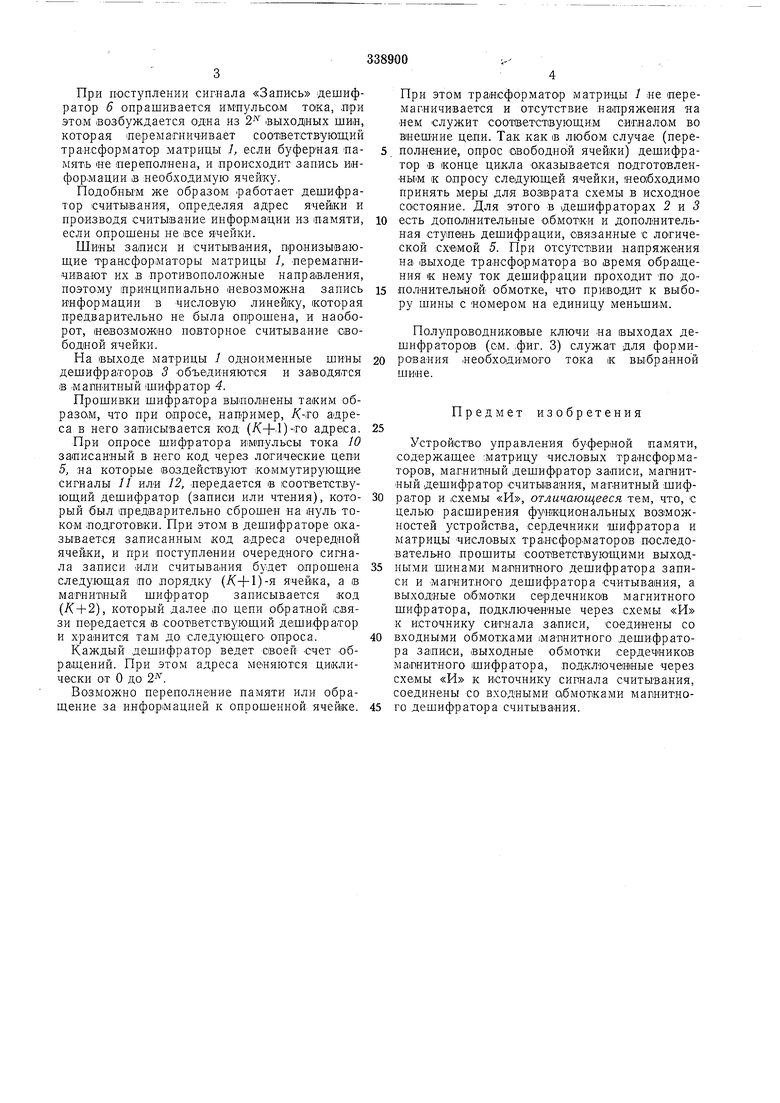

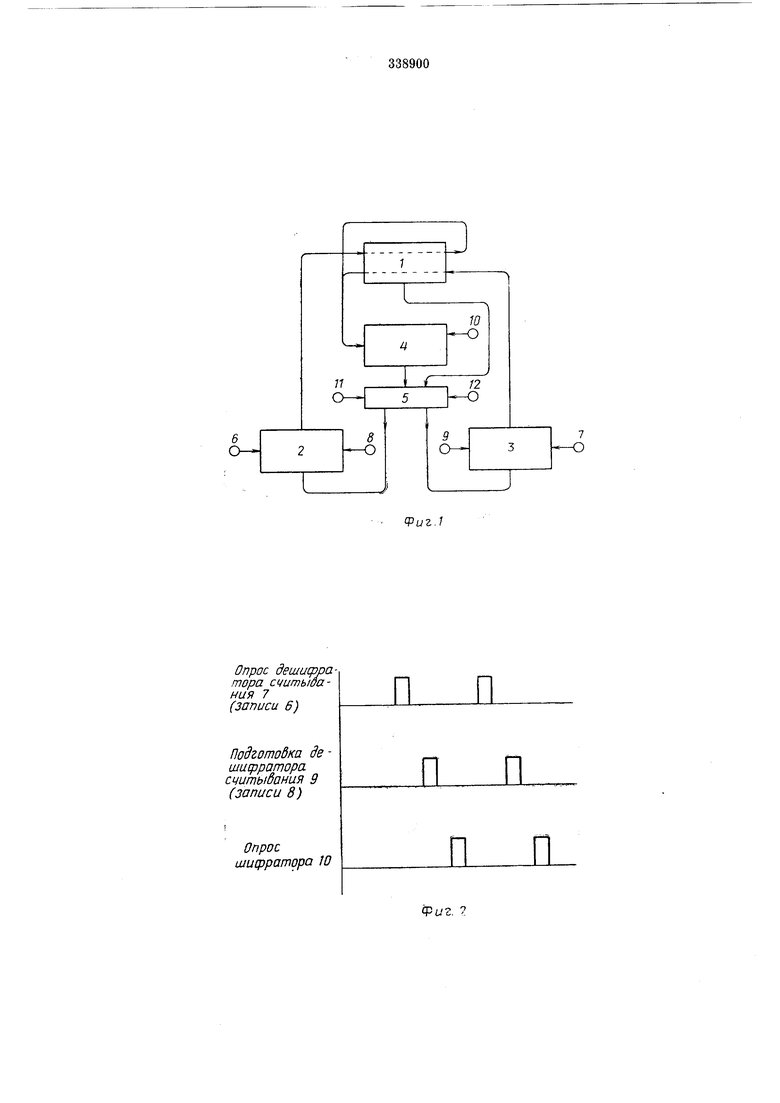

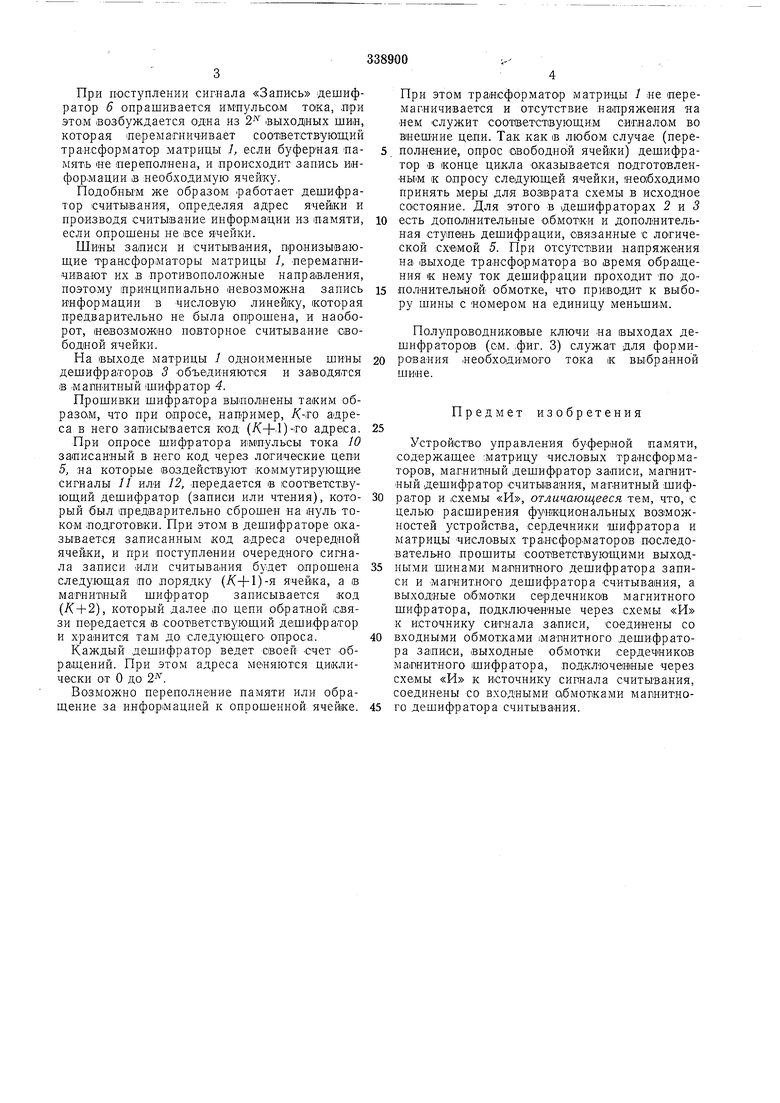

На фиг. 1 дана, блок-схема устройства управления буферной намяти; на фиг. 2 - разложение нм пуль с ОБ тока на временной оси; «а фиг. 3-принципиальная схема устройства управления буферной памятп (память емкостью восемь слоев ).

Устройство содержит матрицу трансформаторов /, св-язанных с числовыми линейками

памяти, магнитный дешифратор записи 2, магнитный дешифратор считывания 3, магнитный шифратор 4, логические цепи 5 обратной связи. Для управления работой схемы в нее подаются импульсы тока опроса дешифратора

записи 6, опроса дешифратора считывания 7, подготовки дешифратора записи 8, подготовки дешифратора считывания 9, опроса шифратора 10, сигнал записи //, силнал считывания 12.

Чередование циклов записи и чтения при работе намяти произвольное. Схема работает следующим образом. Дешифраторы записи 2 и считывания 3, представляющие собой пирамидальные дроссельные схемы на сердечниках с прямоугольной петлей гистерезиса, Л входов и выходов (где - емкость памяти). Магнитные сердечники дешифратора записи 2 хранят код адреса ячейки, в которую необхоПри поступлении сиг-нала «Зались дешифратор 6 опрашивается импульсом тока, при этом возбуждается одна из (Выходных шин, которая перемагниЧИвает соответствующий трансформатор матрицы 1, если буферная память ее переполнена, и происходит запись инфор.мации iB необходимую ячейку.

Подобным же образом работает дешифратор считывания, определяя адрес ячей|ки и производя считывание информации из памяти, если опрошены не все ячейки.

Шины записи и считывания, Пронизываюш;ие тран сфор|Маторы матрицы 1, перемагничивают их в противоположные нанравлеяия, поэтому принципиально невозможна запись информации в числовую линейку, которая предварительно не была опрошена, и наоборот, невозможно повторное считывание свободной ячейки.

На выходе матрицы 1 одноименные шины дешифраторов 5 объединяются и заводятся в малнитный шифратор 4.

Прошивки шифратора выполнены таким образом, что при опросе, например, /(-го адреса в него записывается код (Ki-{-l) адреса. При опросе шифратора вмпульсы тока 10 записанный в него код через логические цепи 5, на которые воздействуют коммутирующие сигналы 11 или 12, пе редается в соответствующий дешифратор (записи или чтения), который был предварительно сброшен на нуль током подготовки. При этом в дешифраторе оказывается записанным код адреса очередной ячейки, и при поступлении очередного сигнала записи или считывания будет опрощена следующая по порядку ()- ячейка, а в магнитный шифратор записывается ко.ц (/(+2), который далее по цепи обратной связи передается е соответствующий дешифратор и хранится там до следующего опроса.

Каждый дешифратор ведет своей счет обращений. При этом адреса меняются циклически от О до

Возможно переполнение памяти или обращение за информацией к опрошенной ячейке.

При этом трансформатор матрицы 1 не перемагничивается и отсутствие напряжения на нем служит соответствующим сигналом во внешние цепи. Так как в любом случае (переполнение, опрос Овободнои ячейки) дещифратор в конце цикла оказывается подготовленным к опросу следующей ячейки, необходимо принять меры для возврата схемы в исходное состояние. Для этого в дешифраторах 2 и 3

есть дополнительные 0|бмотки и дополнительная ступень дешифрации, связанные с логической схемой 5. При отсутствии напряжения на выходе трансформатора во время обращ,ения к нему ток дешифрации проходит по дополнительной обмотке, что приводит к выбору шины с номером на единицу меньшим.

Полупроводниковые ключи на выходах дешифраторов (см. ,фиг. 3) служат для формирования (Необходимого тока к вьгбранной шине.

Предмет изобретения

Устройство управления буферной памяти, содержащее :матрицу числовых трансформаторов, магнитный дешифратор записи, малнитный дешифратор считывания, магнитный шифратор и (Схемы «И, отличающееся тем, что, с целью расширения функциональных возможностей устройства, сердечники шифратора и матрицы числовых трансформаторов последовательно прошиты соответствующими выходными шинами ма(Лнилного дешифратора заниси и магнитного дешифратора считывания, а выходные 0|бмоТ(Ки сердечников магнитного шифратора, подключенные через схемы «И к источнику сигнала записи, соединены со

входными обмотками ма лнитного дешифратора записи, выходные обмот1ки сердечников ма(лнитного шифратора, подключенные через схемы «И к источнику сигнала считывания, соединены со входными обмотками магнитного дешифратора считывания.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПРОГРАММНОЕ УСТРОЙСТВО ДЛЯ ВЫЧИСЛИТЕЛЬНОЙМАШИНЫ | 1969 |

|

SU254204A1 |

| УСТРОЙСТВО для СЕЛЕКТИВНОГО ВЫВОДА ИНФОРМАЦИИ ИЗ ПРОВОЛОЧНЫХ ИСКРОВЫХ КАМЕР | 1967 |

|

SU202581A1 |

| УСТРОЙСТВО для УПРАВЛЕНИЯ ЗАПОЛ\ИНАЮЩИМБЛОКОМ | 1970 |

|

SU272372A1 |

| Управляющий автомат цифрового устройства числового управления | 1972 |

|

SU507153A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1970 |

|

SU275139A1 |

| РЕВЕРСИВНЫЙ ДЕШИФРАТОР | 1969 |

|

SU247351A1 |

| ВСЕСОЮЗНАЯ I | 1973 |

|

SU377867A1 |

| ЬИЬЛИО', ЕКА | 1973 |

|

SU365707A1 |

| БУФЕРНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1972 |

|

SU341083A1 |

| АССОЦИАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1971 |

|

SU310308A1 |

Опрос дешисрра тора считывания 7 (записи 6)

Подготобка де ши зраторасчитывания 9 (запаси 8)

Опрос шисрраторо Ю

пп

пп

пп

Фиг. 7

г-УЫй

Hrt--Л

Авторы

Даты

1972-01-01—Публикация