ДВУХСТУПЕНЧАТЫЙ ДЕШИФРАТОР С КОНТРОЛЕМ

| название | год | авторы | номер документа |

|---|---|---|---|

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1970 |

|

SU277852A1 |

| Постоянное запоминающее устройство | 1976 |

|

SU716065A1 |

| Цифровое устройство числового программного управления | 1971 |

|

SU441858A1 |

| РЕВЕРСИВНЫЙ ДЕШИФРАТОР | 1969 |

|

SU247351A1 |

| Устройство для контроля адресных токов блоков памяти | 1975 |

|

SU562868A1 |

| Запоминающее устройство типа 2,5 д | 1981 |

|

SU999105A1 |

| УСТРОЙСТВО для ВЫБОРКИ ИНФОРМАЦИИ из постоянного ТРАНСФОРМАТОРНОГО ЗАПОМИНАЮЩЕГО | 1973 |

|

SU377868A1 |

| Дешифратор для запоминающего устройства матричного типа | 1972 |

|

SU497728A1 |

| Оперативное запоминающее устройство | 1974 |

|

SU495712A1 |

| Устройство для обмена информацией | 1980 |

|

SU955014A1 |

1

Предлагаемый дешифратор относится к устройствам вычислительной техники и может быть использован в цифровых специализироваииых и уииверсальных вычислительных системах.

Известны различные двухступенчатые дешифраторы, основное оборудование которых составляют диоды и различные ключи. Надежность таких дешифраторов определяется надежностью входящих в их состав элементов. Известиы методы обнаружения неисправностей запоминающего устройства (ЗУ) с дешифратором в адресной системе, которые предполагают введение избыточиых разрядов в числовых линейках ЗУ и наличие устройств контроля кода ЗУ (в нростейшем случае но признаку четности). Известные устройства контроля работы ЗУ не позволяют установить место возиикновення неисправности, что приводит к большим затратам времеин иа локализацию неисиравности в том случае, если обнаружена ошибка в коде.

В процессе работы дешифратора, например в составе МОЗУ, возможно возникновение следующих неисправностей: обрыв в схеме формирователя адресного тока, обрыв (или замыкание) ключей иервой стуиени выбора числовой лииейки магнитного наконителя, обрьш (или замыкание) диода диодной дешифрирующей матрицы. В случае возникновения неисправности типа «оорыв исчезает возможность обращения к нужной числовой линейке (нужному выходу дешифратора), а в случае возиикиовения неисправности типа «замыкание

появляется опасность одновременного выбора нескольких числовых линеек (выходов дешифратора).

Целью предлагаемого изобретения является создание дешнфратора, обеспечнвающего

обнаружение и локализацию ненснравностей в нем как типа «обрыв, так тииа «замыкание. Применение такого дешифратора совместно с известными устройствами контроля кодов позволяет обеспечить высокую достоверность

записи и считывания информацни, наиример в МОЗУ, и сократить время, затрачиваемое на отыскание неисправностей.

Сущность тзобретеиия заключается в том, что выявление ненсиравиости тииа «обрыв

производится но отсутствию тока в адресно цен, а локал за и я не снрав юст производ тся путем носледовательной ироверк отдельных участков иенснравной адресной . Выявление неисправност типа «замыкание в

системе ключей выбора числовой линейки ЗУ производится путем сравнения адреса выбираемого ключа из регистра адреса с фактичесК 1м наличием 1 Л пульса ia выходе да 1ного клкзча в первой стунен. В 51явление н локал зацня пенсправност типа «замыкаипе днодов дешифрирующей матрицы производится путем подключения к ним дополнительного источника импульсного напряжения обратной полярности и индикации соответствуюп;его адреса при наличии недопустимо больп.ю-Г{) обратного тока, протекающего через диод.

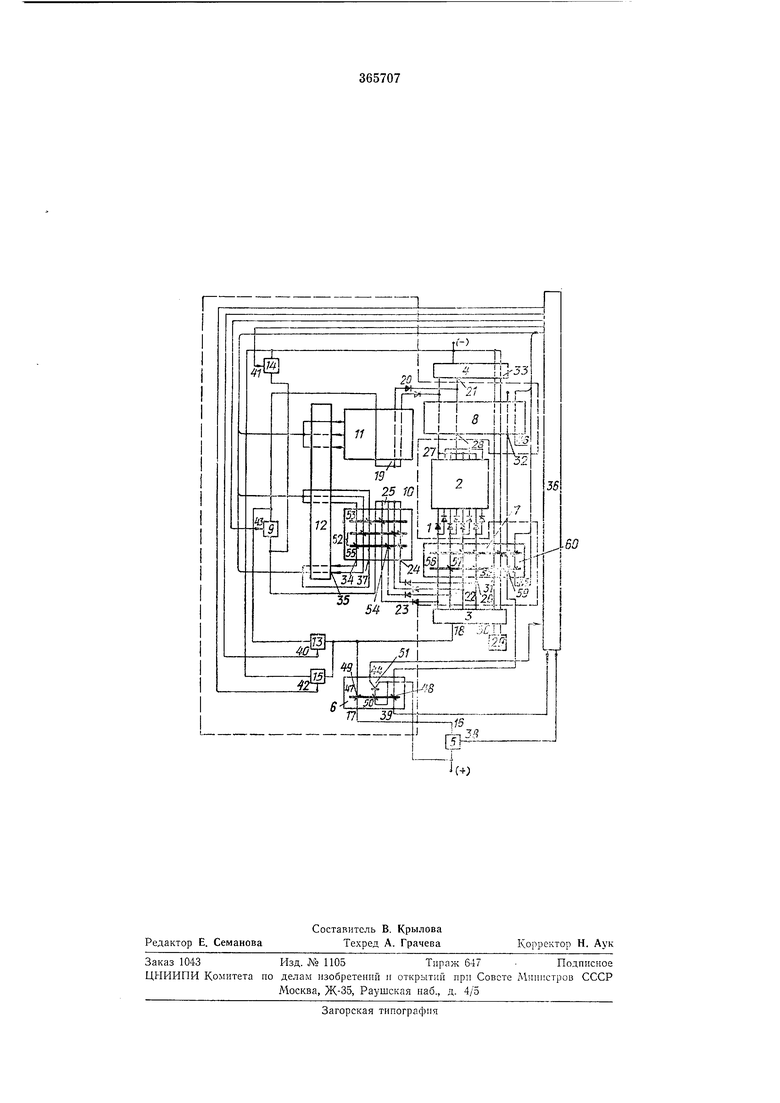

На чертеже изобралсена схема нереверсивного двШ|ифратора (например, дешифратора адреса МОЗУ с раздельными адресными шинами записи и считывания).

Предложенное устройство состоит из диодной матрицы (диодов) (тхп) 1, выходы которой (тХп выходов) подключены, например, к числовым линейкам магнитного накопителя 2, первого блока 3 первой ступени дешифрации, второго блока 4 первой ступени дешифрации, формирователя 5 адресного тока, схемы 6 выявления обрыва адресной цепи, схем 7 и 8 сравнения адресов первой ступени импульсного источника 9 напряжения, схем 10 и У/ щифрации адреса первой ступени, схемы 12 индикации адреса и ключей 13-15. Выход 16 формирователя 5 подключен ко входу подготовки 17 схемы 6, далее ко входу 18 блока 3, через ключ 13 - к объединенным п шинам 19 схемы //, после чего через п диодов 20 подключен к п выходам 21 блока 4.

Блок 5 имеет т выходов 22, которые через диоды 23 подключены к т шинам 24 схемы 10, объединенные концы 25 которых подключены через КЛЮЧИ 14 к отрицательному полюсу источника питания. Выходы 22 блока 3 также подключены к т входным шинам 26 схемы 7, после чего - к т npynnaiM, объединенных по п диодов, п выходов 27 1магйитного накопителя 2 подсключены к п входным .ш-инам 28 схемы 8, далее - к п выходам 21 дешифратора блока 4.

Вход 18 блока 3 подключен через ключ 15 к отрицательному полюсу источника питания.

Регистр адреса 29 подключен ко входам 30 блока 3, ко входам 31 схемы 7, ко входам 32 схемы 8 и ко входам 33 блока 4.

Выходные шины 34 схем 10 и 11 подключены к шипам 35 схемы 12 (в том числе и через промежуточные усилители), объедипеппый конец которых подключен к устройству управления 36. Выходные шины 37 схем 10 и 11 подключены непосредственно к устройству управления 36.

Вход 38 запуска формирователя 5 и вход 39 запуска схемы 6 подключепы к устройству управления 36.

Устройство управления 36 подключено ко входам 40-42 ключей 13-15 соответстенно, а также ко входу 43 источника 9.

Выход 44 схемы 6, а также выходы 45 и 46 схем 7 и S подключены к устройству управления.

Схема 6 выявления обрыва адресной цепи состоит из магнитного сердечника 47 с ППГ, имеющего обмотку 48 зануска, обмотку подготовки 49 и выходную обмотку 50, которая подключена ко входу транзистора 51.

Схема 10 состоит из М (где M-log2/«) магнитных (с непрямоугольной петлей гистерезиса) сердечников 52 и одного магнитного (с непрямоугольной петлей гистерезиса) сердечника 53, имеющих обмотки 54 запуска и выходные обмотки 55 (аналогично выполнена и схема 11).

Схема 7 состоит из /И магнитных (с прямоугольной петлей гистерезиса) сердечников 56 с согласно включенными обмотками 57 и 58, со встречно (относительно обмоток 57 и 58) включенными обмотками 59 и выходными обмотками 60 (аналогично выполнена и схема 8).

Рассмотрим работу предложенного устройства в случае возникновения неисправности типа «замыкание.

В процессе работы дещифратора возможно появление замыкания в блоках 3 и 4 н ъ диодах /. Замыкание диода / обнаруживается по наличию у диода недопустимо малого обратного сопротивления. Для этого импульс напряжения от источника 9 прикладывается к диодам 1, причем этот импульс прикладывается в такой момент, когда отсутствует импульс тока, формируемый формирователем 5. Внутреннее сопротивление источника 9 в остальное время (когда он не вырабатывает импульс напряжения) велико (запертый транзистор). При этом через замкнутый диод 1 потечет импульс тока по следующей цепи: положительный выход источника 9 - схема // - диод 20 - схема S - магнитный накопитель 2 - неисправный диод 1 - схема 7 - диод 23 - схема 10 - отрицательный выход источника 9. Импульс тока поступит на вполне определенные шины 24 схем 10 и 11, соответствующие адресу неисправного диода 1, в результате чего определенные сердечники 52 и 53 схем 10 и 11 перемагнитятся и на их выходных обмотках 55 сформируется код, соответствующий адресу замкнутого диода 1, который с шин 34 схем 10 н 11 поступает на шины 35 схемы 12, после чего в виде сигнала «сбой - на }стройство управления 36.

Таким образом, введение источника 9 позволяет решить задачу выявления замыкания диода 1, а введение схем 10 и 11 - задачу локализации замкнутого диода /. Затраты оборудо1вания при тХп 1024 составляет ориентировочно 6% от всего дешифратора, причем с увеличением тХп этот процент уменьшается. Обмотки 54 на сердечниках 52 расположены таким образом, чтобы при поступлении импульса тока на любую из шин 24 схем 10 и // перемагнитнлись те из 2М сердечников 52, которые соответствуют 2М - разрядному двоичномуадресузамкнутогодиода( logzm Iog2«).

Введение сердечника 53 в схемы 10 и 11 обусловлено необходимостью формирования сигнала «сбой при замыкании диода 1, соответствующего нулевым выходам обоих блоков первой ступени дешифрации, двоичные адреса которых содержат н}ли во всех первых илп вторых М разрядах. При это.м сигпал «сбой с выходных щин 37 схем 10 и 11 иоступает пряМО на устройство управления 36, минуя схему 12.

Замыкание ключей в блоках 3 (4) сонровождается растеканием тока от формирователя 5 по нескольким шинам 28 (или 26) илн протеканием тока через ключ несоответствующий адресу выбираемой числовой линейки магнитного наконителя 2.

Схемы 7 и S обеспечивают выявление замыкания ключей блоков 3 и 4 соответственно и формирование сигнала «сбой, поступающего па устройство унравления 36. Для этого при записи на ключи адрес (в двоичном коде) записывается и на магнитные сердечники 56 схем 7 и 5, в результате чего определенные сердечники 56 оказываются перема гничеппыми (подготовленными) в определенное состояние. Обмотки 58 расположены на сердечникках 56 по схеме шифрации таким образом, что при открывапии нужного ключа блока 3 (4) импульс тока от формирователя проходит по обмоткам 58 всех (и только их) ранее «подготовленных сердечников 56. При протекании тока через ключ блока 3 (4), несоответствующий нужному адресу, возможны два случая: протекание тока по обмоткам 58 всех ранее «подготовленных сердечников 56, а также по обмоткам 58 некоторых «неподготовленных сердечников 56; протекание неполного тока по обмоткам 58 некоторых из ранее «подготовленных сердечников 56.

Для выявления несовпадения адреса выбираемой числовой линейки с нужным адресом во втором случае одновременно с запуском формирователя 5 но обмоткам 59 (включенным встречно относительно обмоток 57 и 58) сердечников 56 пропускается импульс тока от устройства управления 36, причем его длительность меньще длительности импульса тока от формирователя 5, в результате чего импульс тока от формирователя полностью «перекрывает импульс тока, протекающий по обмоткам 59 сердечников 56, по времени и равен по амплитуде. При этом те «подготовленные сердечники 56, по обмоткам 57 которых протекает неполпый ток от формирователя 5, перемагнитятся в новое состояние за счет тока, протекающего по обмоткам 59.

При протекании тока по обмоткам 57 «неподготовленных сердечников 56, эти сердечники также перемагпитятся в повое состояние, так как длительность «перекрытого нмпзльса (по обмотке 59) меньше длительности импульса тока от формирователя 5 (по обмотке 57).

Как в первом, так и во втором перемагничивание хотя бы одного сердечника 56 в новое состояние сопроволадается появлением 3. д. с. на его обмотке 60, что соответствует подаче сигнала «сбой па устройство управления 36 со схем 7 или 8.

Таким образом, введение схем 7 и S позволяет решить задачу выявления ненсправности типа «замыкание в ключах первого 3 и второго 4 блоков первой ступени дешифрации.

Локализация замкнутого ключа в блоках 3

(4) осуществляется после возникновения сигнала «сбой на обмотках 60. С этой целью устройство управления 36 органнзует систему тактов, проверяюи,ую наличие проводящей

ветви в блоках 3 (4) без покрытия (нодготовки) ключей в первой ступени. Сначала нз управляющего Зстройства 36 поступают сигналы по входам 38 и 41. Адрес неисправного ключа в блоке 3 при этом фиксируется на схеме 12

с иомощью схемы 10. Затем из устройства управления 36 поступают сигналы по входам 38 и 40. Адрес неисправного ключа в блоке 4 при этом фиксируется па схеме 12 с помощью схемы 11.

Рассмотрим работу предложенного устройства в случае возникновения неисправности типа «обрыв.

Для выявлеиия обрыва одновременно с формированием импульса формирователем 5

па вход 39 схе.мы 6 подается пмпульс тока от управляющего устройства 36, причем такой, чтобы он полностью «перекрывался импульсом тока от формирователя 5. Прп наличии импульса тока от формирователя 5 схема 6 не срабатывает, что свидетельствует об отсутствии обрыва в адресной цепи. Отсутствие же его является причиной срабатывания схемы 6, так как сердечник 47 перемагничивается импульсом тока по обмотке 48. При этом сигнал «обрыв поступает с выхода 44 схемы 6 на устройство управления 36, которое прекращает нормальную работу и приступает к выработке следующей последовательпостп контрольных управляющих сигналов но входам 42, 40, 41, пз которых сопровождается подачей сигналов запуска на вход 38 формпрователя 5 н на вход 39 схемы 6, а при необходимости и возбуждение.м регистра адреса 29.

По сигналу входа 42 открывается ключ 16, и формирователь 5 подключается непосредственно к отрицательному полюсу источннка питания. Если формирователь 5 исправен, то его выходной импульс поступает на вход подготовки 17 схемы 6 п запрещает запуск этой схемы.

Таким образом, транзистор 51 схемы 6 не срабатывает, что свидетельствует об исправпости формирователя 5.

По сигналу с входа 40 открывается ключ

13, и организуется новая цепь для выходного нмпульса формирователя 5: ключ 13 - схема 11 - диоды 20 - блок 4. Наличие тока в этой цепп (что выявляется схемой 6) свидетельствует об исправности подготовленного ключа в блоке 4. Отсутствие тока свидетельствует об обрыве ключа в блоке 4, номер которого записан в регистре адреса 29.

По сигналу с входа 41 открывается ключ 14,

И оргаиизуется следующая цепь выходного импульса формирователя 5: блок 3 - диоды 23 - схема W ключ 14. Наличие пмпульса тока в этой цепп свидетельствует об исправности иодготовленпого ключа в блоке 3.

Если при подаче сигпалов по входам 42, 40

и 41 во всех случаях схема 6 не фиксировала обрыв, то делается вывод об обрыве диода /, адрес которого записан в регистре адреса 29. Таким образом, введение схемы 6 и ключей 13, 14 и 15 позволяет решить задачу выявления и локализации обрыва пепи дешифратора. На базе описанного нереверсивного дешифратора легко построить в реверсивный дешифратор с такими же возможностями путем удвоения блоков источника 9, схем 6-8, ключей 13-15 и диодов 20 и 23 и обмоток 54 иа сердечниках 52 и 55 схем 10 и //. Кроме того, в реверсивных дешифраторах выдвигается дополнительное требоваиие к источникам 9 напряжения, заключающееся в TOIM, чтобы источники не имели обш,1х точек с источником питания формирователей 5. Выдвинутое требоваиие легко выполиить, применив в качестве источников изолированные друг от друга и от источника иитания формирователей 5 вторичные обмотки имнульсных трансформаторов.

Предмет изобретения

отличающийся тем, что, с целью автоматической локализации места неисиравиости типа «замыкание, первый выход дополдительного источника импульсного питания через иервую схему шифрации и т дополнительных диодов

подключен к выходам соответствующих ключей первого блока первой ступени дешифрации и через один ключ - к входу основпого источника питания, второй выход дополнительного источника импульсного питания через п дополнительных диодов и вторую схему шифрации подключен к выходам соответствующих п ключей второго блока первой ступени дешифрации и через другой ключ - к выходу основного источника питаиия, выходы обеих схем шифрации подключены ко входам индикатора.

первой ступени дешифрации через одновходовую схему контроля, выход которой подключен к устройству управления.

Авторы

Даты

1973-01-01—Публикация