Изобретение относится к области вычислительной техники, в частности, к области запоминающих устройств.

Известны дешифраторы для запоминающих устройств, содержащих матрицы сердечников, прошитых адресными шинами, в которые включены диоды, источник питания и формирователи тока записи и считывания, подключенные через КЛЮЧИ к адресным шинам.

В предложенном дешифраторе ключи выполнены в виде переключателей тока, работающих на принципе распределения тока, а выходы разноименных формирователей объединены и подключены к источнику питания.

Это упрощает дешифратор.

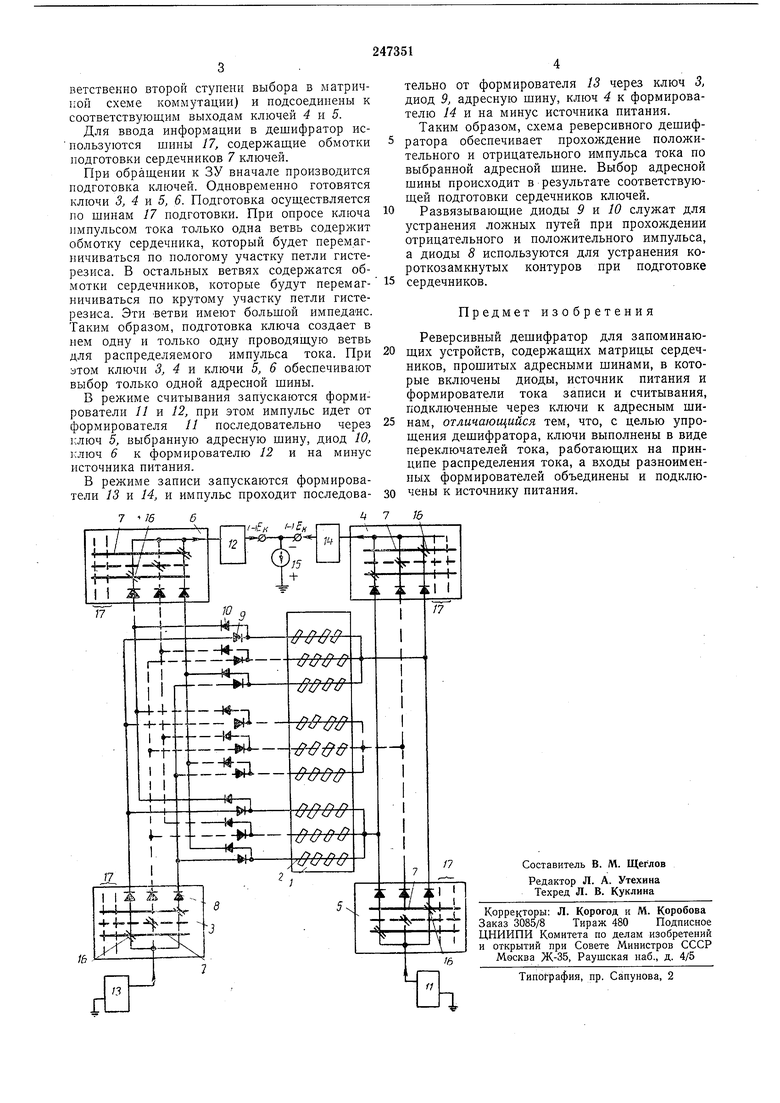

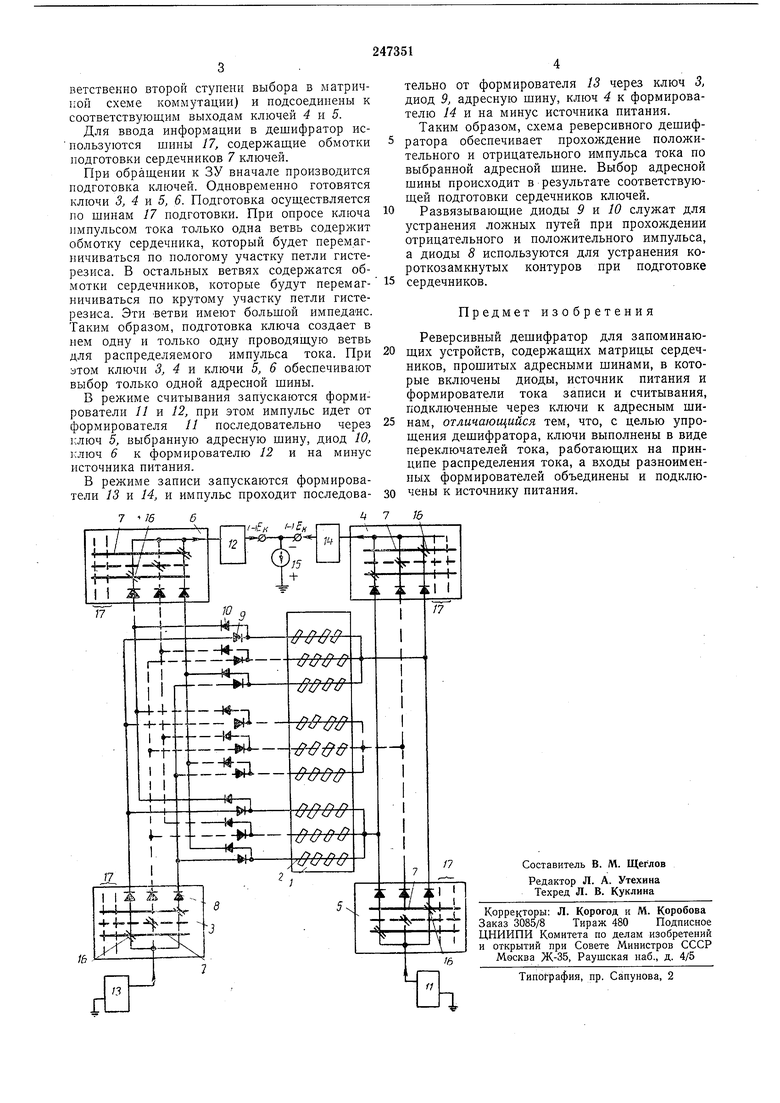

На чертеже показано описываемое устройство.

Оно содержит матрицу 1 МОЗУ с линейной выборкой и одной адресной шиной на число, адресную шину 2 с сердечниками матрицы МОЗУ, КЛЮЧИ 3-6 на сердечниках с ППГ, магнитные сердечники 7 ключей, 4 п штук по п в каждом ключе (п - число адресов, МОЗУ), диоды 8 в ключах (п штук в каждом ключе), диоды 9 матрицы записи (пХп штук), диоды 10 матрицы считывания («Хп штук), формулирователи 11-14 тока записи и считывания, источник питания 15, многовитковые (распределяющие) обмотки 16 на сердечниках и щины 17 подготовки сердечников ключей.

На чертеже показана схема реверсивного дешифратора и его подключение к матрице 1 МОЗУ с линейной выборкой на п чисел, содержащей по одной адресной шине 2 на число. Схема содержит четыре ключа 3-6 на магнитных сердечниках 7 с ППГ и диодах 8, выполненные по принципу распределения тока, матрицу (пХп) из диодов 9 для коммутации импз льсов тока записи, матрицу «Х« из диодов 10 ДЛЯ коммутации импульсов тока считывания и четыре импульсных формирователя тока 11-14, через которые схема подключается к источнику питания 15.

Ключи 3-6 представляют собой разветвленную цепь, каждая ветвь которой содержит многовитковую обмотку 16 магнитного сердечника и диод 8. В ключах 5 и 5 диоды подключены к обмоткам анодами, а в ключах 4 и 6 - катодами. Ключи 3 н 4 образуют две ступени выбора адресной шины при записи, а КЛЮЧИ 5 Н 6 - при считывании. Выходы ключа 3 подключены к анодам диодов 9,

а к катодам диодов 9 подсоединены адресные шины. К этим же точкам подсоединены аноды диодов 10. Катоды диодов 10 подсоединены к выходам ключа 6. Вторые концы адресных шин объединены в п групп (соответствекно второй ступени выбора в матричной схеме коммутации) и подсоединены к соответствующим выходам ключей 4 и 5.

Для ввода информации в дешифратор используются шины 17, содержащие обмотки подготовки сердечников 7 ключей.

При обращении к ЗУ вначале производится подготовка ключей. Одновременно готовятся ключи 3, 4 м 5, 6. Подготовка осуществляется по шинам 17 подготовки. При опросе ключа импульсом тока только одна ветвь содержит обмотку сердечника, который будет перемагпичиваться по пологому участку петли гистерезиса. В остальных ветвях содержатся обмотки сердечников, которые будут перемагничиваться по крутому участку петли гистерезиса. Эти ветви имеют большой импеданс. Таким образом, подготовка ключа создает в нем одну и только одну проводящую ветвь для распределяемого импульса тока. При этом ключи 3, 4 и ключи 5, 6 обеспечивают выбор только одной адресной щины.

В режиме считывания запускаются формирователи 11 и 12, при этом импульс идет от формирователя 11 последовательно через ключ 5, выбранную адресную шину, диод 10, ключ 6 к формирователю 12 и на минус источника питания.

В режиме записи запускаются формирователи 13 и 14, и импульс проходит последова7 /5

тельно от формирователя 13 через ключ 3, диод 9, адресную шину, ключ 4 к формирователю 14 и на минус источника питания.

Таким образом, схема реверсивного дешифратора обеспечивает прохождение положительного и отрицательного импульса тока по выбранной адресной шине. Выбор адресной шины происходит в результате соответствующей подготовки сердечников ключей.

Развязывающие диоды 9 к 10 служат для устранения ложных путей при прохождении отрицательного и положительного импульса, а диоды 8 используются для устранения короткозамкнутых контуров при подготовке

сердечников.

Предмет изобретения

Реверсивный дешифратор для запоминающих устройств, содержащих матрицы сердечников, прошитых адресными шинами, в которые включены диоды, источник питания и формирователи тока записи и считывания, подключенные через ключи к адресным шинам, отличающийся тем, что, с целью упрощения дешифратора, ключи выполнены в виде переключателей тока, работающих на принципе распределения тока, а входы разноименных формирователей объединены и подключены к источнику питания.

7

| название | год | авторы | номер документа |

|---|---|---|---|

| Дешифратор для запоминающего устройства матричного типа | 1972 |

|

SU497728A1 |

| ЬИЬЛИО', ЕКА | 1973 |

|

SU365707A1 |

| Реверсивный дешифратор | 1976 |

|

SU604151A1 |

| УСТРОЙСТВО для ПАРАЛЛЕЛЬНОГО СУММИРОВАНИЯДВУХ ЧИСЕЛ | 1970 |

|

SU268498A1 |

| ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО | 1969 |

|

SU255993A1 |

| ВЫЧИСЛИТЕЛЬНО-ЛОГИЧЕСКОЕ УСТРОЙСТВО | 1973 |

|

SU393741A1 |

| Устройство для управления накопителем | 1979 |

|

SU773737A1 |

| Логическое запоминающее устройство | 1971 |

|

SU443411A1 |

| Управляющий автомат цифрового устройства числового управления | 1972 |

|

SU507153A1 |

| ЦИФРОВОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО НА ПОЛНОТОЧНОМНАКОПИТЕЛЕ | 1971 |

|

SU289514A1 |

Даты

1969-01-01—Публикация