1,

Изобретение относится к области радиотехники и может быть использовано в пересчетных устройствах вычислительной техники, требующих высокого быстродействия.

Известен двоичный счетчик импульсов, каждый разряд которого выполнен на основе Дтриггера на шести многовходовых логических элементах «И-НЕ/ИЛИ-НЕ потенциального типа, имеет выход импульса переноса и содержит элемент, на выходе которого образуется импульс, передний и задний фронты которого совпадают во времени с задним фронтом импульсов счета.

Однако в известном устройстве от разряда к разряду увеличивается задержка выходных импульсов разрядов по отношению к счетным импульсам, что уменьшает быстродействие устройства.

Цель изобретения - расширение функциональных возможностей счетчика.

Достигается это тем, что выход вышеуказанного элемента каждого разряда соединен со свободным счетным входом последующих разрядов.

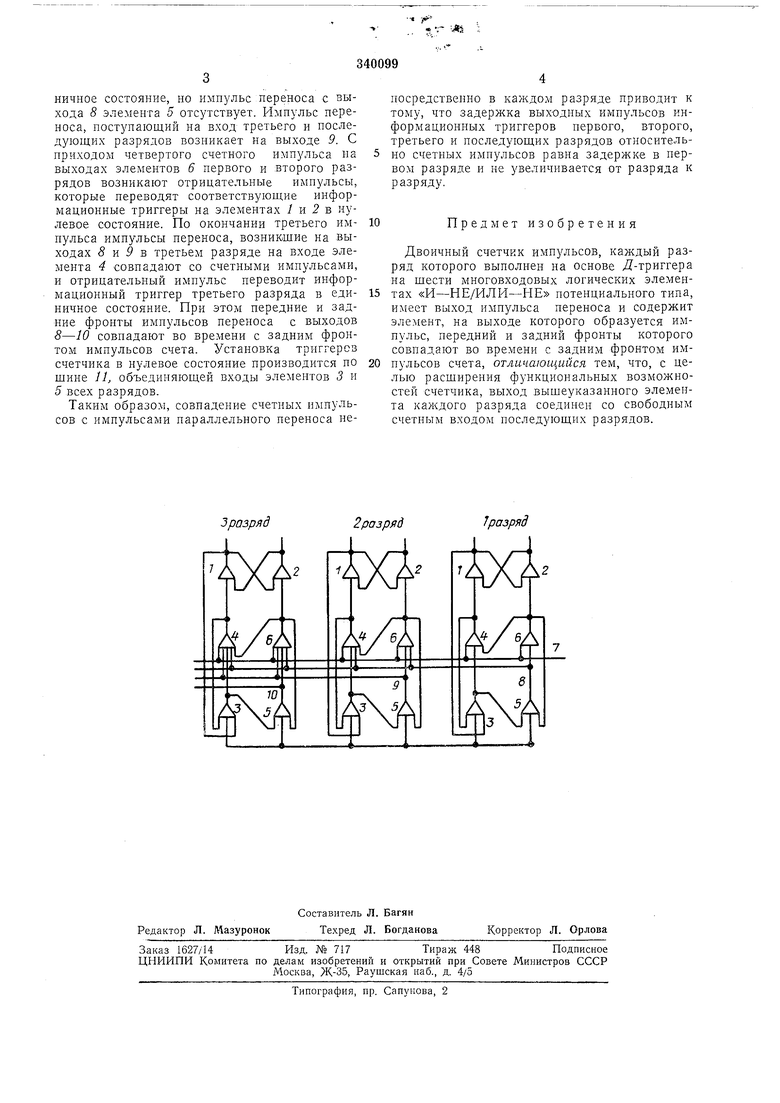

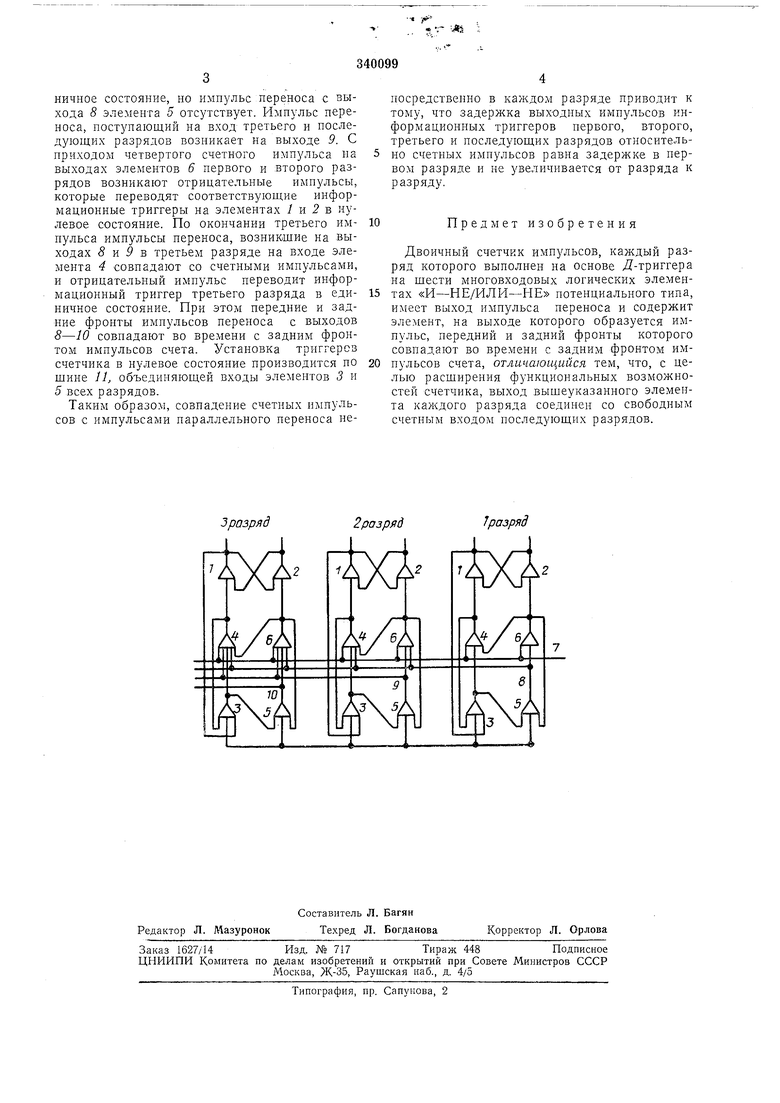

На чертеже представлена функциональная блок-схема устройства на примере трехразрядного двоичного счетчика.

ИЛИ-НЕ потенциального типа. Выход элемента 5 каждого разряда соединен со свободным счетным входом последующих разрядов. Вход 7 счетных импульсов соединен со счетными входами элементов 4 и 6 всех разрядов. Элементы / и 2 каждого разряда представляют собой информационный триггер.

Положим, все информационные триггеры находятся в нулевом положении. При поступлении на вход 7 первого счетного импульса на выходе элемента 4 первого разряда возникает отрицательный импульс, который переводит информационный триггер первого разряда в единичное состояние. При этом импульс переноса отсутствует, так как на выходе 8 элемента 5 наблюдается потенциал низкого уровня. С приходом второго счетного импульса на .выходе элемента 6 возникает отрицательный импульс, который переводит информационный триггер первого разряда в нулевое состояние. При этом на выходе 8 элемента 5 устанавливается высокий потенциал, который поступает на входы второго и третьего разрядов. Во втором разряде на входе элемента 4 происходит совпадение счетного импульса с импульсом переноса. Отрицательный импульс устанавливает информационный триггер на элементах / и 2 в единичное состояние. Третий счетный импульс снова переводит инничное состояние, но имнульс переноса с выхода 8 элемента 5 отсутствует. Импульс переноса, поступающий на вход третьего и последуюш,их разрядов возникает на выходе 9. С приходом четвертого счетного импульса на выходах элементов 6 первого и второго разрядов возникают отрицательные нмнульсы, которые переводят соответствующие информационные триггеры на элементах / и 2 в нулевое состояние. По окончании третьего импульса импульсы переноса, возникшие на выходах 8 и 9 в третьем разряде на входе элемента 4 совпадают со счетными импульсами, и отрицательный импульс переводит информационный триггер третьего разряда в единичное состояние. При этом передние и задние фронты импульсов переноса с выходов 8-10 совпадают во времени с задним фронтом импульсов счета. Установка триггеров счетчика в нулевое состояние производится по щине 11, объединяющей входы элементов 3 и 5 всех разрядов.

Таким образом, совпадение счетных импульсов с импульсами параллельного переноса не340099

посредственно в каждом разряде приводит к тому, что задержка выходных импульсов информационных триггеров нервого, второго, третьего и последующих разрядов относительно счетных импульсов равна задержке в нервом разряде и не увеличивается от разряда к разряду.

Предмет изобретения

Двоичный счетчик импульсов, каждый разряд которого выполнен на основе Д-триггера на шести многовходовых логических элементах «И-НЕ/ИЛИ-НЕ нотенциального типа, имеет выход импульса переноса и содержит элемент, на выходе которого образуется импульс, передний и задний фронты которого совпадают во времени с задним фронтом имнульсов счета, отличающийся тем, что, с целью расширения функциональных возможностей счетчика, выход вышеуказанного элемента каждого разряда соединен со свободным счетным в.ходом последующих разрядов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Счетное устройство с предварительной уставкой кода | 1982 |

|

SU1027832A1 |

| Многовходовый сигнатурный анализатор | 1986 |

|

SU1383362A1 |

| Устройство программируемой задержки импульсов | 1980 |

|

SU953717A2 |

| Устройство для упорядочивания чисел | 1983 |

|

SU1144103A1 |

| Устройство программируемой задержки импульсов | 1980 |

|

SU875608A1 |

| Функциональный преобразователь | 1984 |

|

SU1211756A1 |

| Цифровой интегратор с контролем | 1975 |

|

SU540269A1 |

| Устройство для программного управления | 1991 |

|

SU1800445A1 |

| Устройство для сравнения чисел с допуском | 1985 |

|

SU1251067A1 |

| Счетчик импульсов | 1978 |

|

SU746949A1 |

разряд2разряд разряд

k -k k

4М

4Х/

Даты

1972-01-01—Публикация