- микроопераций, 1.2 - признака формата, 1.3 - времени задержки, 1.4 - адреса безусловного перехода (передачи управления); счетчик 2 адреса; регистр 3 микроопераций; коммутатор 4 направления приема адреса; триггер 5 режима; шифратор 6 направления приема управления; дешифратор 7 направления передачи управления; счетчик 8 времени задержки; элемент 9 запрета; шину 10 микроопераций; первый 11, второй 12, третий 13 и четвертый 14 элементы ИЛИ, первый 15 и второй 16 элементы И; входы 17.1 и 17.2 синхронизации; входы 6.1-6.1-1 инициализации данного модуля другими модулями системы; вход 6.I инициализации модуля от внешнего устройства управления; выходы 7.1-7.d передачи управления дру- тим модулям и соответствующие связи. Новым в устройстве является введение дешифратора направления передачи управления, шифратора направления приема управления, коммутатора направления приема адреса, триггера режима, элемента запрета, первого элемента ИЛИ, второго элемента ИЛИ, третьего элемента ИЛИ, четвертого элемента ИЛИ, первого и второго элементов И и обусловленных ими связей. 5 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| МОДУЛЬНОЕ УСТРОЙСТВО ДЛЯ ПРОГРАММНОГО УПРАВЛЕНИЯ | 1997 |

|

RU2112269C1 |

| Микропрограммное устройство управления модуля распределенной параллельной вычислительной системы | 1985 |

|

SU1252775A1 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1142832A1 |

| Модульное устройство для программного управления и контроля | 1988 |

|

SU1647519A1 |

| Устройство для программного управления | 1988 |

|

SU1500994A1 |

| Микропрограммное устройство управления модуля вычислительной системы | 1982 |

|

SU1034037A1 |

| Устройство для управления и микродиагностики | 1981 |

|

SU968815A1 |

| Перестраиваемый микропрограммный процессор | 1981 |

|

SU983713A1 |

| Мультимикропрограммная управляющая система с контролем и восстановлением | 1988 |

|

SU1704147A1 |

| Микропрограммное устройство управления | 1981 |

|

SU1015383A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении систем управления технологич.ескими процессами. Целью изобретения является расширение области применения модульного устройства за счет введения функции передачи управления другим модулем и приема управления как от внешнего устройства управления, так и от других модулей системы; введения входов и выходов, обеспечивающих организацию интерфейса при построении управляющей системы с требуемым объемом памяти микрокоманд. При этом обеспечивается возможность агрегатирова- ния и наращивания управляющей памяти в зависимости от сложности алгоритма управления. Модульное устройство содержит блок 1 памяти микрокоманде выходами 1.1

Изобретение относится к области автоматики и вычислительной техники и может быть использовано при построении систем управления технологическими процессами.

Целью изобретения является расширение области применения устройства, называемого теперь модульным устройством для программного управления (МПУ), за сет; а) введения функции передачи управления другими модулями, и приема управления как от внешнего устройства управления, так и от других модулей системы; б) введения входов и выходов, обеспечивающих организацию физических линий связи (интерфейса) при построении управляющей системы с требуемым объемом памяти микрокоманд.

Поставленная цель достигается тем, что в устройство для программного управления, содержащее счетчик времени задержки, регистр микроопераций, блок памяти микрокоманд, счетчик адреса, причем выход счетчика адреса соединен с адресным входом блока памяти микрокоманд, а выходы микроопераций и времени задержки блока памяти соединены соответственно с информационным входом регистра микрооперацией и счетчиком времени задержки, дополнительно введены: коммутатор направления приема адреса, триггер режима, шифратор направления приема управления, дешифратор направления передачи управления, элемент запрета, шина микроопераций, первый, второй, третий и четвертый элементы ИЛИ, первый, второй элементы И, причем группа входов инициализации устройства являются группой входов шифратора направления приема управления, выход которого соединен с младшими разрядами входа первого элемента ИЛИ и с группой информационных входов коммутатора направления приема адреса, выход адреса/номера модуля блока памяти микрокоманд соединен с второй

группой информационных входов коммутатора направления приема адреса, со входом второго элемента ИЛИ, с группой информационных входов дешифратора направления передачи управления, выход

которого является выходом передачи управления другим устройством системы, группа выходов признака формата блока памяти микрокоманд соединен со второй группой первого элемента ИЛИ, с

V-управляющим входом дешифратора направления передачи управления, с первым входом третьего элемента ИЛИ, с К-входом триггера режима, выход которого соединен со вторым входом третьего элемента ИЛИ, с управляющим входом элемента запрета, выход-регистра микроопераций соединен с информационным входом элемента запрета, выход которого соединен с шиной микроопераций, выход первого элемента ИЛИ соединен с прямым и инверсным управляющими входами коммутатора направления приема адреса, выход которого соединен с информационным входом счетчика адреса, выход первого элемента

ИЛИ и первый вход синхронизации устройства соединены соответственно с 1-входом и синхровходом IK-триггера режима, первый вход синхронизации устройства соединен с первым входом первого элемента И,

выход которого соединен с синхровходом и счетным входом счетчика времени задержки, второй вход синхронизации устройства является первым входом второго элемента И, выход которого соединен с синхровходом

регистра микроопераций, выход третьего элемента ИЛИ соединен со вторыми входами первого и второго элементов И, выход переноса счетчика времени задержки соединен со счетным и синхровходом счетчика адреса, параллельный выход счетчика времени задержки соединен с группой входов четвертого элемента ИЛИ, выход которого соединен с V-управляющим входом счетчика времени задержки, выход второго эле- мента ИЛИ соединен с V-управляющим входом счетчика адреса.

Сущность предлагаемого изобретения состоит в обеспечении возможности агре- гатирования и наращивания управляющей памяти в зависимости от сложности алгоритма управления с сохранением виртуальной (непрерывной) адресации микрокоманд, то есть построения дискретных сетевых структур управления. Эта воз- можность реализуется путем:

а) введения интерфейсных входов-выходов в каждом модуле. При выполнении модуля по технологии СБИС в одном корпусе эти входы-выходы реализуют внешние связи передачи управления между модулями;

б) введения формата микрокоманды, обеспечивающего адресацию ПЗУ не только внутри одного модуля, но и возможность последовательной передачи управления другим модулям системы.

Указанные усовершенствования позволяют размещать в управляющей памяти микропрограммы комплексных (объединен- ных) алгоритмов большой сложности, Жесткость адреса передачи управления между модулями несколько снижает гибкость микропрограммирования, однако при оптимальном агрегатировании комплексных алгоритмов этот недостаток неощутим. При этом сложность интерфейса обмена получается минимальной, т.к. для передачи управления между двумя модулями требуются две физические линии связи, передающие единичный сигнал. Таким образом, сложность интерфейсной шины С составит: С 2п, где п - число модулей в составе. Кроме того, реализация сущности предполагаемого изобретения указанным путем с использо- ванием технологии СБИС позволяет достичь технико-экономического эффекта, заключающегося в снижении числа корпусов микросхем, необходимых для реализации микропрограммы требуемой сложности. Оценка выигрыша дана в конце описания.

Суть новой функции и соответствующего режима работы устройства состоит в следующем. После выбора из блока памяти

микрокоманды передачи управления устройства переходит в режим анализа номера модуля, которому передается управление, активизации соответствующей линии связи и собственного отклонения. При этом код номера модуля с выхода блока памяти поступает на дешифратор направления передачи управления. Триггер режима по заднему фронту тактового импульса т переключится в нулевое состояние (это обеспечивается единичным состоянием признака формата данной микрокоманды), после чего на выходе дешифратора направления передачи управления возбудится соответствующая линия связи. Нулевое состояние триггера режима обеспечивает также отключение входов синхронизации данного модуля. С выхода дешифратора передающего модуля единичный сигнал поступит на один из входов шифратора направления приема управления соответствующего модуля. На выходе шифратора сформируется код адреса первой микрокоманды, триггер режима единичным сигналом с первого элемента ИЛИ переводится в единичное состояние, и через третий элемент ИЛИ произойдет открытие входов синхронизации данного модуля. Описанный процесс обеспечивает последовательный режим передачи управления между модулями по жесткому адресу. При этом схемная реализация обеспечивает объединение модулей в сетевую структуру по принципу каждый с каждым.

Сущность изобретения реализуется за счет введения совокупности следующих конструктивных признаков (новых элементов и новых связей), определя ющих соответствие заявляемого технического решения критерию Новизна :

- введение межмодульных связей через введенные дешифратор направления передачи управления и шифратор направления приема управления обеспечивает взаимодействие по принципу каждый с каждым,

- введение коммутатора направления приема адреса и его связей обеспечивает управление выбором адреса следующей микрокоманды. При этом возможно поступление адреса безусловной передачи из собственного блока памяти или одного из жестких адресов при приеме управления от других модулей;

- введение триггера режима с его связями необходимо для перевода модуля из режима ожидания приема управления в режим внутренней адресации и обратно. Кроме того, триггер режима обеспечивает открытие и закрытие элемента запрета;

- элемента запрета управляется сигналом состояния триггера режима и предназначен для передачи кода микрооперации из модуля в шину микроопераций;

- первый элемент ИЛИ предназначен для управления коммутатором направления запрета адреса и перевода триггера режима в единичное состояние при получении управления от любого модуля системы;

- второй элемент ИЛИ после появления на его входе ненулевого кода формирует единичный сигнал на выходе, которым переводит счетчик адреса в режим записи параллельным кодом;

-третий элемент ИЛИ после появления на одном из его входов единичного сигнала формирует сигнал открытия входов синхронизации модуля;

- четвертый элемент ИЛИ предназначен для управления режимом работы счетчика времени задержки. При наличии на его входе ненулевого кода на выходе элемента ИЛИ устанавливается единичный сигнал, поступающий на вход управления счетчика времени задержки, При этом счетчик работает в режиме счета, увеличивая свое содержимое на единицу. После полного заполнения регистра (код 11 ...1) последний обнуляется, вырабатывая единичный сигнал переноса. Нулевой код на входе четвертого элемента ИЛИ формирует нулевой сигнал на его выходе, переводящий счетчик времени задержки в режим записи параллельным кодом;

- первый элемент И пропускает первую серию тактовых импульсов г от внешнего генератора в случае наличия единичного сигнала на его втором входе;

- второй элемент И пропускает вторую серию тактовых импульсов Т2 сдвинутых относительно первой серии.

При использовании предлагаемого изобретения может быть получен положительный эффект, состоящий:

- в расширении области применения устройства за счет построения многомодульной управляющей системы с требуемым объемом памяти микропрограмм и последовательной передачей управления между модул я ми;

- в минимальных аппаратных затратах по числу требуемых модулей и сложности обменного интерфейса благодаря жестким адресам, используемым при передаче управления.

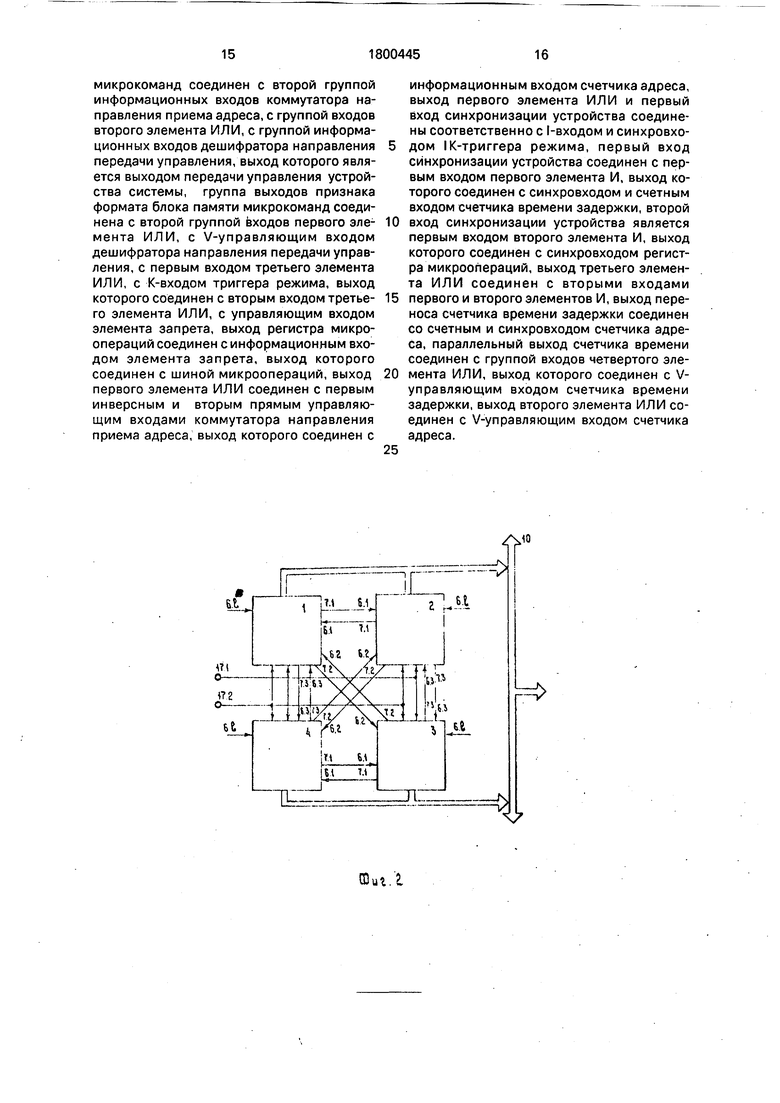

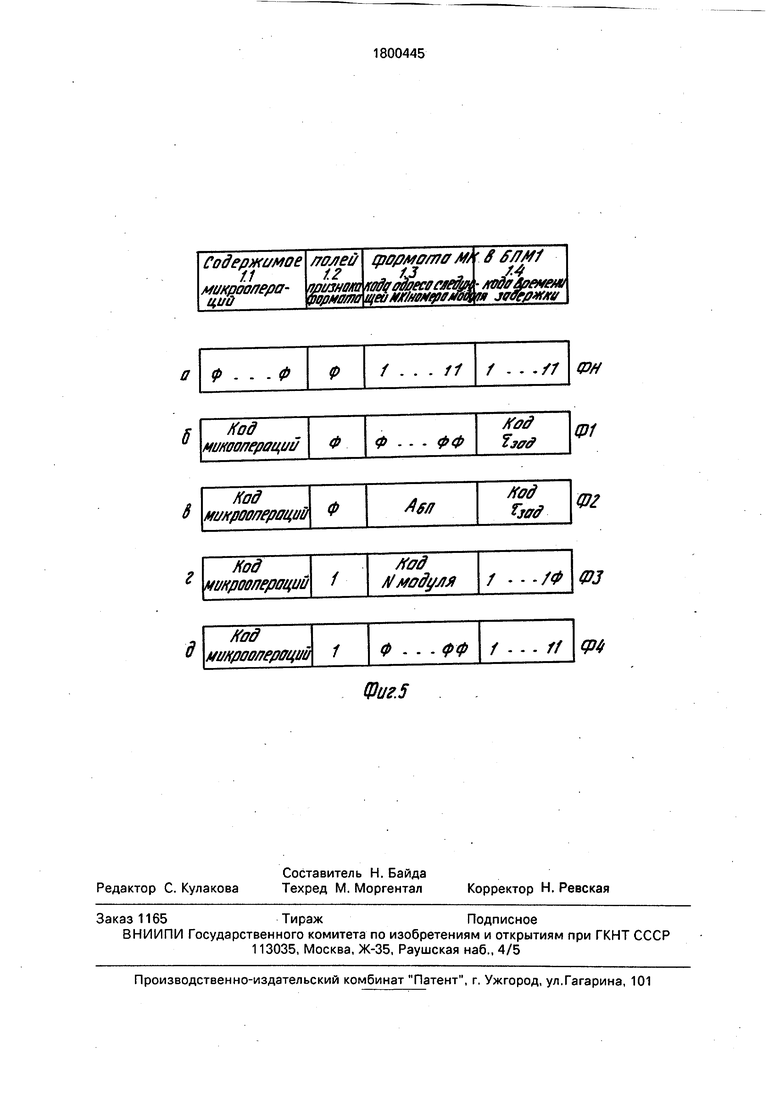

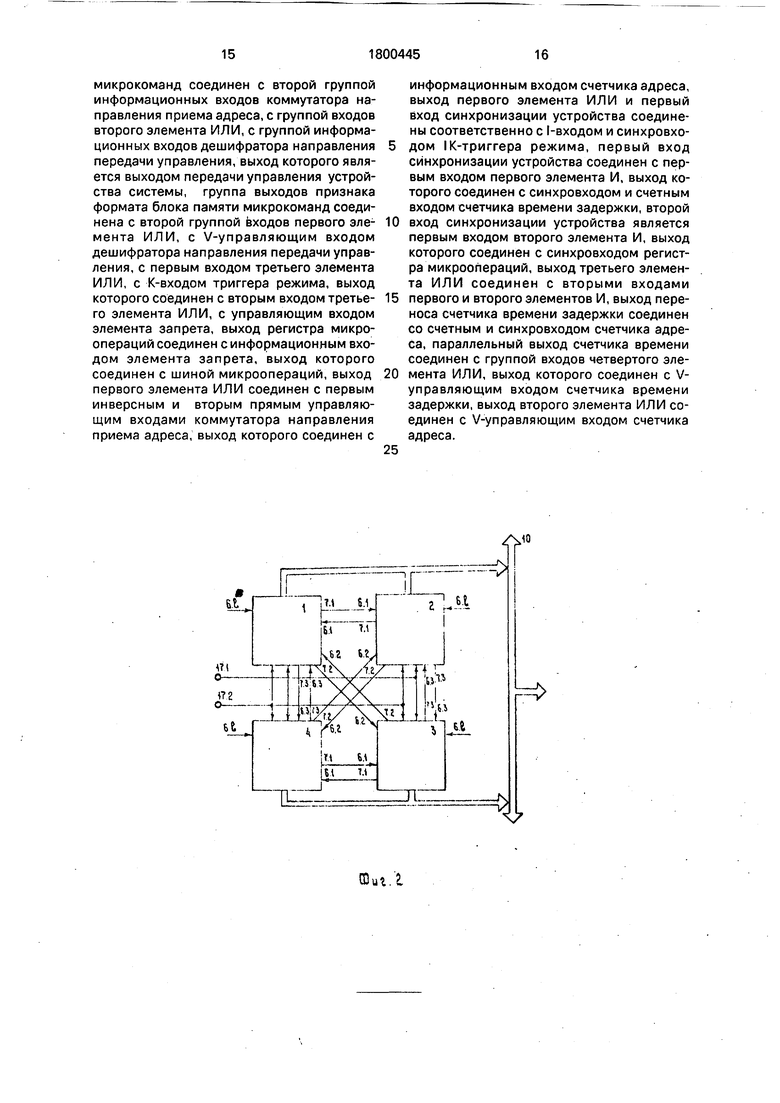

На фиг. 1 показана функциональная схема модульного устройства для программного управления (МУПУ); на фиг.2 - структурная схема включения МУПУ в распределенную управляющую систему, объединенную по принципу каждый с каждым ; на фиг.З - алгоритм работы МУПУ;. на фиг;4 - временная диаграмма работы МУПУ; на

фиг. 5 а,б,в,г,д - различные форматы микрокоманд: ФИ-формат исходной (нулевой) МК, Ф1 формат МК с естественным формированием адреса следующей МК, М2 - формат МК с адресом безусловного перехода к

следующей МК, ФЗ-форматМ К передачи управления другому модулю, Ф4-формат последней МК микропрограммы последнего модуля в цепи ее реализующей.

Устройство содержит (фиг.1): блок 1 памяти микрокоманд с выходами 1.1-микро- операций, 1.2 признака формата, 1.3 - задержки; 1,4 - адреса безусловного перехода (передачи управления); счетчик 2 адреса, регистр 3 микроопераций; коммутатор 4 направления приема адреса, триггер 5 режима, шифратор 6 направления приема управления, дешифратор 7 направления передачи управления, счетчик 8 времени задержки, элемент 9 запрета, шина 10

микроопераций, первый 11, второй 12, третий 13 и четвертый 14 элементы ИЛИ; первый 15 и второй 16 элементы И, входы 17.1 и 17.2 синхронизации; входы 6.1-6.1-1 инициализации данного модуля другими модулями системы; вход 6.I инициализации модуля от внешнего устройства управления; выходы 7,1-7.d передача управления другим модулям.

Нумерация на фиг.2-5 соответствует нумерации, принятой на фиг.1,

На фиг,1-5 использованы следующие обозначения: ROM - постоянное запоминающее устройство. КОП - код операции, TI, га - тактовые импульсы на входах синхронизации, МО - микрооперация, МК - микрокоманда, т, Гзад - код времени задержки, ЕП - естественный переход, БП безусловный переход, ПУ - передача управления, Ст т - счетчик времени задержки, Тфеж триггер режима, 8(р) - выход переноса Р счетчика 8.

Блок 1 памяти микрокоманд предназначен для хранения микрокоманд форматов,

показанных на фиг.5,а,б,в,г. Микрокоманда имеет четыре поля: 1.1 - кода микрооперации, 1,2 - признака формата, 1.3 - кода адреса следующей микрокоманды или номера модуля, принимающего управления;

Счетчик 2 адреса предназначен для приема, хранения и выдачи адреса очередной микрокоманды в режиме записи парал- лельным кодом, а также увеличения текущего адреса на единицу в счетном режиме. Этим обеспечивается режим принудительной (безусловной) и естественной адресации. Смена состояний счетчика 2 происходит по заднему фронту сигнала переноса Р, поступающего на его счетный вход и вход синхронизации с выхода переноса счетчика 8. Режим работы счетчика 2 определяется состоянием сигнала на его управляющем входе, поступающем с выхода второго 12 элемента ИЛИ. При нулевом сигнале на управляющем входе счетчик 2 работает в режиме счета, в противном случае - в режиме записи параллельным кодом.

Регистр 3 микроопераций предназначен для приема, хранения и выдачи управляющих сигналов микроопераций в шину 10 микроопераций через элемент 9 запрета. Запись кода микроопераций в регистр 3 осуществляется по заднему фронту тактового импульса Тг, поступающему на его синхров- ход.

Коммутатор 4 предназначен для выбора направления приема адреса очередной МК. Первый инверсный и второй прямой управляющие входы коммутатора 4 объединены. На оба эти входа поступает один и тот же сигнал с выхода элемента ИЛИ 11. Когда этот управляющий сигнал нулевой - открыт первый информационный вход коммутатора 4, когда этот сигнал единичный - открыт второй информационный вход коммутатора 4.

IK-триггер 5 режима предназначен для управления режимами работы устройства. IK-триггер 5 переключается по заднему фронту тактовых импульсов г, поступающих на его синхровход. В единичное состо- яние триггер 5 переключается при единичном сигнале на своем l-входе, в нулевое - при единичном сигнале на К-входе. Едичное состояние триггера 5 соответствует рабочему режиму устройства, нулевое - режиму ожидания приема управления или исходному состоянию.

Шифратор 6 предназначен для кодирования направления приема управления в жесткий адрес начала микропрограммы. Шифратор 6 имеет 1-разрядный вход, число I разрядов которого определяется числом фрагментов различных микропрограмм, хранимых в БПМ1 рассматриваемого модульного устройства. На вход шифратора 6 может поступать только унитарный код, который затем кодируется обычным двоичным

кодом (как двоичное представление номера разряда входа шифратора, который находится в единичное состоянии).

Дешифратор 7 предназначен для определения направления передачи управления рассматриваемым модульным устройством другим модулям управляющей системы. Дешифратор 7 имеет d-разрядный

выход, число d разрядов которого определяется числом незаконченных фрагментов различных микропрограмм, хранимых в БМП1 модуля. На информационный входде- шифратора 7 поступает log2d -разрядный

код номера модуля, которому передается управление. Этот код представляет собой код номера1 разряда выхода дешифратора, на котором должен быть сформирован единичный сигнал передачи управления соответствующему модулю управляющей системы. Дешифратор 7 функционирует только при единичном сигнале признака МК передачи управления, который поступает на его управляющий, разрешающий работу

вход.

Счетчик 8 предназначен для записи кода времени задержки, поступающего на его информационный входе выхода 1,4 блока 1 памяти. От значения кода зависит режим

работы регистра. Если код задержки равен нулю (00..0), то на выходе четвертого 14 элемента ИЛИ устанавливает нулевой сигнал. Этим сигналом, поступающим на управляющий вход счетчика 8, последний устанавливается в режим записи параллельным кодом. Любые другие значения кода времени задержки формируют на выходе четвертого элемента ИЛИ единичный сигнал, который переводит счетчик 6 в режим счета.

На выходе переноса счетчика 8 образуется единичный сигнал после переполнения его содержимого, при этом сам счетчик обнуляется.

Запись кода задержки и увеличение содержимого счетчика 8 осуществляется по заднему фронту тактовых импульсов т , поступающих соответственно на синхро- и счетный входы счетчика 8.

Элемент 9 запрета предназначен для открытия и закрытия доступа к шине 10 микроопераций. При единичном сигнале на управляющем входе элемента 9 запрета код микрооперации поступает с выхода регистpa 3MO на шину 10МО.

Шина 10 микроопераций (ШМО) передает управляющие сигналы МО, формируемые любым модулем управляющей системы, на вход операционного блока.

Первый 11 элемент ИЛИ управляет коммутатором 4, установкой триггера 5 режима в единичное состояние.

Второй 12 элемент ИЛИ управляет режимом работы счетчика 2. Так, при появлении на входе второго 12 элемента ИЛИ не нулевого кода адреса следующей МК единичный сигнал с его выхода устанавливает счетчик 2 в режим параллельной записи. Нулевой код на входе второго 12 элемент ИЛИ формирует сигнал низкого уровня и счетчик 2 переключается в режим счета.

Третий 13 элемент ИЛИ предназначен для открытия входов синхронизации устройства по одному из двух возможных сигналов, поступающих на его вход.

Четвертый 14 элемент ИЛИ управляет режимом работы счетчика 8.

Первый 15 и второй 16 элементы И разрешают поступление в устройство двух серий тактовых импульсов соответственно П и Г2 .

Рассмотрим работу устройства для программного управления.

В исходном состоянии блок памяти микрокоманд 1 содержит коды микрокоманд, реализующих заданные алгоритмы управления. Счетчик 2 адреса находится в нулевом состоянии, что обеспечивает в момент включения модуля обращение к нулевой ячейке блока памяти. В нулевой ячейке блока памяти записан код ФН начала микропрограммы. (Он имеет вид, показанный н.а фиг.5,а). Поля адреса 1.3 и времени задержки 1,4 имеют единичные коды, что обеспечивает режим записи параллельным кодом в счетчик 2 и выполнение первой микрокоманды микропрограммы без задержки. Счетчик 8 времени задержки имеет нулевое содержимое, что обеспечивает нулевой сигнал на его управляющем входе и нахождение счетчика 8 в режиме параллельной записи. Триггер 5 режима и регистр 3 микроопераций находятся в нулевом состоянии, элементы И15, 16 закрыты.

При поступлении сигнала запуска модуля от центрального устройства управления на соответствующий вход 6.1 шифратора 6 на его выходе формируется жесткий код первой МК. Этот код поступает на второй информационный вход коммутатора 4 и на вход первого 11 элемента ИЛИ, на выходе которого формируется единичный сигнал. Этот сигнал открывает второй информационный вход коммутатора 4 и поступает на 1-вход триггера 5 режима. По заднему фронту очередного тактового импульса т триггер 5 режима переходит в единичное состояние, открывая тем самым элемент 9

запрета и через элемент ИЛИ 13 элементы И15, 16.

Первый тактовый импульс тг пройдя через элемент И16 поступает на синхровход

регистра 3 микроопераций. По его заднему фронту произойдет запись в регистр 3 нулевого кода (см.формат МК ФН на фиг. 5а). Первый тактовый импульс т , прошедший через элемент И15 поступает на синхровход

0 счетчика 8. По его заднему фронту в счетчик 8 запишется единичный код с выхода 1.4 БПМ1. Элемент ИЛИ 14 сформирует единичный сигнал, по которому счетчик 8 переходит в счетный режим. По заднему фронту

5 следующего тактового импульса TI в регистр 3 снова перепишется нулевой код с выхода 1.1 БПМ1. Очередной тактовый импульс серии п , поступая на счетный вход счетчика 8, своим задним фронтом добавля0 ет единицу к содержимому счетчика 8. Поскольку в последнем находится код 11...1,то происходит переполнение, При этом счетчик 8 обнуляется, а на выходе переполнение образуется единичный импульс Р такой

5 же формы, что и т . Поскольку счетчик 2 находится в режиме параллельной записи, то код адреса первой МК с выхода шифратора 6 записывается в него задним фронтом импульса Р. Далее из блока 1 памяти из

0 указанного адреса выбирается первая микрокоманда микропрограммы управления.

При естественной или безусловной адресации с требуемой задержкой выбора следующей микрокоманды устройство

5 работает следующим образом. На выходе блока 1 памяти появляется микрокоманда, имеющая формат Ф1 или Ф1 (фиг.5 б,в),

Очередной тактовый импульс TI записывает в счетчик 8 код времени задержки

0 Тзад . При этом единичный сигнал с выхода четвертого 14 элемента ИЛИ переводит счетчик 8 в режим счета. Тактовый импульс Т2 записывает код микроопераций в регистр 3 и через открытый элемент 9 запрета МО

5 поступает в ШМ010. Начинается выполнение МО в операционном блоке. Последующие тактовые импульсы TI прибавляют к содержимому счетчика 8 единицы в младший разряд до его переполнения, а тг пере0 записывают код МО в регистр 3, после переполнения счетчика 8 происходит запись нового адреса в счетчик 2, как было описано выше. Задаваясь различными кодами времени задержки в поле 1,4 микроко5 манды, можно управлять временем выборки следующей МК. При необходимости выполнения МК без задержки в поле 1,4 микрокоманды указывается код 11,.,1, Естественная адресация обеспечивается нулевым кодом поля 1.3 микрокоманды. В противном случае реализуется переход по указанному в поле 1.3 адресу. Переход счетчика 2 из режима счета в режим параллельной записи и обратно осуществляется сигналом на его управляющем входе, поступающем с выхода второго 12 элемента ИЛИ. При передаче управления другим модулям по жесткому адресу на выходе блока 1 памяти передающего модуля появляется МК, имеющая формат ФЗ (фиг,5г). При этом содержимое поля 1.3 имеет смысл номера модуля, которому передается управление. Этот код поступает на вход дешифратора 7. Единичный сигнал с оыхода 1.2 признака БПМ1 разрешает работу дешифратора 7, через элемент ИЛИ 11 открывает второй информационный вход коммутатора 40 поступает на К-вход IK-триг- гера 5 режима. ПО заднему фронту очередного импульса Т2 в регистр 3 запишется последний микрооперационный код фраг- мента микропрограммы, реализуемой рассматриваемым модулем. Этот код поступает далее через элемент 9 в шину 10. Дешифратор 7 по коду номера модуля, которому нужно передать управление формирует на соответствующем разряде своего выхода единичный сигнал. Этот сигнал поступает на соответственный разряд входа шифратора 6 соответственно по модулю, которому передается управление. Шифратор 6 этого модуля формирует жесткий адрес первой МКсвоей работы. Элемент ИЛИ11 формирует единичный сигнал, который открывает второй информационный вход коммутатора 4 и поступает на 1-вход триггера 5 режима модуля принимающего управление.

По заднему фронту очередного импульса ri произойдет следующее.

1) В модуле передающем управление: К-триггер5 переходите нулевое состояние, в счетчик 8 записывается код (1... 10) на единицу меньший единичного кода, элемент 9 закрывается, модуль отключается от шины 10 МО, счетчик 8 переходит в режим счета.

2) В модуле, принимающем управле- ние: IK-триггер 5 переходит в единичное состояние, элемент 9 открывается дл я нулевого кода МО с выхода регистра 3, открываются для тактовых импульсов ri и Г2 элементы И15, 16.

Очередной импульс ti изменений не вызовет. В шину 10 МО по-прежнему будет поступать нулевой код с выхода регистра 3 модуля, принимающего управление.

По очередному импульсу TI : в счетчик 8 модуля принимающего управления записывается единичный код, счетчик 8 переходит в счетный режим, счетчик 8 модуля передающего управления увеличивает свое содержимое до единичного кода (1...11).

Очередной импульс Т2 опять не вызовет никаких изменений. По следующему импульсу ri и в модуле передающем и в модуле принимающем управление счетчики 8 переполнятся и сформируют сигналы Р. По заднему фронту сигнала Р в модуле принимающем управление в счетчик 2 запишется адрес первой МК с выхода шифратора 6. В модуле передающем управление по сигналу Р в счетчик 2 запишется нулевой адрес, т.к. в коммутаторе 4 этого модуля сигналом с выхода 1.2 БПМ1 открыт второй информационный входО на который с выхода шифратора 6 ничего не поступает. Итак, из БПМ1 в модуле передавшем управление считывается нулевая МК (формата ФН), а в модуле, принявшем управление - первая МК микропрограммы. Модуль, передавший управление находится в исходном состоянии, а модуль, принявший управление - в рабочем.

При окончании выполнения микропрограммы, последний из выполнявших ее модулей реализует МК формата Ф4 (фиг.5-д) выполняется аналогично описанному выполнению МК формата ФЗ. Отличие состоит лишь в том, что дешифратора 7 по нулевому коду на своем информационном входе не возбуждает ни один из разрядов своего выхода, соединенных с другими модулями управляющей системы,

Формула изобретения Устройство для программного управления, содержащее счетчик времени задержки, регистр микроопераций, блок памяти микрокоманд, счетчик адреса, причем выход счетчика адреса соединен с адресным входом блока памяти микрокоманд, а выходы микроопераций и времени задержки блока памяти соединены соответственно с информационным входом регистра микроопераций и счетчика времени задержки, о т- личающееся тем, что, с целью расширения области применения устройства и снижения объема оборудования при построении управляющих систем, устройство дополнительно содержит коммутатор направления приема адреса, триггер режима, шифратор направления приема управления, дешифратор направления передачи управления, элемент запрета, шину микроопераций, с первого по четвертый элементы ИЛИ, первый, второй элементы И, причем группа входов инициализации устройства является группой входов шифратора, выход которого соединен с первой группой входов первого элемента ИЛИ и с группой информационных входов коммутатора направления приема адреса, выход адреса-номера модуля блока памяти

микрокоманд соединен с второй группой информационных входов коммутатора направления приема адреса, с группой входов второго элемента ИЛИ, с группой информационных входов дешифратора направления передачи управления, выход которого является выходом передачи управления устройства системы, группа выходов признака формата блока памяти микрокоманд соединена с второй группой входов первого элемента ИЛИ, с V-управляющим входом дешифратора направления передачи управления, с первым входом третьего элемента ИЛИ, с К-входом триггера режима, выход которого соединен с вторым входом третьего элемента ИЛИ, с управляющим входом элемента запрета, выход регистра микроопераций соединен с информационным входом элемента запрета, выход которого соединен с шиной микроопераций, выход первого элемента ИЛИ соединен с первым инверсным и вторым прямым управляющим входами коммутатора направления приема адреса, выход которого соединен с

0

5

0

5

информационным входом счетчика адреса, выход первого элемента ИЛИ и первый вход синхронизации устройства соединены соответственно с 1-входом и синхровхо- дом IK-триггера режима, первый вход синхронизации устройства соединен с первым входом первого элемента И, выход которого соединен с синхровходом и счетным входом счетчика времени задержки, второй вход синхронизации устройства является первым входом второго элемента И, выход которого соединен с синхровходом регистра микроопераций, выход третьего элемента ИЛИ соединен с вторыми входами первого и второго элементов И, выход переноса счетчика времени задержки соединен со счетным и синхровходом счетчика адреса, параллельный выход счетчика времени соединен с группой входов четвертого элемента ИЛИ, выход которого соединен с V- управляющим входом счетчика времени задержки, выход второго элемента ИЛИ соединен с V-управляющим входом счетчика адреса.

Шиг/2,

Фиг.5

| Каган Б.М | |||

| Электронные вычислительные машины и системы | |||

| - М.: Энергоатомиз- дат, 1985, с.161, рис.7.1 | |||

| Устройство для программного управления | 1985 |

|

SU1252759A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Коул Б | |||

| Быстродействующие микропрограммные микроконтроллеры фирмы ALTERA | |||

| - Электроника, 1987, с.60, № 5, с | |||

| Машина для изготовления проволочных гвоздей | 1922 |

|

SU39A1 |

Авторы

Даты

1993-03-07—Публикация

1991-02-15—Подача