Лог.1 ,-аЗ

а

(J5

W

ОО

00 со оо

О)

ю

Изобретение относится к вычислительной технике и предназначено для контроля и локализации неисправностей в многовходовых логических блоках.

Целью изобретения является повышение быстродействия анализатора.

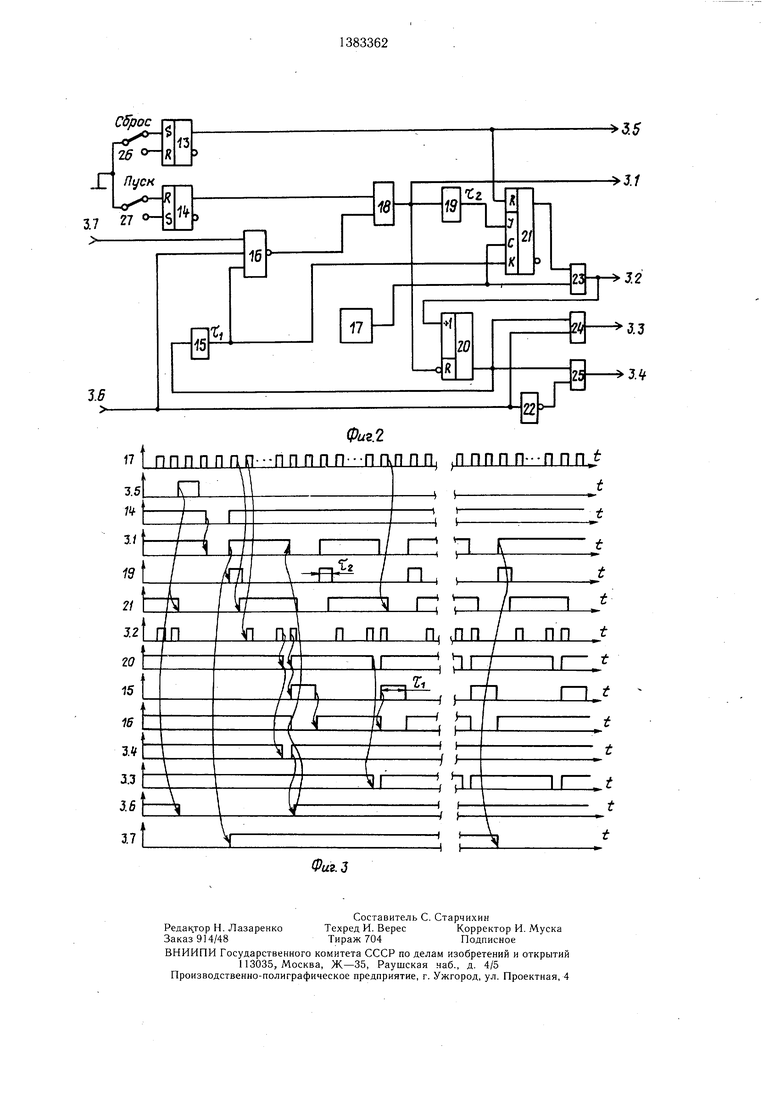

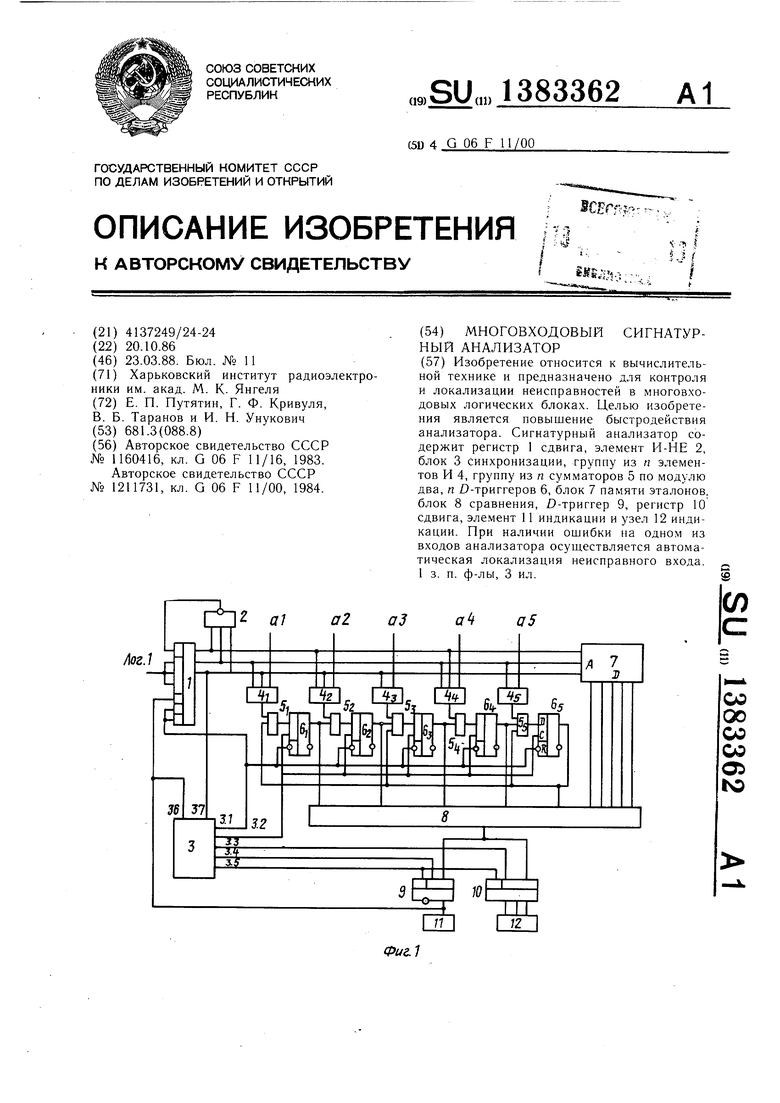

На фиг. 1 приведена функциональная схема многовходового сигнатурного анализатора (частный случай для количества входов и образующего полинома ф(х) х +Х + х + 1); на фиг. 2 - функциональная схе.ма блока синхронизации; на фиг. 3 - временная диаграмма функционирования анализатора.

Многовходовый сигнатурный анализатор (фиг. 1) содержит регистр 1 сдвига, элемент И-НЕ 2, блок 3 синхронизации, группу из п элементов И 4, группу из п сумматоров 5 по модулю два, п 1)-триггеров 6, блок 7 памяти эталонов, блок 8 сравнения, триггер 9 ошибки, регистр 10 сдвига, элемент 11 индикации, узел 12 индикации.

Блок синхронизации (фиг. 2) содержит два Л 5-триггера 13 и 14, элемент 15 задержки, элемент И-НЕ 16, генератор 17 тактовых импульсов, элемент ИЛИ 18, элемент 19 задержки, счетчик 20, //(-триггер 21, элемент НЕ 22, три элемента И,23-25, переключатели «Сброс 26 и «Пуск 27.

Многовходовый сигнатурный анализатор работает следующим образом.

По нажатии переключателя «Сброс 26 на выходе триггера 13 формируется импульс . положительной полярности, который устанавливает в нулевое состояние триггеры 21 и 9 и регистр 10. По нажатии переключателя «Пуск 27 на выходе триггера 14 формируется импульс отрицательной полярности, который проходит через элемент ИЛИ 18 и устанавливает в нулевое состояние счетчик 20 и триггеры 6. Этим же импульсом в единичное состояние устанавливаются все разряды регистра 1, что обеспечивает прохождение информации с входов сигнатурного анализатора ai-as через открытые элементы И 4 на входы сумматоров 5 по модулю два. По положительному фронту этого импульса элемент 19 задержки формирует импульс положительной полярности длительностью Т|, которая должна быть больше периода .следования тактовых импульсов, снимаемых с генератора 17 тактовых импульсов. Импульс элемента 19 поступает на /- вход //(-триггера 21 и по отрицательному фронту тактового импульса триггер 21 переходит в единичное состояние и открывает элемент И 23, через который тактовые импульсы начинают поступать на синхровходы / -триггеров 6 и счетный вход счетчика 20.

На входы сигнатурного анализатора поступают двоичные последовательности с выходов проверяемого устройства, которые с помощью многовходового сдвигового регистра с линейными обратными связями, выполненного на триггерах 6 и сумматорах 5 по модулю два, сворачиваются в сигнатуру. После того, как счетчик 20 заполняется (все тестовые последовательности поданы на проверяемое устройство), на его

выходе переполнения формируется импульс отрицательной полярности. Этот импульс через открытый элемент И 25 поступает на синхровход триггера 9 ошибки и осуш,еств- ляет запись в этот триггер результата сравQ нения полученной сигнатуры, находящейся в триггерах 6, и эталонной сигнатуры, хранящейся в блоке 7 памяти эталонов, по адресу, поступающему с регистра 1.

По положительному фронту импульса переполнения счетчика на выходе элемен5 та 15 формируется импульс положительной полярности длительностью Т2, которая должна быть больше периода тактовых импульсов. Этот импульс поступает на /(-вход триггера 21 и по отрицательному фронту тактового импульса //(-триггер 21 устанавливается в нулевое состояние.

При совпадении полученной и эталонной сигнатур триггер 9 остается в нулевом состоянии, элемент И-НЕ закрыт и процесс диагностики прекращается, проверяемое уст5 ройство исправно. Если же полученная и эталонная сигнатуры не совпали, триггер 9 ошибки устанавливается в единичное состояние и сигнатурный анализатор переводится в режим локализации неисправного выхода проверяемого устройства.

0 При этом открываются элемент 16 и элемент 24, а закрывается элемент 25, регистр 1 переводится в режим сдвига. Через открытый элемент 16 импульс, сформированный элементом 15, поступает через элемент ИЛИ 18 на установочные входы D-триггеров 6,

5 переводя их в нулевое состояние, и осуществляет сдвиг на один разряд содержимого регистра 1. Первый разряд регистра 1 при этом устанавливается в «О, а остальные - в «1. «О в первом разряде регистра 1 за0 крывает второй и четвертый элементы И 4. Таким образом, на сумматоры 5 подаются последовательности только со входов (21, аз и as. Импульсом, сформированным элементом 19, триггер 21 переводится в единичное состояние, и тем самым разрешается прохождение

5 тактовых импульсов через элемент 23 на синхровходы триггеров 6 и на счетный вход счетчика 20. Импульсом переполнения счетчика в регистр сдвига 10 заносится результат сравнения полученной и эталонной сигнатур, который определяет младший разряд двоич0 ного номера неисправного выхода. Аналогично происходит формирование второго и третьего разрядов номера неисправного выхода. При формировании второго разряда номера неисправного выхода во втором разс- ряде регистра 1 находится логический «О, а во всех остальных - логические «1. В этом случае открыты второй и третий элементы И 4 и, следовательно, на сумматоры по модулю два 5 поступают последовательности

с входов 02 и Оз. При формировании третьего разряда номера неисправного выхода после- довательно.сти поступают со входов 04 и as. В этом случае третий разряд регистра 1 находится в «нуле. После того, как номер неисправного выхода сформирован в регистре 10, уровень логического «О на старшем разряде регистра 1 закрывает элемент И- НЕ 16, процесс проверки заканчивается. Номер неисправного выхода отображается узлом 12 индикации.

Таким образом, при наличии ошибки на одном из входов анализатора осуществляется автоматическая локализация неисправного входа, что обеспечивает суммарное повышение быстродействия анализатора.

Формула изобретения

1. Многовходовый сигнатурный анализатор, содержащий блок синхронизации, п D-триггеров, где п - число входов анализатора, п сумматоров по модулю два, п элементов И и элемент индикации, причем первый выход блока синхронизации подключен к входам установки в «О О-триггеров, синхровходы которых объединены и подклю- чены к второму вьпсоду блока синхронизации выход /-го (, п) сумматора по модулю два соединен с информационным входом t -ro /З-триггера, выход /-го () О-триг- гера соединен с первым входом (/+1)-го сумматора по модулю два, второй вход /-го cyiyiMaTOpa по модулю два соединен с выходом /-ГО элемента И, выход п-го D-триггера соединен с первым входом первого сумматора по модулю два и с третьими входами сумматоров по модулю два в соответствии с ненулевыми коэффициентами образуюш,его полинома, отличающийся тем, что, с целью повышения быстродействия, он содержит блок памяти эталонов, блок сравнения, два регистра сдвига, триггер ошибки, элемент И-НЕ и узел индикации, причем первый вход /-ГО элемента И является /-м информационным входом анализатора, /-и разрядный выход первого регистра сдвига (, /С, К log2rt) соединен с /-м входом элемента И-НЕ, с /-М разрядным адресным входом блока памяти эталонов и с входами элемен- тов И, имеющими нуль в /-м разряде двоичной записи их номеров, 7(-й разрядный выход первого регистра сдвига соединен с входом останова блока синхронизации, выход элемента И-НЕ соединен с последовательным информационным входом первого регистра сдвига, группа параллельных информационных входов которого подключена к шине логической единицы, синхровход первого регистра сдвига соединен с первым выходом блока синхронизации, вход управления режимом работы первого регистра сдвига со

,j

5

0

5 0 5 п 5 0

5

единен с входом задания режима блока синхронизации, выходом триггера ошибки и входом элемента индикации, первая и вторая группы входов блока сравнения соединены соответственно с выходами О-триггеров и выходами блока памяти эталонов, выход блока сравнения соединен с информационным входом триггера ошибки и последовательным информационным входом второго регистра сдвига, синхровходы второго регистра сдвига и триггера ошибки подключены соответственно к третьему и четвертому выходам блока синхронизации, пятый выход которого соединен с входами установки в «О триггера ошибки и второго регистра сдвига, группа выходов которого соединена с группой входов узла индикации.

2. Анализатор по п. 1, отличающийся тем, что блок синхронизации содержит генератор тактовых импульсов, два 5-триггера, //(-триггер, счетчик, два элемента задержки, элемент И-НЕ, элемент ИЛИ, три элемента И, элемент НЕ и переключатели «Сброс и «Пуск, подвижные контакты которых соединены с шиной нулевого потенциала, размыкающий и замыкающий контакты переключателя «Сброс подключены соответственно к нулевому и единичному входам первого / 5-триггера, размыкающий и замыкающий контакты переключателя «Пуск подключены соответственно к единичному и нулевому входам второго / 5-триггера, выход первого / 5-триггера подключен к -входу //(-триггера и является пятым выходом блока, выход второго / 5-триггера соединен с первым входом элемента ИЛИ, выход которого соединен с входом сброса счетчика, входом второго элемента задержки и являются первым выходом блока, вход останова блока подключен к первому входу элемента И-НЕ, второй вход которого соединен с вторым входом второго элемента И, входом элемента НЕ и является входом задания режима блока, третий вход элемента И-НЕ соединен с выходом первого элемента задержки и /(-входом //(-триггера, выход элемента И-НЕ соединен с вторым входом элемента ИЛИ, выход второго элемента задержки соед инен с /-входом //(-триггера, С-вход которого соединен с выходом генератора тактовых импульсов и вторым входом первого элемента И, выход //(-триггера соединен с первым входом первого элемента И, выход которого соединен со счетным входом счетчика и является вторым выходом блока, выход переполнения счетчика связан с входом первого элемента задержки и первыми входами второго и третьего элементов И, выход элемента НЕ соединен с вторым входом третьего элемента И, выходы второго и третьего элементов И являются соответственно третьим и четвертым выходами блока.

J.3

3.4

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальный сигнатурный анализатор | 1990 |

|

SU1718220A1 |

| Многоканальный сигнатурный анализатор | 1984 |

|

SU1211731A1 |

| Сигнатурный анализатор | 1986 |

|

SU1388869A1 |

| Устройство для контроля цифровых узлов | 1983 |

|

SU1160417A1 |

| Устройство для контроля цифровых узлов | 1981 |

|

SU978154A1 |

| Сигнатурный анализатор | 1984 |

|

SU1242957A1 |

| Сигнатурный анализатор | 1986 |

|

SU1357961A1 |

| Сигнатурный анализатор | 1984 |

|

SU1262501A1 |

| Сигнатурный анализатор (его варианты) | 1984 |

|

SU1252784A1 |

| Устройство для контроля цифровых блоков | 1986 |

|

SU1411750A1 |

Изобретение относится к вычислительной технике и предназначено для контроля и локализации неисправностей в многовхо- довых логических блоках. Целью изобретения является повышение быстродействия анализатора. Сигнатурный анализатор содержит регистр 1 сдвига, элемент И-НЕ 2, блок 3 синхронизации, группу из п элементов И 4, группу из п сумматоров 5 по модулю два, п О-триггеров 6, блок 7 памяти эталонов, блок 8 сравнения, D-триггер 9, регистр 10 сдвига, элемент 11 индикации и узел 12 индикации. При наличии ошибки на одном из входов анализатора осуществляется автоматическая локализация неисправного входа. 1 3. п. ф-лы, 3 ил. S. S

17

143J 13

2i 3.2 20 15

16 3.V 3.3 З.б

Фи2.2

ПППП ппп---ппппп---ППуППП )ППППП---ППП,

| Многоканальный сигнатурный анализатор | 1983 |

|

SU1160416A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Многоканальный сигнатурный анализатор | 1984 |

|

SU1211731A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-03-23—Публикация

1986-10-20—Подача