Изобретение относится к области автоматического контроля и Может быть ионользовано в автоматических системах управления производством, характеризующимся дискретным протеканием процессов.

Известны устройства анализа импульсных последовательностей, содержащие триггер, на устаяовочные входы которого подаются импульсные Последовательности, схемы совладения и счетчик.

Однако этим устройствам свойственна ограниченность логических возможностей, что затрудняет решение технических задач, возникающих отри создании автоматических систем управления.

Расширение возможностей осуществляется за счет введения в устройство сравнения дополнительно двух триггеров запомиНания знака отклонения и двух схем совпадения, формирующих индивидуальные сигналы откло} ения при работе нескольких устройств на общий нако нитель. Возврат схемы В исходное состояние при восста-новлении запланироваиной очередности поступления импульсов после нарущения обеонечивается за счет введения в схему триггера-дискриминатора правильного чередования импульсов в сравниваемых последовательностях и схемы совпадения, формирующей сигнал возврата триггеров запоминания знака отклонения.

Предлагаемое устройство отличается от известных тем, что оно дополнительно содержит два трИГгера запоминания знака отклонения, триггер-дискриминатор правильного чередования ИМпульсов в сравниваемых 1последовательностях схемы совпадения, формирующие индивидуальные сигналы отклонения, и схему совпадения, формирующую Импульс возврата триггеров запоминания знака отклонения в исходное состояние после восстановления нарушенной очередности поступления импульсов, Цричем, единичный вход первого триггера запоминания знака отклонения соединен с единичным выходом триггера-дискриминатора, а

единичный вход второго триггера запоминания знака отклонения - с выходом первой схемы совпадения, входы третьей и четвертой схем совпадения подключены попарно к разноименным выходам триггеров запоминания знака

отклонения и к выходам триггера сравнения, единичный вход триггера дискриминатора по-дключен к единичному выходу триггера сравнения, а нулевой - к выходу второй схемы со В1падения; нулевой выход триггера дискриминатора подключен к потенциальным входам импульсно-потенциальных схем совпадения на входах триггеров запоминания знака отклонения, а импульсные входы этих схем совпадения подключены к выходу пятой схемы совпаным выходам триггера сравнения и триггеров заломинания знака отклонения, а «первая схема совнадения, подключенная -к нулевому входу и ВЫХОДУ ,ра срав|нения, своим третьим входом подключена к единичн-ному выходу триггера дискриминатора.

Это (позволяет накапливать информацию о количестве отклонений анализируемой последовательности от опорной, производить индивидуальный контроль наличия отклонения в текущий времени и исключить появление ложных сигналов в моменты подачи импульсных сигналов.

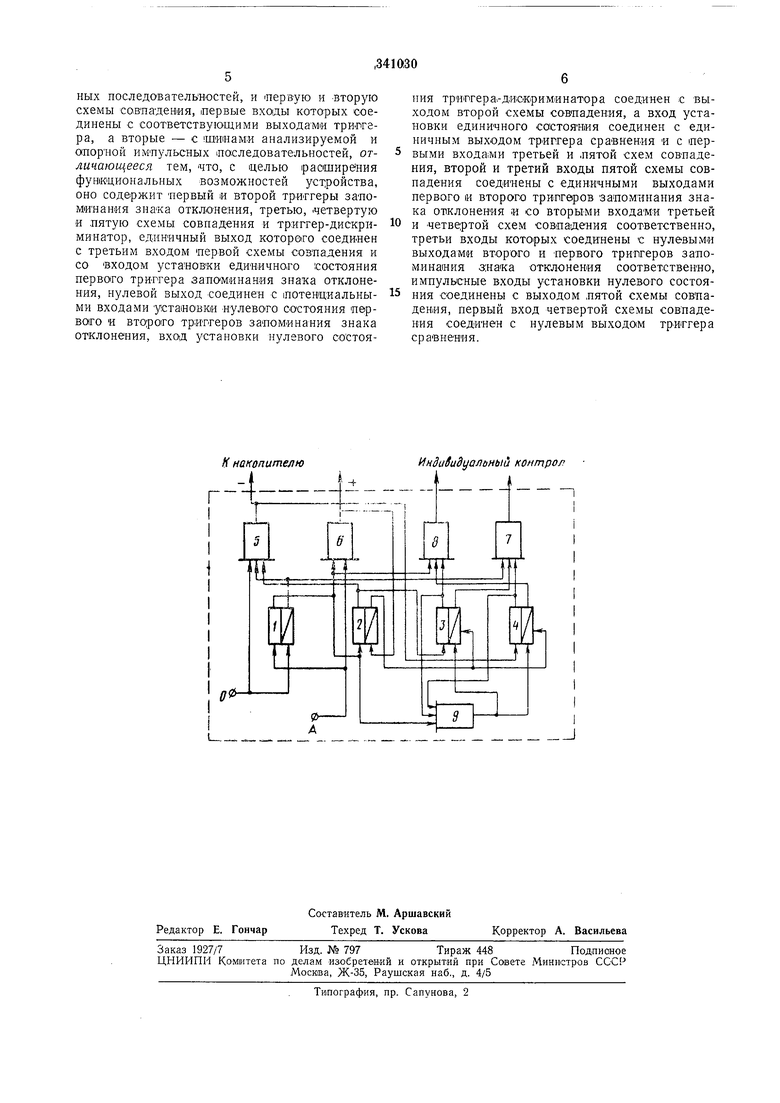

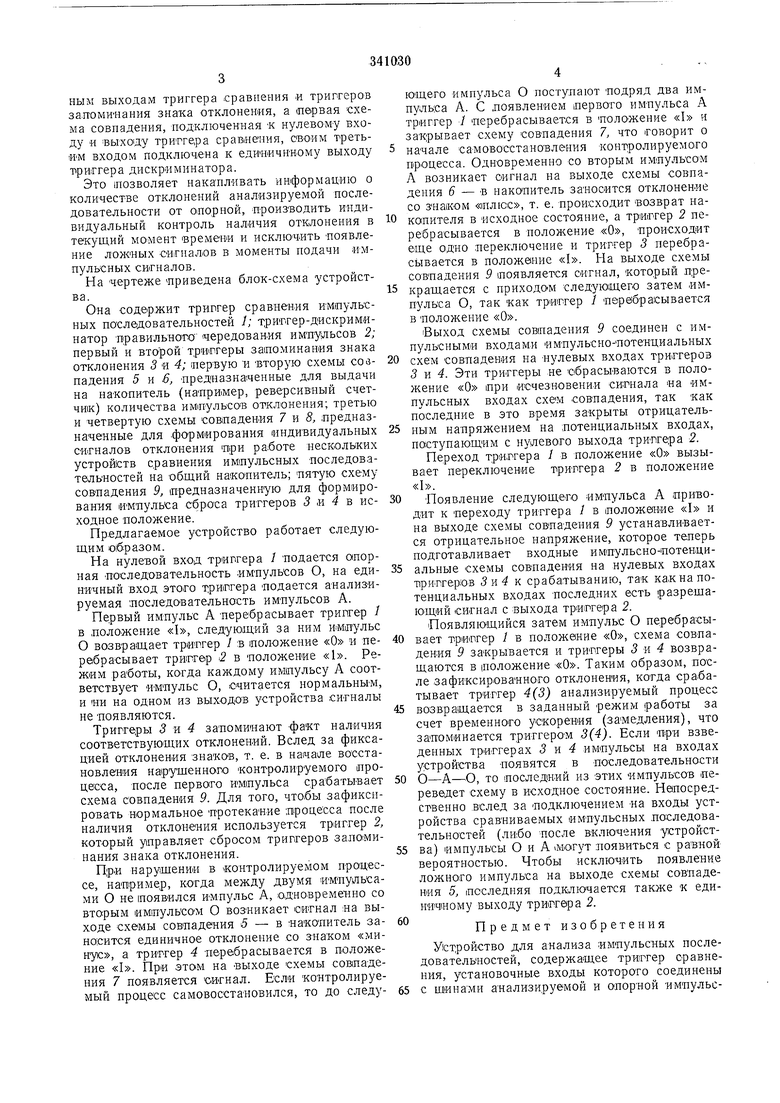

На чертеже «приведена блок-схема устройства.

Она содержит триггер сравнения импульсных последовательностей 1; триггер-дискриминатор вравильного чередования имтаульсов 2; первый и второй триггеры запоминания знака отклонения 3 и 4; иеръую и вторую схемы совпадения 5 и .6, предназначенные для выдачи на накопитель (например, реверсивный счетчик) количества им1пульсОВ отклонения; третью и четвертую схемы совпадения 7 и S, предназначенные для .формирования индивидуальных сигналов отклонения при ра:боте нескольких устройств сравнения импульсных последовательностей на общий накопитель; пятую схему совпадения 9, предназначенную для формирования Импульса сброса триггеров 3 я 4 в исходное положение.

Предлагаемое устройство работает следующим О1бразом.

На нулевой вход триггера / подается опорная последовательность импульсов О, на единичный вход этого т;рИ1Г1гера подается анализируемая яоследовательность импульсов А.

Первый импульс А перебрасывает трипгер / в положение «I, следующий за ним Импульс О возвращает трипгер 1 в положение «О и перебрасывает триггер 2 в положение «1. Режйм работы, когда каждому импульсу А соответствует импульс О, считается нормальным, и НИ на одном из выходов устройства сигналы не ПОЯВЛЯЮТСЯ.

Триггеры и 4 запоминают факт наличия соответствующих отклонений. Вслед за фиксацией отклонения знаков, т. е. в начале восстановления нарущенного контролируемого процесса, после первого ИМпульса срабатывает схема совпадения 9. Для того, чт01бы зафиксировать нормальное протекание процесса после наличия отклонения используется триггер 2, который управляет сбросом триггеров заломинания знака отклонения.

При нарушении в контролируемом процессе, например, когда между двумя импушьсами О не появился нмпульс А, одновременно со вторым импульсоМ О возникает сигнал на выходе схемы совпадения 5 - в накопитель заносится единичное отклонение со знаком «минус, а триггер 4 перебрасывается в положение «I. При этам на выходе схемы совпадения 7 появляется сигнал. Если контролируемый процесс самовосстановился, то до следующего импульса О поступают подряд два импульса А. С .появлением первого импульса А триггер 1 перебрасывается в положение «I и закрывает схему совпадения 7, что говорит о начале самовосстановления контролируемого процесса. Одновременно со вторым импульсом у возникает сигнал на выходе схемы совпадения 6 - в накопитель заносится отклонение со знаком «плюс, т. е. происходит возврат накопителя в исходное состояние, а триггер 2 перебрасывается в полон ение «О, происходит еще одно переключение и триггер 3 перебрасывается в положе1ние «I. На выходе схемы совпадения 9 появляется сигнал, который прекращается с приходоМ следующего затем импулвса О, так как триггер ) перебрасывается в положение «О.

Выход схемы совпадения 9 соединен с импульсными входами импульсно-потенциальных

схем совпадения на пулевых входах триггеров 3 ъ 4. Эти триггеры не сбрасываются в положение «О при исчезновении сигнала па импульсных входах схем совпадения, так как последние в это время закрыты отрицательным напряжением на потенциальных входах, поступающим с нулевого выхода триггера 2.

Переход три.ргера 1 в положение «О вызывает переключение триггера 2 в положение «I.

-Появление следующего импульса А приводит к переходу триггера / в положение «I и на выходе схемы совпадения 9 устанавливается отрицательное напряжение, которое теперь подготавливает входные импульсно-потенциальные схемы совпадения на нулевых входах Т1риггеров 5и4 к срабатыванию, так как на потенциальных входах последних есть разрешающий сигнал с выхода триггера 2. Появляющийся затем импульс О перебрасывает триггер / в положение «О, схема совпадения 9 закрывается и триггеры 5 и 4 возвращаются в положение «О. Таким образом, после зафиксированного отклонения, когда срабатывает триггер 4(3) анализируемый процесс

возвращается в заданный режим работы за счет временного ускорения (замедления), что запоминается триггером 3(4). Если при взведенных три1ггерах 5 и 4 импульсы на входах устройства появятся в последовательности

, то последний из этих импульсов переведет схему в исходное состояние. Непосредственно вслед за подключением на входы устройства сравниваемых импульсных последовательностей (либо после включения у1стройства) импульсы О и А iMoiryT появиться с равной вероятностью. Чтобы исключить появление ложного импульса на выходе схемы совпадения 5, последняя подключается также к единичному выходу три ггера 2.

г,,.

Предмет изобретения

ных последовательностей, и первую и Вторую схемы совпадевия, первые входы которых соединены с соответствующими выходами три.пгера, а вторые - с шстнами анализируемой и опорной имнульсных лоследовательностей, отличающееся тем, что, с целью расширения функциональных возможностей уст;ройства, оно содержит первый и второй триггеры запоминания знака отклонения, третью, Четвертую и лятую схемы совпадения и триггер-дискриминатор, единичный выход которого соединен с третьим входом первой схемы совпадения и со ВХОДОМ установки единичного состояния первого триггера запоминания знака отклонения, нулевой выход соединен с потенциальными входами установюи нулевого состояния первого и второго триггеров запоминания знака отклонения, вход установки нулевого состояния триргерагдискриминатора соединен с выходом второй схемы совпадения, а вход установки единичного состояния соединен с единичным выходом триггера сравнения и с иервыми входа;ми третьей и .пятой схем совпадения, второй и третий входы пятой схемы совпадения соединены с единичными выходами первого и второго три лгеров запоминания знака отклонения и со вторыми входами третьей

и четвертой схем совпадения соответственно, третьи входы которых соединены с нулевыми выходами второго и первого триггеров запоминания знака отклонения соответственно, импульсные входы установки нулевого состояПИЯ соединены с выходом пятой схемы совпадения, первый вход четвертой схемы совпадения соединен с нулевым выходам триггера сравнения.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для приема частотно-импульсной информации | 1982 |

|

SU1061169A1 |

| МНОГОКАНАЛЬНЫЙ ЦИФРОВОЙ ДИСКРИМИНАТОР | 1973 |

|

SU378859A1 |

| УСТРОЙСТВО для ИЗМЕРЕНИЯ ФУНКЦИИ РАСПРЕДЕЛЕНИЯ ВЕРОЯТНОСТЕЙ СЛУЧАЙНЫХ ПРОЦЕССОВ | 1969 |

|

SU249774A1 |

| МНОГОКАНАЛЬНЫЙ ИНФРАНИЖОЧАСТОТНЫЙ ЦИФРОВШ КОРРЕЛЯТОР | 1972 |

|

SU433486A1 |

| МНОГОЧАСТОТНЫЙ ДИСКРИМИНАТОР | 1973 |

|

SU379977A1 |

| ЦИФРОВОЙ АНАЛИЗАТОР ВРЕМЕИНЫХ ХАРАКТЕРИСТИК ТРАНЗИСТОРНЫХ СХЕМ | 1971 |

|

SU297011A1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ СКОРОСТИ ВРАЩЕНИЯ ОБЪЕКТА | 1972 |

|

SU412552A1 |

| Демодулятор фазоманипулированного сигнала | 1987 |

|

SU1536506A1 |

| Устройство для формирования сигнала разностной частоты импульсных последовательностей | 1981 |

|

SU1086552A1 |

| ЮЗНАЯ | 1973 |

|

SU370612A1 |

К накопителю

Индийидуалйный контрол

Авторы

Даты

1972-01-01—Публикация