1

Изобретение относится к области вычислтельной техники, а именно, к вычислителям статистических параметров случайных процессов.

Известные многоканальные цифровые кор- реляторы параллельно-последова1ельного действия, содержащие двухканальный преобразователь аналог-код, узел смещения, многокаскадный сдвиговый регистр.счетчйки делитель частоты, три схемы совпадения и два триггера, соединенные единичными выходами с первыми входами первой и третьей схем еовпаде №ия, кулевой выход втЬрого Tj rrtpflt хроме того, еовдинен е п§р8ММ вхевем €хемы €в§ ш/|@иня, i er§ (1ан11я {шй ехзд § йнф@|1М1ци§н11ым

выходом делителя частоты, выход второй схемы совпадения подсоединен к информационному входу делителя частоты, позволяют производить корреляционный анализ относительно высокочастотных процессов. Однако такие устройства используют сравнительно большое количество оборудования. В то же время для анализа внфранизкочастотных процессов можно значнтель

но сократить объем оборудования, необходнмый для построения коррелятора, что и является целью изобретения.

Пос1ашеШ1ая цель достигается тем, что выход синхронизации тфеобразователя соедннен со вторым входом первой схемы совпадения, выход которой подключен к вторым входам вторий и третьей схем совпадения, выход второй схемы совпадения соединен с входами опросов старших разрядов всех каскадов регистра сдвига, выход третьей схемы совпадения подкгаочен к входам, удвоения делителя частоты, к нулевому входу тороге трмггерй к к еинхроннаирующим ixoдам в@ех хвекаввв р§гивтр§в вввкгй, ккформв1ше№ые выщры sm ем§щея1 Я тамяе

ченй к бхёдвм ПврЬвЖ каскада рвривтра

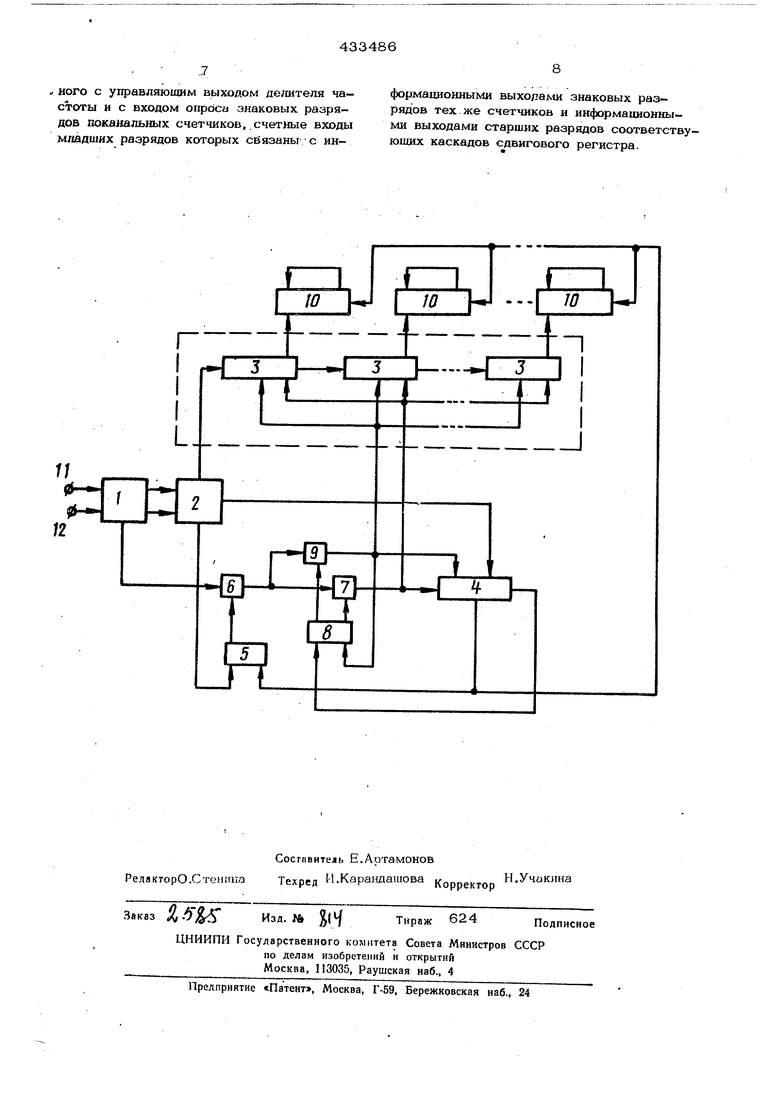

сдвига и установки коэффициента деления делителя соответственно, а управляющий выход соединен с единичным входом первого триггера, нулевым входом связанного с управляющим выходом делителя частоты и с входом опроса .знаковых разрядов поканальных счетчиков, счетные выходы младших разрядов которых связаны с информационными выходами знаковых разрядов тех же счетчиков и информационными выходами старших разрядов соотвотствуюнщх каскаНа чертеже приведена блок-схема предлагаемого устройства.

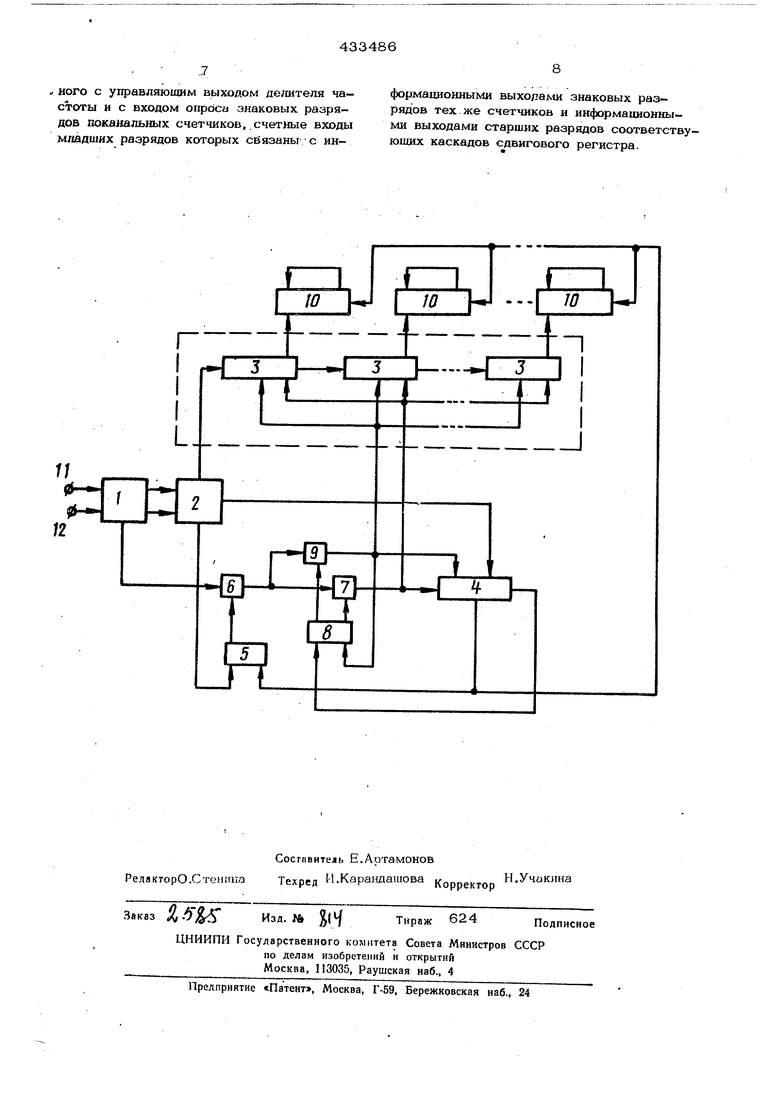

Она содержит двухканальный преобразователь 1 типа аналог -код, узел смещения 2, многокаскадный регистр сдвига 3, делитель 4 частоты, триггер 5, логические схемы совпадения 6 и 7, триггер 8, схему совпадения 9 и покана гьные с етчики 1О.

Преобразователь 1 имеет два информационных входа 11 и 12, два информахшонных выхода, подключенных к входам узла смешения 2, и шину генерации синхроимпульсов, связанную с импульсным входом схемы И 6.

Информационные выходы узла смешения 2 порознь подклк/чены соответственно к входным шинам младшего каскада Ц -каскадного регистра сдвига 3 и к входным шинам установки коэффициента деления делителя частоты 4, Управляюший выход узла 2 связан с единичным входом триггера 5, единичным потенциальным выходом соединенного с управляюшим входом схемы И 6, выход которой связан с импульсными входами схем И 7 и 9, управляющими входами подключенных к нулевому и единичному потенциальным выходам соответственно триггера 8.

Каждый каскад сдвиговогО ре1истра 3 состоит из Тп разрядов, причем выход старшего разряда предыдущего каскада связан со входом младшего разряда последующего каскада; tn-ый разряд каждого каскада снабжен выходной схемой И (на че1)тоже она не показана), упраБляю1Ш1М входом связанную с единичным потенциат ным выходом W -го разряда, а им- пул1язные входы схем И всех каскадов подключены к информационно|.1у входу де;штеля частоты 4 и к выходу схемы И 7. Сдвиговая шина регистра сдвига 3 подключена к выходу схемы И 9, нулевому входу триггера 8 и к входу удвоения коэ фщиеита деле1шя делителя частоты 4, а в(11ход по.следнего соединен с единичным входом триггера 8.

Каждый поканальный (2т )-разрядный счетчик снабжен трш-гером знака, нулевым потенциальным выходом подклоченным к управляющему входу cxeMiji И (на чертеже она не показана), выходом связанную параллельно с выходов вентиля соответствующего каскада сдвигового регистра 3, с выходом младшего разряда того же счетчика 10- Опросные входы знаковых схем И всех счетчиков объединены

нулевым входом триггера 5 и с управляющим выходом признака завершения Ш - кратного удвоения коэффициента деления делителя частоты 4.

Преобразователь 1 производит преобразование ординат знакопеременных сигналов

00,

X(t)H (t) в моменты времени t в соответствующ {е дискретные отсчеты X()H

-5CUT:)

Узел 2 осуществляет смещение дискрет Xllut) y(iu.T) на Бе;шчину N,, с пвследуюншм делением смешенных дискрет xCt.ut)H- Nj,и у(1дг)+М(,„ на два.

. Результаты деления Г ( KNcH-j „

rv/LuT1+-N т

1 1 . перезаписываются соответственно в младший каскаде сдвигового регисгра 3 и в делитель частоты 4. 2т ста14ших и знаковый разряды счетчика К -го канала отведены под целую и знаковую части корреляционного момента о СКд1)

5Ху

а t младших разрядов - под дробную часть указанного числа.

Цепи начальных установок с целью упрощения на чертеже не отражены.

0В исходном положении триггеры 5 и 8

находятся в положении нуля, схемы И 6 и 9 закрыты, а схема И 7 открыта. В каждом из счетчиков зафиксирован инверсный

оJ

КОД числа N{N-N Т, авих 5-СМ см -i I

знаковых разрядах - код единицы. Знаковые схемы И счетчиков Ю по управляюшим входам закрыты.

Анализ осуществляется в течение N 0 циклов. Каждый цикл включает tn +2 этапа.

На первом этапе каждого цикла производится преобразова1гае ординат исследуемых сигналов в дискретные отсчеты.

Второй этап включает процедуру смешения дискретных отсчетов на величину N

см

с последующим делением Смещенных дискрет на два и размещением результатов деления соответственно в младшем каска0 де сдвигового регистра 3 и в делителе частоты 4.

Последующие П этапов отводятся на операцию умножения, которая распадается

5 на Ш частичных умножений. Процесс умножения совмещается с процедурой сдвига информации в сдвиговом регистре 3. Поэтому после завершения умножения информация оказывается перезаписанной из каж0 дого предыдущего каскада в последующий. 5433 MjjaflmHft же каскад освобождается джг . приема очередной дискреть. Процедура улшожения начииает ся по isctманде, выраба ьтабмой на управляющем выходе узла смещейия 2 лосяе завершения перезаписи информации в младший каскад сдвигового регистра Зин делитель частоты 4. При этом схема И 6 открывается по управляющему входу, в результате чего синхроимпульсы через схемы И 6 и 7 поступают на вход делителя частоты 4 в количестве, равном величине установленного коэффициента деления. Одновременно с этим осуществляется и соответствующее указанному количеству число огфосов старщих разрядов всех каскадов сдвигового регистра 3. На информационных выходах последних формируются пакеты импульсов, с чисЖ)м импульсов последовательности, равным коэффициенту деления, только в тех каскадах, старщие разряды которых находили единичном положении. Указанное число икьпульсов поступает на счетный вход соответствующих счетчиков 1О, Частичное перемножение завершается с появлением выходного импульса делителя частоты 4, который перебрасывает триггер 8 в положение единицы. В результате схема И 7 закрывается, а И 9 открывается. Поэтому очередной импульс последовательности, пройдя через схему И 9, осуществляет сдвиг кодов в регистре сдвига 3 ни один разряд вправо, удваивает коэффициент деления в делителе частоты 4 и перебрасывает триггер 8 в положение нуля Схема И 7 открывается, а И 9 закрывается. На этом завершается первое частичное умножение и подготовка к очередному этапу. В последующем этапе опрос старших разрядов всех каскадов сдвигового регистра 3 осуществляется в удвоенном количест ве, а с завершением процедуры опросов производится очередной сдвиг дискретных отсчетов на один разряд, Процесс умножения прекращается росле Ш -кратного удвоения коэффициента деления. При этом делитель частоты 4 сбрасывает на ну.ль соэффициент деления и формирует на управляющем выходе сигнал, перебрасывающий триггер 5 в положение нуля. В результате дальнейшее продвижени синхроимпульсов в делитель частоты 4 и опрос старщих разрядов всех каскадов сдв гового регистра 3 полностью прекращается Дискретные отсчеты в сдвиговом регистре 3 располагаются в соседних каскадах, а ;Младщий каскад полностью освобожден. Устройство подготовлено к очередному циклу анализа, который осуществляется в описанж й последовательности. В процессе завершения каждого цикла тфоводится опрос знаковых разрядов всех счетчиков при помоши управляющего сигнала делителя частоты 4. При этом в отдельно взятом счетчике возможна лишь однократная передача сигнала в младший его разряд. Это происходит в момент превыщения текущего результата статистического накрпле- кия парных хроизведений дискретных отсчётов, сдвинутых на заданный аргумент, над числом, заложенным в счетчике гфи его начальной установке. С набором статистической выборки N в старщих и I младших разрядах C4et чика К -го канала фиксируются коды соответственно целой и дробной частей искомой оценки К -ой ординаты корреляционной функции о ( дТ , а в знако 3вом разряде - знак получаемой оценки. Предмет обретения Многоканальный ин4ранизкочастотный цифровой коррелятор, содержащий двухканальный преобразователь аналог-код, узел смещения, многокаскадный сдвиговой регисгр, счетчики, делитель частоты, три схемы совпадения и два триггера, соединен- ные единичными выходами с первыми входами первой и третьей схем совпадения, нулевой выход второго триггера, кроме того, соединен с первым входом второй схемы совпадения, а его единичный вход - с информационным выходом делителя частоты, I выход второй схемы совпадения подсоединен к информационному входу делителя частоты, отл и чающийся тем, что, с целью сокращения количества оборудования, выход синхронизации преобразователя соединен со вторым входом первой схемы совпадения, выход которой подключен к вторым входам второй и третьей схем совпадения, выход второй схемы совпадения соединен с входами опросов, старших разрядов всех каскадов регистра сдвига, выход третьей схемы совпадения подключен к входам удвоения делите,гп1 частоты, к нулевому входу второго триггера и к сннхрониз1грующим входам всех каскадов регистров сдвига, информационные выходы узла смещения подключены ко входам первого каскада регистра сдвига и установки коэффициента деления делителя соответственно, а управляющий ьыход соединен с единичным входом Первого триггера, нулевым входом связан-

.7

ного с управляющим выходом де/штеля частоты и с входом опроса знаковых разрядов поканальных счетчиков, .счетные входы м/шдшях разрядов которых сйяэаны с ин8

формацнонными выходами знаковых разрядов тех же счетчиков и информационными выходами старш1гх разрядов соответствующих каскадов сдвигового регистра.

| название | год | авторы | номер документа |

|---|---|---|---|

| МНОГОКАНАЛЬНЫЙ ЦИФРОВОЙ КОРРЕЛЯТОР | 1972 |

|

SU337784A1 |

| ПРОЦЕССОР ДЛЯ ЦИФРОВОЙ СИСТЕМЫ ОБРАБОТКИ ДАННЫХ | 1971 |

|

SU305477A1 |

| Знаковый коррелометр | 1979 |

|

SU832564A1 |

| Устройство для коррекции шкалы времени | 1986 |

|

SU1365039A2 |

| АДАПТИВНОЕ ЦИФРОВОЕ ДИФФЕРЕНЦИРУЮЩЕЕ И ПРОГНОЗИРУЮЩЕЕ УСТРОЙСТВО | 2014 |

|

RU2535467C1 |

| ЦИФРОВОЕ ПРОГНОЗИРУЮЩЕЕ УСТРОЙСТВО | 2011 |

|

RU2446454C1 |

| Делитель частоты с переменным коэффициентом деления | 1988 |

|

SU1547057A2 |

| Устройство для умножения | 1976 |

|

SU651341A1 |

| АДАПТИВНОЕ ЦИФРОВОЕ ПРОГНОЗИРУЮЩЕЕ И ДИФФЕРЕНЦИРУЮЩЕЕ УСТРОЙСТВО | 2011 |

|

RU2475831C1 |

| Устройство для деления | 1983 |

|

SU1164698A1 |

Авторы

Даты

1974-06-25—Публикация

1972-04-12—Подача