1

Изобретение относится к области вычислительной техники и может применяться в качестве цифрового дискриминатора-анализатора распределения вероятностей значений случайных процессов.

Известный цифровой дискриминатор, содержащий я-каскадный регистр, каждый из каскадов которого представляет собой кольцевой сдвиговый регистр, поканальные блоки установки уровней анализа и ширины дифференциального окна, триггеры, логические элементы «И и переключатели, имеет сложную конструкцию.

Целью изобретения является упрощение дискриминатора. Это достигается тем, что в нем единичные потенциальные выходы каждого разряда кольцевого сдвигового регистра соединены с соответствующими неподвижными контактами групп переключателей блока установки уровней анализа и блока ширины дифференциального окна, подвижные контакты первой группы переключателей подключены ко входам соответствующих логических элементов «И всех каналов, а подвижные контакты второй группы переключателей -- ко входам других соответствующих элементов «И всех каналов, выходы элементов «И каждого канала соединены со входами соответствующих триггеров, единичные выходы которых соединены с управляющими

входами соответствующих выходных элементов «И, импульсные входы которых соединены с управляющим входом дискриминатора, а к информационному входу дискриминатора подключен вход сдвигового регистра

первого канала, выход регистра каждого

предыдущего канала соединен со входом

сдвигового регистра носледующего канала.

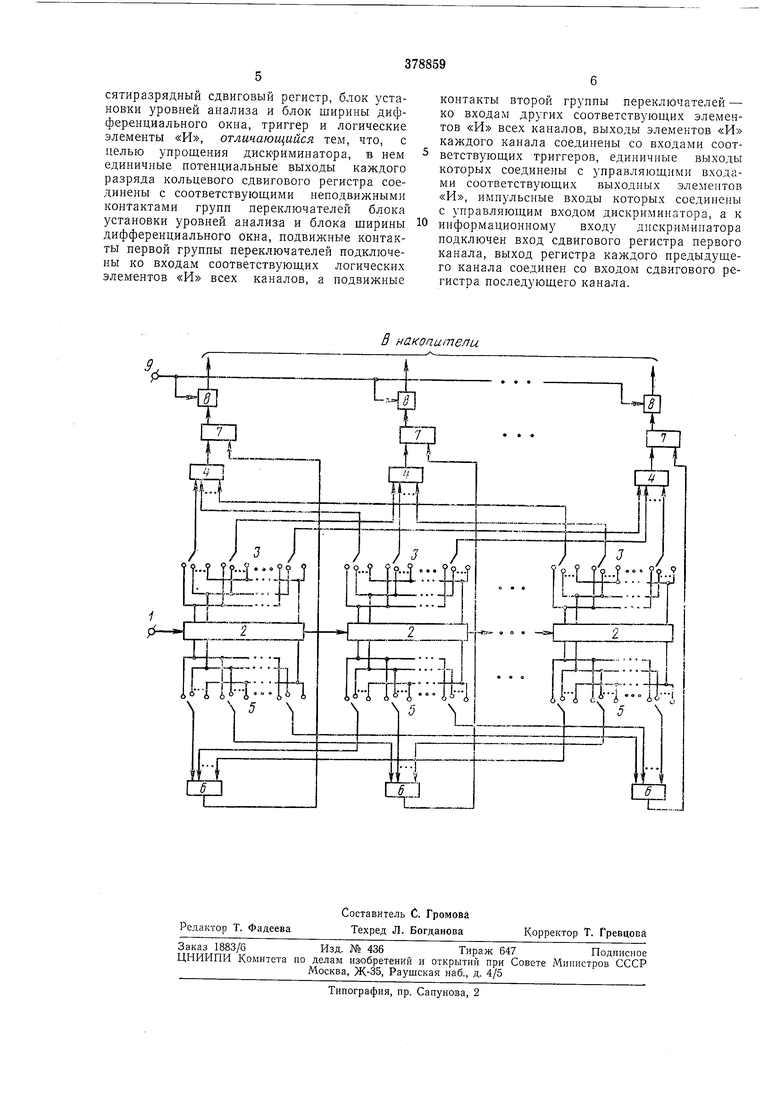

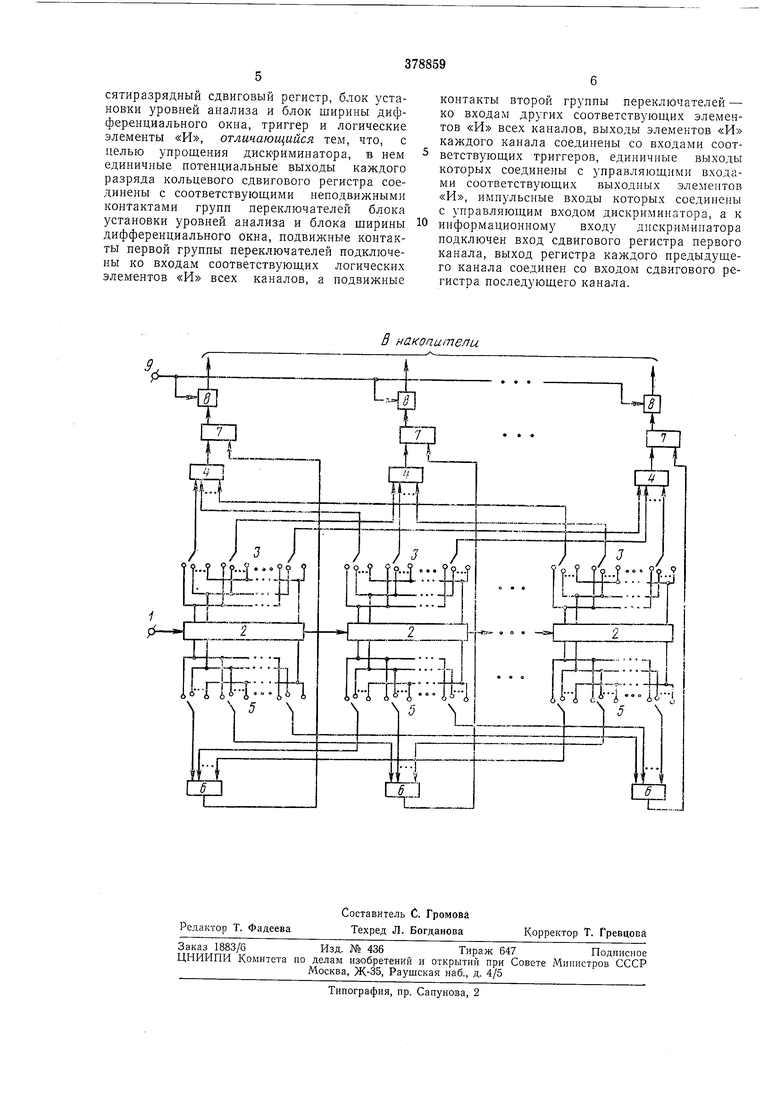

На чертеже изображена функциональная

блок-схема предлагаемого дискриминатора.

Он содержит информационный вход Л я-каскадный регистр (количество каскадов определяется разрядностью числа возможных анализируемых уровней), каждый каскад которого представляет собой кольцевой десятиразрядный сдвиговый регистр 2, первый покаскадный блок 3 установки уровней анализа, состоящий из т переключателей в каждом канале, т первых поканальных многовходовых логических элементов «И 4, поканальный блок 5 ширины дифференциального окна, состоящий в каждом канале из т переключателей, от вторых поканальных многовходовых логических элементов «И 5, от

поканальных триггеров 7, /п третьих логических элементов «И 8.

Вход / цифрового дискриминатора подключен к сдвиговой щине кольцевого десятиразрядного регистра первого канала. Выходы

регистров первого, второго и так далее

(п-1)-ого каскадов связаны соответственно со сдвиговыми шинами регистров второго, третьего и так далее каналов. Поразрядные единичные потенциальные выходы каждого из каналов связаны с соответствующими неподвижными контактами первой покаскадной группы блока 3 и второй покаскадной группы блока 5 переключателей. Подвижные контакты п первых переключателей первой группы переключателей блока 3 соединены с первым п входовым логическим элементом «И 4 первого канала, подвижные контакты п вторых переключателей первой группы переключателей блока 3 соединены с первым Бходовым логическим элементом «И 4 второго канала-и так далее, подвижные контакты п т-ых .переключателей первой группы переключателей блока 3 соединены с лервым п входовым логическим элементом «И 4 -т ого-канала--Аналогичным обр-азом осуществляется связь между подвижными контактами переключателей второй группы блока 5 и т поканальными вторыми п входовыми логическими элементами «И 6.

Выходы первых логических элементов «И 4 первого, второго и так далее каналов подсоединены соответственно к единичным пбканальных триггеров 7 первого, второго и так далее т-ого каналов. Выходы вторых логических элементов «И 6 первого, второго и так далее т-ого каналов подсоединены соответственно к нулевым входам триггеров 7 первого, второго и так далее п-ого каналов. Единичные выходы триггеров 7 соединены с управляющими входами третьих поканальных логических элементов «И 8, импульсные входы которых подсоединены к управляющей клеММе 9. Выходы третьих логических элементов «И соединены -с поканальными выходами дискримидатора, посту-пающими на :вход поканальных накопителей (на чертеже ие показаны).

Рассмотрим работу цифрового многоканального дискриминатора при определении значений функции распределения, точнее функции FI(X), где FI(X) -F(x). Предварительно переключатели второй группы первого канала выводятся в разомкнутое положение, что обеспечивает блокировку всех элементов «И 6, которая достигается отсутствием потенциала кода единицы на первых входах второй группы элементов «И 6. Па вход прибора подается напряжение реализации x(t) исследуемого случайного процесса. С каждой выборкой с выхода преобразователя аналог-код выдаются дискретные выборки. Первой выборке соответствует значение Xi(t) напряжения исследуемой реализации.

В результате аналого-цифрового преобразования напряжение Xi(t) преобразуется в число импульсов mi. Эти импульсы поступают на вход 1 цифрового дискриминатора. Перед поступлением первого и последующего пакетов импульсов триггеры всех разрядов

поканальных кольцевых регистров сдвига, кроме триггеров первых разрядов, установлены в нулевое положение. Триггеры же первых разрядов регистров каждого канала находятся в единичном положении. Поканальные триггеры 7 находятся в нулевом состоянии. До начала анализа с помощью первых покаскадных групп переключателей задаются для каждого канала выбранные уровни анализа, т. е. для второго канала используются вторые переключатели каскадов первой группы переключателей и так далее, для т-ого канала т-ые переключатели каналов первой группы переключателей. В конце выборки третьи логические элементы «П 8 опрашиваются импульсом конца пачки, поступающим с клеммы 9. Импульс конца пачки проходит только через те элементы «И 8, на потенциальные входы которых с соответствующих триггеров 7 поданы разрешающие потенциалы, что возможно только в том случае, если анализируемый уровень превысит данную выборку. Этот же импульс вновь возвращает триггеры 7 в нулевое состояние и устанавливает в нулевое состояние кольцевые регистры 2 (этому состоянию соответствует наличие единицы в первом разряде каждого кольцевого регистра сдвига). Так достигается очистка схемы - сброс на нуль. Аналогичным образом процессы повторяются при каждой выборке.

В конце времени анализа Т счетчик /-ого канала зафиксирует qi импульсов, соответствующих случаям превышения реализации анализируемого данным каналом f-oro уровня. Тогда FiT - , где Л - количество

выборок за время анализа Т. Определение плотности распределения сводится к подсчету количества ординат hi, зафиксированных /-ым накопителем в данном дифференциальном окне за время анализа Г, так как для i-oro

дифференциального окна co(Xj) - --4,

V

где AXi - ширина дифференциального окна. Так же, как и при определении интегрального закона распределения нижний уровень дифференциального окна для каждого канала задается с помощью первой грудпы переключателей блока 3 в числовой форме. Верхний же уровень дифференциального окна каждого канала устанавливается с помощью второй группы переключателей блока 5 тоже в числовой форме аналогичным образом.

Благодаря новым конструктивным связям и новому логическому построению процесса в схеме отсутствуют поканальные дискриминаторы, что позволяет принципиально упростить схему предлагаемого устройства.

Предмет изобретения

Многоканальный цифровой дискриминатор, содержащий в каждом канале кольцевой десятиразрядный сдвиговый регистр, блок установки уровней анализа и блок ширины дифференциального окна, триггер и логические элементы «И, отличающийся тем, что, с целью упрощения дискриминатора, в нем единичные потенциальные выходы каждого разряда кольцевого сдвигового регистра соединены с соответствующими неподвижными контактами групп переключателей блока установки уровней анализа и блока ширины дифференциального окна, подвижные контакты первой группы переключателей подключены ко входам соответствующих логических элементов «И всех каналов, а подвижные

контакты второй группы переключателей - ко входам других соответствующих элементов «И всех каналов, выходы элементов «И каждого канала соединены со входами соответствующих триггеров, единичные выходы которых соединены с управляющими входами соответствующих выходных элементов «И, импульсные входы которых соединены с управляющим входом дискриминатора, а к

информационному входу дискриминатора подключен вход сдвигового регистра первого канала, выход регистра каждого предыдущего канала соединен со входом сдвигового регистра последующего канала.

| название | год | авторы | номер документа |

|---|---|---|---|

| Амплитудный дифференциальный дискриминатор | 1978 |

|

SU765780A1 |

| Способ измерения плотности заполнения орбиты кольцевого ускорителя сгустками заряженных частиц и устройство для его осуществления | 1987 |

|

SU1614144A1 |

| Анализатор реовазосигналов для индикации наличия сосудов с нарушенной проходимостью | 1988 |

|

SU1602454A1 |

| Устройство для автоматического поиска дефектов в логических блоках | 1982 |

|

SU1108451A1 |

| Измерительная система с автоматическим контролем аналого-цифрового преобразования и блок задания нечувствительности | 1991 |

|

SU1837261A1 |

| СПОСОБ И УСТРОЙСТВО СЕЛЕКЦИИ СИГНАЛОВ НАДВОДНОЙ ЦЕЛИ В МОНОИМПУЛЬСНОЙ РЛС | 2004 |

|

RU2278397C2 |

| Преобразователь линейного позиционного кода в двоичный код | 1980 |

|

SU935944A1 |

| Многоканальное устройство для идентификации моделей | 1984 |

|

SU1238100A1 |

| Устройство для подключения абонентов к магистрали передачи данных | 1984 |

|

SU1254499A1 |

| Устройство для контроля логических блоков | 1979 |

|

SU875390A1 |

Даты

1973-01-01—Публикация