Изобретение относится к цифровой вычислительной технике и может быть использовано при построении МОЗУ, в которых одна из шин управления применяется для съема сигнала при считывании информации.

Известен ряд схем, обеснечнвающнх съем сигналов н уменьшение помех на входе усилителей считывания, появляющихся в момент прохождения разрядных токов в МОЗУ типов 2Д и ЗД и координатных в МОЗУ типа 2,5Д. Во всех известных схемах шины разделяются на две равные части и включаются в мостовую схему, в состав которой входит токовыравннвающий трансформатор. Кроме того, в некоторых схемах дополнительно иснользуются диоды, нозволяющие индуктивностям обмоток токовыравнивающего трансформатора быстро разряжаться.

Эти схемы сложны и требуют обеспечения двойной амплитуды тока. Некоторые схемы требуют специальные ключи для шунтирования трансформатора, которые при срабатывании могут создавать на диагонали моста (т. е. на входе усилителей считывания) помехи. Кроме того, имеется потеря сигнала за счет шунтирования входа усилителя считывания токозадаюгцими резисторами со сравнительно небольшими величинами сопротивлений, а также невозможность использования без дополнительных развязываюш,их элементов одного усилителя считывания для нескольких шин в одном разряде (например, н МОЗУ типа 2,5Д).

Для упрош,ения матрицы и уменьшения тока, потребляемого от источника питания в предлагаемом устройстве применяются два трансформатора, нмеюп-1,ие по две обмотки, из которых первичные подключены соотвегственно к первой и второй частям разрядной

(координатной) шины и соединены последовательно, а вторичные обмотки трансформаторов включены встречно и подключены к усилителю считывания. Генератор тока или электронный ключ с ограничительным резнстором включаются последовательно с пс))вичнымп обмотками трансформаторов.

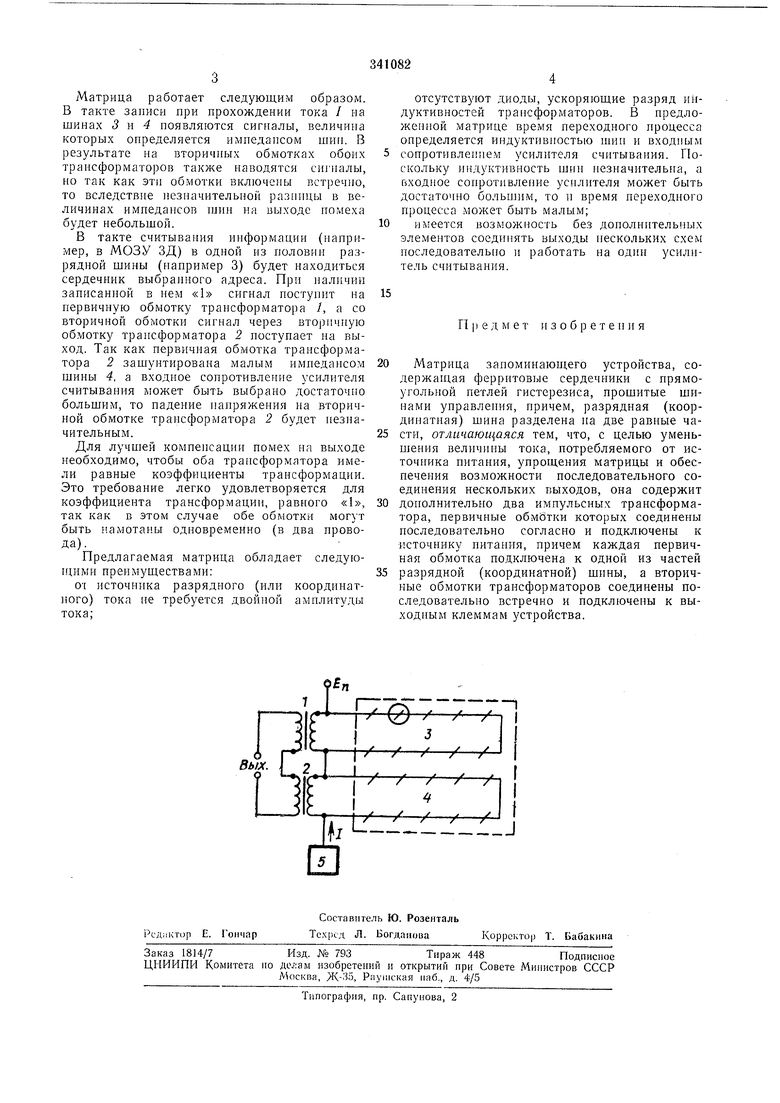

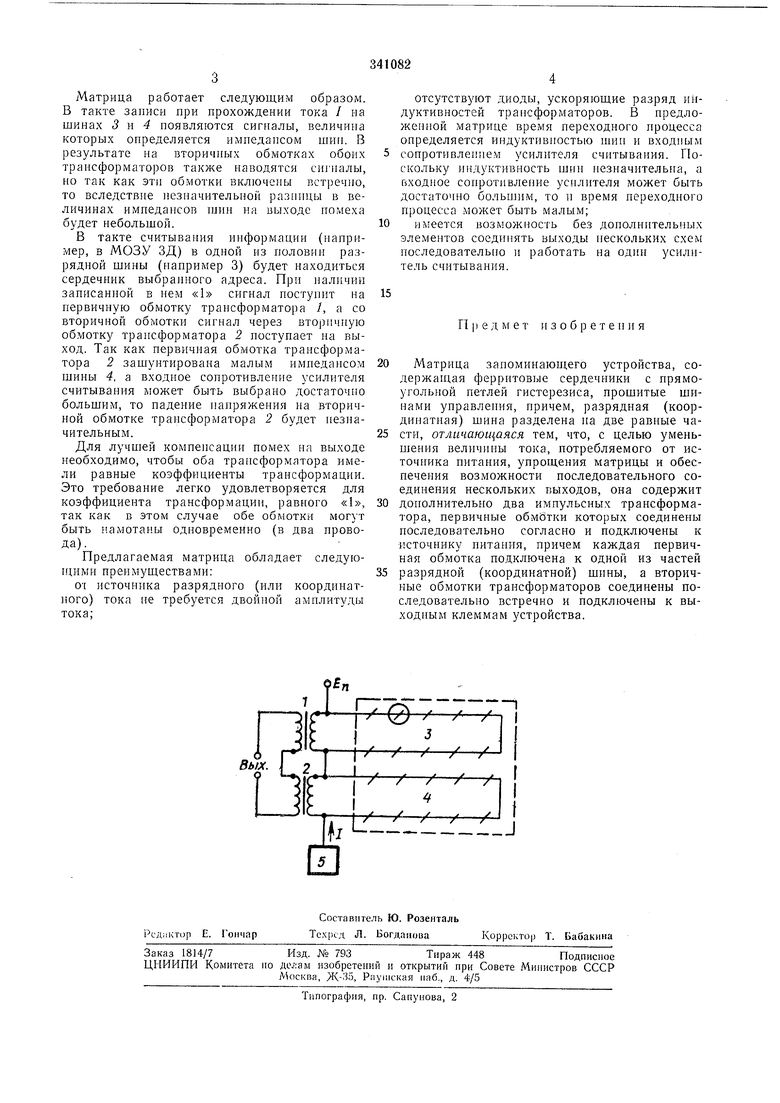

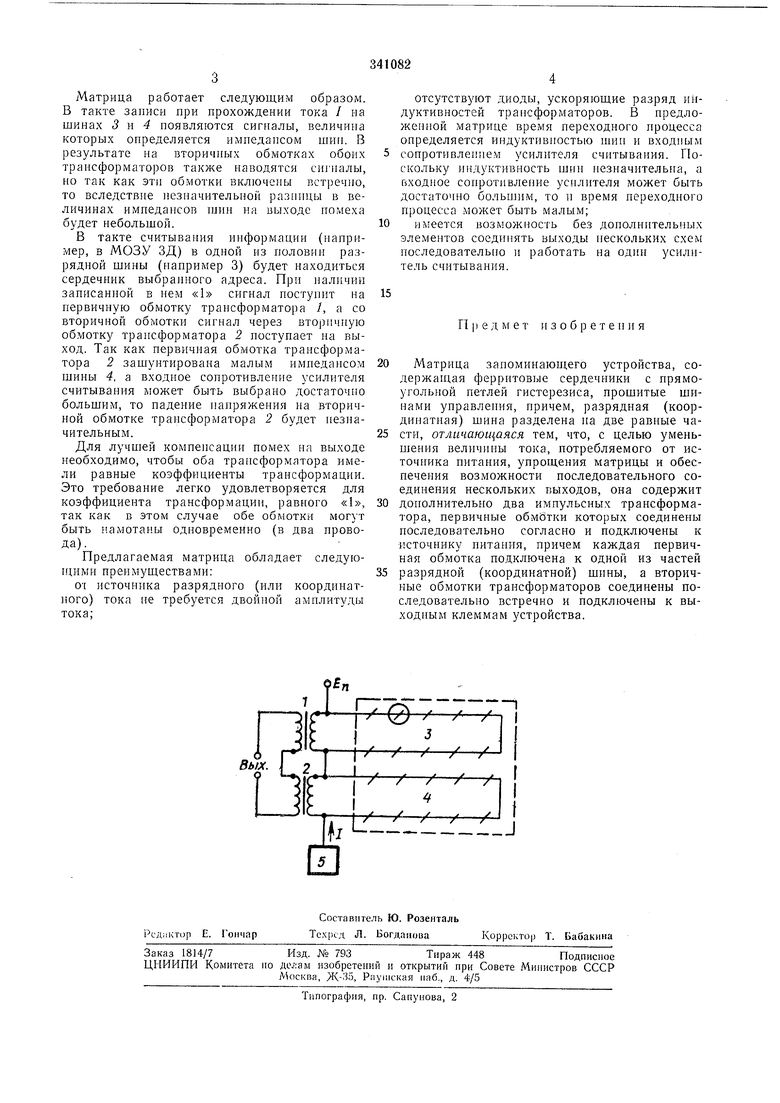

На чертеже изображена предлагаемая магрица запоминаюш.его устройства.

В состав матрицы входят два трансформатора У и 2, шины унравления и , а также источник питания 5. На представленном чертеже показаны две части шины: разрядной - для МОЗУ тинов 2Д и ЗД и координатной - для типа 2,5Д.

Первичпые обмотки обоих трансформаторов подключены соответственно к шинам 3 и 4, причем соединены между собой последовательно согласно и подключены к источннку питания 5. Вторичные обмотки трансформаМатрица работает следующим образом. В такте записи при прохождении тока / на шинах 5 и 4 появляются сигиалы, величина которых определяется нмнедаисом шин. В результате на вторичных обмотках обоих трансформаторов также наводятся си1налы, но так как эти обмотки включены встречно, то вследствие незначительной разницы в величинах имиедансов П1ин на выходе помеха будет небольшой.

В такте считывания ииформации (например, в МОЗУ ЗД) в одной из половнн разрядной шины (например 3) будет находиться сердечник выбранного адреса. При наличии записанной в нем «1 сигнал поступит на первичную обмотку трансформатора /, а со вторичной обмотки сигнал через вторичную обмотку трансформатора 2 поступает на выход. Так как первичная обмотка трансформатора 2 зашунтирована малым имиедаисом шины 4, а входное сопротивление усилителя считывания может быть выбрано достаточно большим, то падение паиряжеиия на вторичной обмотке трансформатора 2 будет незначительным.

Для лучшей компенсации помех на выходе необходимо, чтобы оба трансформатора имели равные коэффициенты трансформации. Это требование легко удовлетворяется для коэффициента трансформации, равного «I, так как в этом случае обе обмотки могут быть намотаны одновременно (в два провода).

Предлагаемая матрица обладает следую1ЦИМН преимуществами:

Ol источника разрядного (или координатного) тока не требуется двойной амплитуды тока;

отсутствуют диоды, ускоряющие разряд индуктивностей тра сформаторов. В предложенной матрице время нереходного процесса определяется индуктивностью шин и входным сонротивленнем усилителя считывания. Поскольку индуктивность шин иезиачительна, а входное сонротнвление усилителя может быть достаточно большим, то и время переходного процесса может быть малым;

имеется возможность без дополннтельных элементов соединять выходы нескольких схем последователь ю и работать на одни усилитель считывания.

Г11) е д мет изобретен и я

Матрица запоминающего устройства, содержащая ферритовые сердечники с прямоугольной петлей гистерезиса, прошитые шинами управлеиия, причем, разрядная (координатная) шина разделена на две равные части, отличающаяся, тем, что, с целью уменьшения величины тока, потребляемого от источника питания, упрощения матрицы и обеспечения возможности последовательного соединения нескольких выходов, она содержит

дополнительно два импульсных трансформатора, первичные обмйтки которых соединены носледовательно согласно и подключены к источнику нитания, причем каждая первичная обмотка подключена к одной из частей

разрядной (координатной) шины, а вторичные обмотки трансформаторов соединены последовательно встречно и подключены к выходным клеммам устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Накопитель магнитного оперативного запоминающего устройства | 1974 |

|

SU498647A1 |

| Устройство для контроля двухпроводных запоминающих матриц | 1978 |

|

SU752503A1 |

| ОПЕРАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1973 |

|

SU392551A1 |

| Клавиатура для ввода данных | 1973 |

|

SU495784A1 |

| Устройство для считывания графической информации | 1982 |

|

SU1080163A1 |

| Коммутатор считанных сигналов магнитных запоминающих устройств | 1986 |

|

SU1348905A1 |

| Дешифратор для запоминающего устройства | 1975 |

|

SU551639A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО ТИПА ЗД | 1971 |

|

SU427380A1 |

| Магнитное оперативное запоминающее устройство | 1969 |

|

SU466687A3 |

| ВЫЧИСЛИТЕЛЬНО-ЛОГИЧЕСКОЕ УСТРОЙСТВО | 1973 |

|

SU393741A1 |

Даты

1972-01-01—Публикация