1

Изобретение относится к области вычислительной техники и может быть использовано при построении устройств хранения дискретной информации.

Известен накопитель МОЗУ, содержащий блок запоминающих матриц на ферритовых сердечниках, прошитых координатными шинами j; и г/ и разрядными шинами записи и считывания, и диодные переключающие матрицы.

Недостатком известного накопителя является большое количество электронного оборудования и, как следствие, большая потребляемая MOui,HOCTb и низкая надежность работы.

Целью изобретения является уменьшение потребляемой мощности и повышение надежности работы накопителя.

Поставленная цель достигается путем того, что блок запоминающих матриц выполнен из m групп, состоящих из п запоминающих матриц. Координатные шины л; и i/ и одноименные разрядные шины записи всех групп запоминающих матриц соединены соответственно с выходами диодных переключающих матриц и У и выходами одноименных разрядных переключающих матриц, а одноименные разрядные шины считывания всех групп запоминающих матриц соединено последовательно.

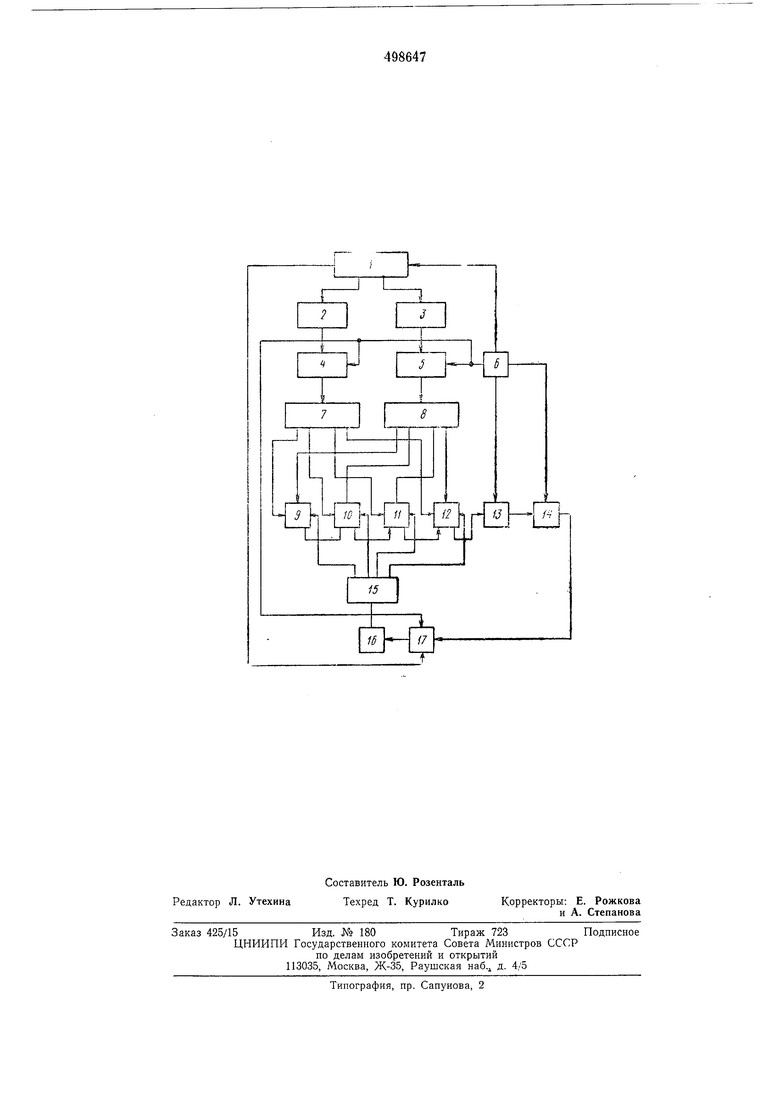

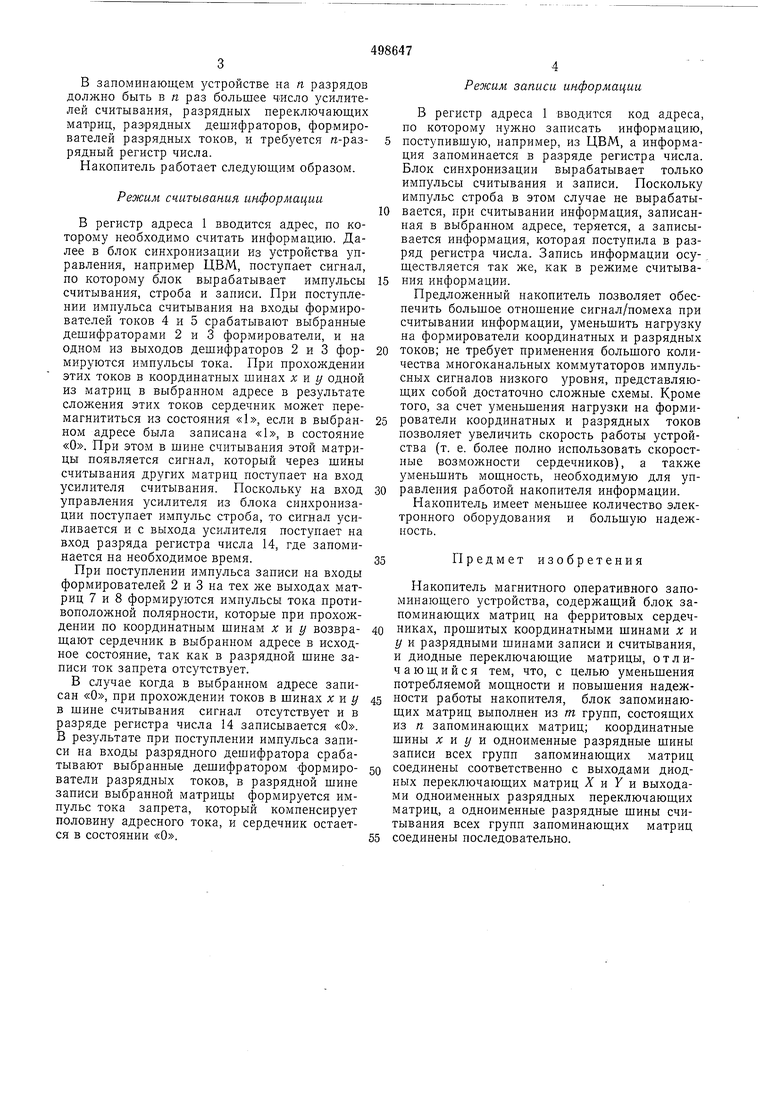

Па чертеже представлен один разряд МОЗУ с предложенным накопителем, где обозначены

регистр адреса 1; дещифраторы адреса по координатам X и у соответственно 2 и 3; формирователи координатных токов хну соответственно 4, 5; блок синхронизации 6; диодные переключающие матрицы X и Y соответственно 7 и 8; разрядные запоминающие матрицы 9- 12 накопителя; усилитель считывания 13; разряд регистра 14; разрядная переключающая матрица 15; формирователи разрядного тока

16 и разрядный дешифратор 17.

Выходы регистра адреса соединены с входами дешифраторов 2 и 3, выходы которых подключены к входам формирователей токов

4 и 5, выходами связанных с входами матриц 7 и 8. Выходы последних соединены с одноименными координатными шинамп матриц 9- 12. Разрядные шины считывания матриц соединены последовательно и подключены к

входу усилителя считывания 13, выход которого связан со входом разряда регистра 14. Разрядные шины записи матриц соединены с выходами матрицы 15, входы которой связаны с формирователями разрядных токов. Выход

разряда регистра числа 14 подключен ко входам дешифратора 17. Блок синхронизации 6 выдает управляющие сигналы в регистр адреса 1, дешифраторы 2, 3 и 17, а также на усилитель 13 и разряд регистра 14. В запоминающем устройстве на п разрядов должно быть в « раз большее число усилителей считывания, разрядных нереключающих матриц, разрядных дешифраторов, формирователей разрядных токов, и требуется гг-разрядный регистр числа. Наконитель работает следуюш,им образом. Режим считывания информации В регистр адреса 1 вводится адрес, по которому необходимо считать информацию. Далее в блок синхронизации из устройства управления, например ЦВМ, поступает сигнал, по которому блок вырабатывает импульсы считывания, строба и записи. При поступлении импульса считывания на входы формирователей токов 4 и 5 срабатывают выбранные дешифраторами 2 и 3 формирователи, и на одном из выходов дешифраторов 2 и 3 формируются импульсы тока. При прохождении этих токов в координатных шинах х и г/ одной из матриц в выбранном адресе в результате сложения этих токов сердечник может перемагнититься из состояния «1, если в выбранном адресе была записана «1, в состояние «О. При этом в шине считывания этой матрицы появляется сигнал, который через шины считывания других матриц поступает на вход усилителя считывания. Поскольку на вход управления усилителя из блока синхронизации поступает импульс строба, то сигнал усиливается и с выхода усилителя поступает на вход разряда регистра числа 14, где запоминается на необходимое время. При поступлении импульса записи на входы формирователей 2 и 3 на тех же выходах матриц 7 и 8 формируются импульсы тока противоположной полярности, которые при прохождении но координатным шинам л: и г/ возвращают сердечник в выбранном адресе в исходное состояние, так как в разрядной шине записи ток запрета отсутствует. В случае когда в выбранном адресе записан «О, при прохождении токов в шинах к w. у в шине считывания сигнал отсутствует и в разряде регистра числа 14 записывается «О. В результате при поступлении импульса записи на входы разрядного дешифратора срабатывают выбранные дешифратором формирователи разрядных токов, в разрядной шине записи выбранной матрицы формируется импульс тока запрета, который компенсирует половину адресного тока, и сердечник остается в состоянии «О. Режим записи информации В регистр адреса 1 вводится код адреса, по которому нужно записать информацию, поступившую, например, из ЦВМ, а информация запоминается в разряде регистра числа. Блок синхронизации вырабатывает только импульсы считывания и записи. Поскольку импульс строба в этом случае не вырабатывается, при считывании информация, записанная в выбранном адресе, теряется, а записывается информация, которая поступила в разряд регистра числа. Запись информации осуществляется так же, как в режиме считывания информации. Предложенный накопитель позволяет обеспечить большое отношение сигнал/помеха при считывании информации, уменьшить нагрузку на формирователи координатных и разрядных токов; не требует применения большого количества многоканальных коммутаторов импульсных сигналов низкого уровня, представляющих собой достаточно сложные схемы. Кроме того, за счет уменьшения нагрузки на формирователи координатных и разрядных токов позволяет увеличить скорость работы устройства (т. е. более нолно использовать скоростные возможности сердечников), а также уменьшить мощность, необходимую для управления работой накопителя информации. Накопитель имеет меньшее количество электронного оборудования и большую надежность. Предмет изобретения Накопитель магнитного оперативного запоминающего устройства, содержащий блок запоминающих матриц на ферритовых сердечниках, прошитых координатными шинами х и у и разрядными шинами записи и считывания, и диодные переключающие матрицы, отлиающийся тем, что, с целью уменьшения отребляемой мощности и повышения надежости работы накопителя, блок запоминаюих матриц выполнен из т групп, состоящих з п запоминающих матриц; координатные ины л; и i/ и одноименные разрядные шины аписи всех групп запоминающих матриц соединены соответственно с выходами диодых переключающих матриц X и У и выходаи одноименных разрядных переключающих атриц, а одноименные разрядные шины счиывания всех групп запоминающих матриц оединены последовательно.

| название | год | авторы | номер документа |

|---|---|---|---|

| Управляющий автомат цифрового устройства числового управления | 1972 |

|

SU507153A1 |

| СПОСОБ ЗАПИСИ ИНФОРМАЦИИ В ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО НА МАГНИТНЫХ СЕРДЕЧНИКАХ И ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО НА СЕРДЕЧНИКАХ | 1992 |

|

RU2101784C1 |

| Магнитное оперативное запоминающее устройство | 1981 |

|

SU980161A1 |

| Логическое запоминающее устройство | 1971 |

|

SU443411A1 |

| ВЫЧИСЛИТЕЛЬНО-ЛОГИЧЕСКОЕ УСТРОЙСТВО | 1973 |

|

SU393741A1 |

| Магнитное оперативное запоминаю-щЕЕ уСТРОйСТВО | 1979 |

|

SU841039A1 |

| Запоминающее устройство с исправлением ошибок при считывании информации | 1976 |

|

SU607281A1 |

| Запоминающее устройство системы 2д с неразрушающим считыванием информации на многоотверстных ферритовых элементах | 1977 |

|

SU693438A1 |

| Запоминающее устройство | 1974 |

|

SU536524A1 |

| Цифровое устройство числового программного управления | 1971 |

|

SU441858A1 |

Авторы

Даты

1976-01-05—Публикация

1974-06-12—Подача